Globalfoundries Alternative

FD-SOI: Preiswerte Alternative zu FinFET

Fortsetzung des Artikels von Teil 1

FD-SOI löst das PD-SOI-Problem

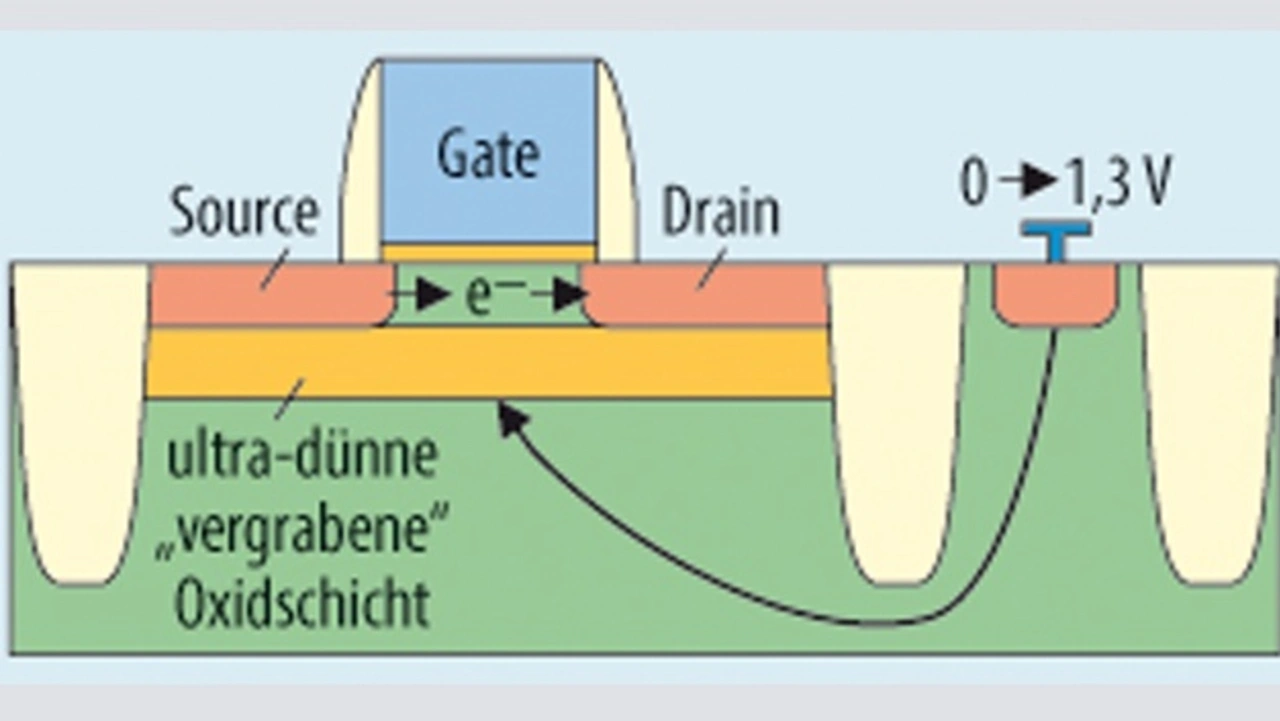

Die Oxid-Sperre isoliert den Transistor-Körper komplett vom Basis-Substrat. Dies reduziert die Source- und Drain-Kapazität dramatisch, so dass z. B. bei einer 180-nm-Fertigung die (aktive) Leistungsaufnahme bei gleicher Taktfrequenz um 50 % fiel oder die Taktfrequenz bei gleich bleibender Leistungsaufnahme um 25 % erhöht werden konnte (diese Werte reduzierten sich bei schrumpfenden Geometrien, bei 28 nm sind sie vernachlässigbar).

Jobangebote+ passend zum Thema

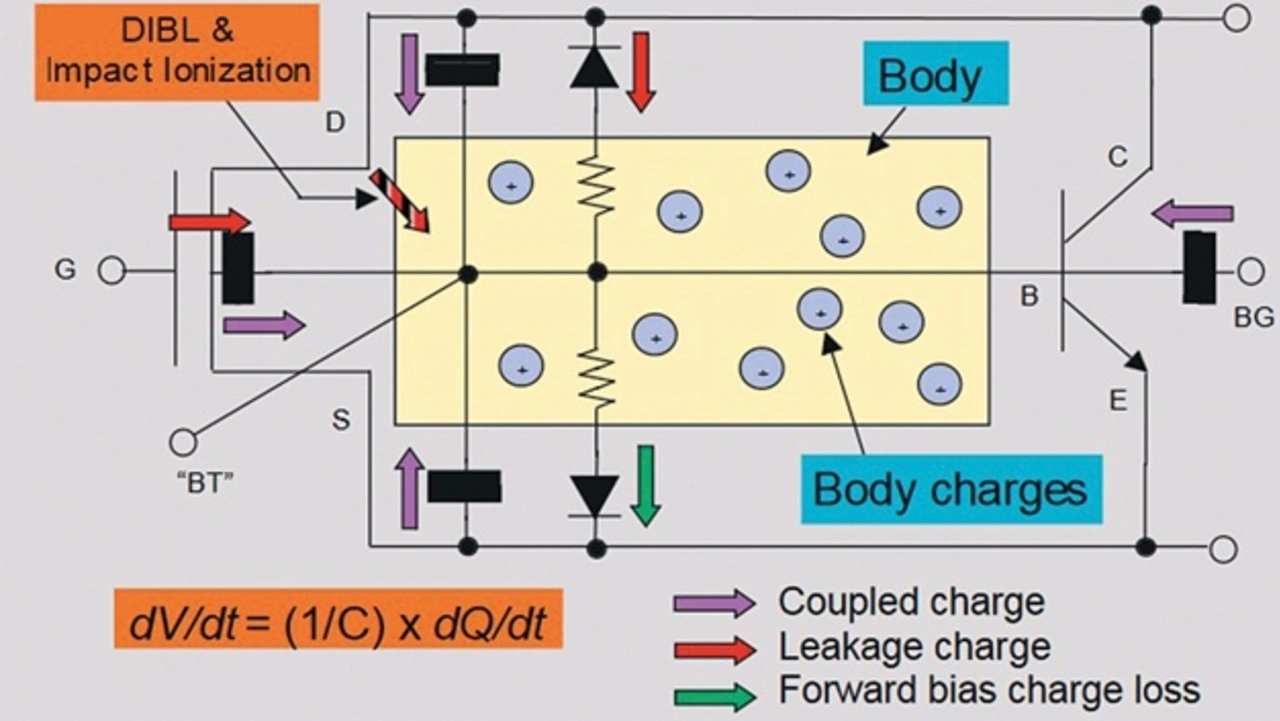

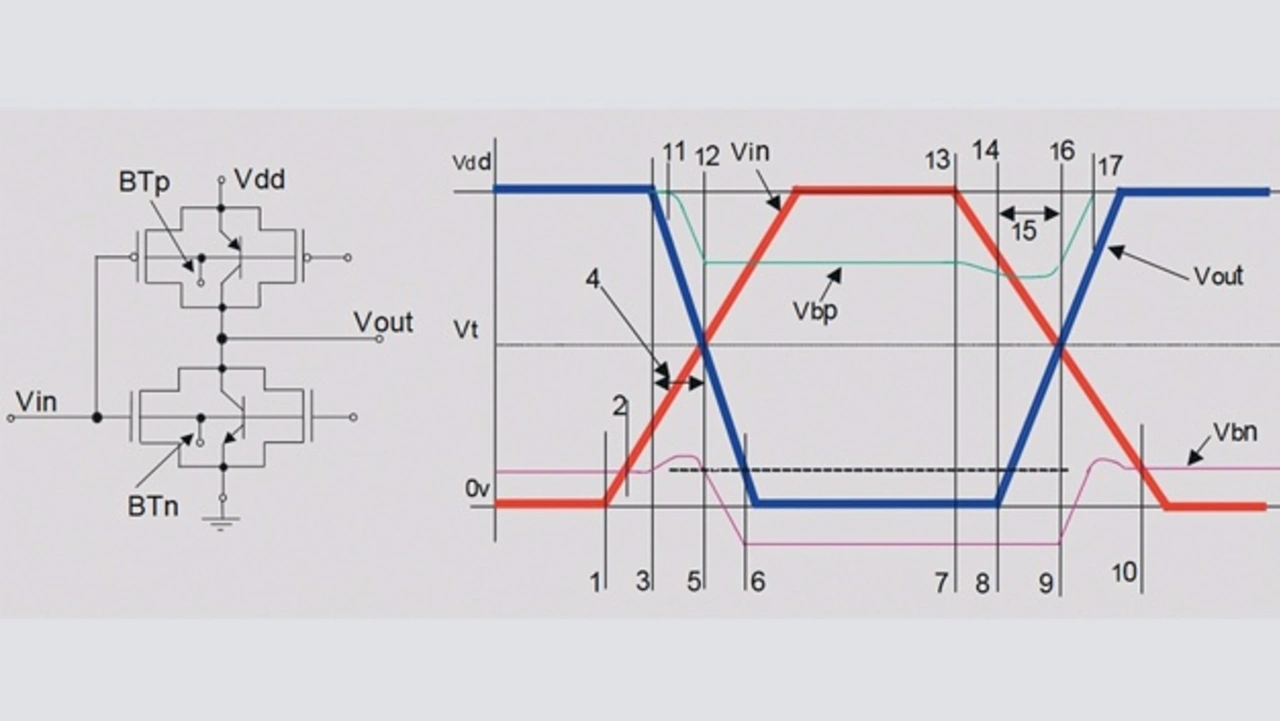

Allerdings kann damit bei PD-SOI-Transistoren der »Floating-Körper« über die Zeit Ladungen aufsummieren, wie es Bild 2 am Beispiel eines n-Kanal-Transistors zeigt. Die Konsequenz sind Variationen der Schwellenspannung (Bild 3 zeigt diese für einen Inverter mit n- und p-Kanal-Transistor), was das Chip-Design verkompliziert. Wie die Kurvenverläufe verdeutlichen (Bild 3), wird eine ideale Schaltfunktion mit senkrechten Flanken in der Praxis bekanntlich nicht erreicht, so dass es für den realen Schaltvorgang eine Rolle spielt, wie lange eine steigende oder fallende Flanke braucht, bis die Schwellenspannung erreicht ist. Idealerweise liegt diese genau in der Mitte zwischen Masse und Versorgungsspannung, doch wegen den in Bild 3 erkennbaren Ladungseffekten ist dies genau nicht der Fall. Die Zahlen von 1 bis 17 dokumentieren den zeitlichen Schaltverlauf in zwei Phasen, die in [2] genauer beschrieben sind:

- Eingangsspannung wechselt von Low auf High (n-Kanal-Transistor ist Off, p-Kanal-Transistor ist On): 1 bis 6 und 11 bis 12

- Eingangsspannung wechselt von High auf Low (n-Kanal-Transistor ist On, p-Kanal-Transistor ist Off): 7 bis 10 und 13 bis 17

Infolge der Eleminierung der Dotierung im Ladungsträgerkanal kann dieser keine Ladungen mehr halten, wodurch das Floating-Körper-Problem gelöst wird. Weil undotierte Transistoren jedoch sehr empfindlich gegenüber Variationen der Dicke der Silizium-Schicht sind, haben IBM und AMD die Probleme mit den Schwankungen der Schwellenspannungen in Kauf genommen und auf PD-SOI gesetzt.

Soitec hat es nun wie auch immer geschafft, eine Technik zu entwickeln, die 15 nm dicke Silizium-Schichten mit nur 3 % Dickenvarianz zulässt. Damit konnte der Ladungsträgerkanal vollständig verarmt werden (FD-SOI) und man begann mit STMicroelectronics einen 28-nm-Prozess in Crolles, Frankreich, zu entwickeln. Gleichzeitig lizensierte man den Prozess an Samsung, das ihn heute u. a. für NXPs i.MX-8-Prozessoren verwendet. Auch Globalfoundries lizensierte den 28-nm-Prozess und entwickelte ihn zu dem 22FDX-Prozess weiter. Anfang 2017 soll die Produktion anlaufen.

22FDX nutzt einen gestreckten Kanal in den PFETs sowie angehobene Source und Drain in NFETs und PFETs. Gegenüber dem 28-nm-FD-SOI-Prozess von ST reduziert sich die Leistungsaufnahme bei gleicher Frequenz um 55 %. Eine Versorgungsspannung von 0,3 V soll möglich sein, allerdings werden die Leckströme dort zunehmend größer, so wird das absolute Minimum der Leistungsaufnahme bei 0,4 V Versorgungsspannung erreicht. Dies ist noch immer wenig: Bei 28-nm-LP wird die geringste Leistungsaufnahme bei 0,65 V erreicht und wenn man bedenkt, dass die Versorgungsspannung quadratisch in die Leistung eingeht, sind dies erhebliche Einsparungen.

Mit einer Substratvorspannung (Body Biasing) kann eine adaptive Schwellenspannungssteuerung realisiert werden (Bild 4). Während eine positive Vorspannung die Schwellenspannung absenkt und die Schaltgeschwindigkeit erhöht (und leider zugleich die Leckströme steigen lässt), werden bei einer Vorspannung in Sperrrichtung die statischen Leckströme auf Kosten der Schaltgeschwindigkeit reduziert. Mit entsprechenden Schaltkreisen kann der Chip die Vorspannung je nach Betriebszustand anpassen: Im Sleep-Mode könnte man die Leckströme reduzieren und im aktiven Modus die Schaltgeschwindigkeit erhöhen. Globalfoundries bietet Body-Biasing optional an, da ca. 2 % bis 3 % zusätzliche Chip-Fläche benötigt werden.

Wie auch bei anderen Prozessen von Globalfoundries (z. B. 28-nm-HKMG) wurde der Gate-First-Ansatz gewählt, bei dem die Gate-Elektrode vor der Implantation und Aktivierung der Source- und Drain-Gebiete hergestellt wird. Der wesentliche Vorteil des Gate-First-Ansatzes ist, dass die Prozessreihenfolge im Wesentlichen der eines Polysilizium-Gates entspricht. Das heißt, es sind weniger Anpassungen an den Herstellungsprozess notwendig, was den Prozess sehr gut für Mixed-Signal-SoCs geeignet macht. Viele Gate-First-Ansätze hatten Ausbeute-Probleme, die Defektrate von 22FDX soll allerdings pro mm2 ähnlich aussehen wie bei 28-nm-HKMG – lassen wir uns überraschen, was in der Massenfertigung passieren wird.

Die Kombination des Gate-First-Ansatzes und SOI wirkt sich positiv auf diverse Analog-Charakteristiken aus. So werden hohe Werte für das Verhältnis von Transkonduktanz zu Treiberstrom erreicht, dies reduziert die Leistungsaufnahme von Schaltkreisen wie Leistungsverstärkern oder HF-Frequenzteilern. Dazu können HF-Signale bis zu einer Frequenz von 310 GHz erzeugt werden, was 22FDX auch für Millimeterwellen-Anwendungen wie 5G geeignet macht.

Die Kostenfrage: FD-SOI füllt eine Lücke

Der Grund, warum PD-SOI nie den Durchbruch schaffte, waren die relativ gesehen hohen Aufpreise: Ein prozessierter Wafer mit Bulk-Silizium-Chips kostete maximal 2000 Dollar, da machen einige hundert Dollar Aufpreis schon etwas aus. Ein prozessierter FinFET-Wafer kostet gegenwärtig hingegen 7000 Dollar plus x, da sind einige hundert Dollar Aufpreis vernachlässigbar. Zudem ist das Chip-Design bei FD-SOI wegen Entfall des Floating-Body-Problems einfacher als bei PD-SOI.

Wenn man 22FDX im Detail mit Globalfoudries 28-nm-HKMG-Prozess vergleicht (genannt 28SLP), stellt man fest, dass sich der kontaktierte Gate-Abstand nur um 9 % auf 104 nm verringert hat, was in einem Zyklus belichtet und geätzt werden kann (Single-Patterning). Von den acht Schichten müssen nur die ersten beiden Metallschichten (Pitch hier 80 nm, Reduktion gegenüber 28SLP rund 11 %) mit Double-Patterning ausgeführt werden. In Summe reduzieren sich die Fertigungsgeometrien nur um 20 %, also um einen halben Node gegenüber 40 % bis 50 % bei einem Voll-Node, deswegen heißt es auch nicht 20 nm sondern 22 nm).

Wegen der zwar limitierten aber doch gegebenen Double-Patterning Anforderungen und den ohnehin teureren SOI-Wafern sind prozessierte Wafer erstmal teurer als bei 28SLP. Auf der Habenseite kann man bei 22FDX jedoch eine größere Anzahl Dies (bei gleichem Design) und eine höhere Chip-Ausbeute erwarten. In Summe sollen somit die Die-Kosten für die meisten Designs vergleichbar sein. Der große Vorteil von 22FDX liegt in dessen reduzierter Leistungsaufnahme, angeblich sollen sogar Leckströme wie bei TSMCs 40-nm-ULL-Prozess erreicht werden, einem Ultra-Low-Leakage-Prozess für batteriebetriebene Anwendungen.

Bleibt noch die Frage nach dem 14-nm-LPP-Prozess. Dieser ist besonders bei großen Chip-Flächen 22FDX deutlich überlegen, sowohl kostenseitig (wegen geringerer Fläche pro Die; mit einem Gate-Pitch von 64 nm und einem Metall-Pitch von 64 nm werden die höheren Wafer-Kosten kompensiert) als auch mit höheren Treiberströmen, die längere Leitungen auf dem Chip und höhere Frequenzen zulassen, bei denen auch noch geringere Leckstöme auftreten.

Anders sieht das Bild bei typischen IoT-Anwendungen aus, bei denen geringere Taktfrequenzen und Chip-Flächen zu erwarten sind. Ist ein Die kleiner als 120 mm2 (und enthält es viele Analog- und HF-Blöcke) schlagen die geringeren Wafer-Kosten des 22FDX durch. Und weil die kleinere Source/Drain-Kapazität durch geringere (aktive) Leistungsaufnahme gegenüber 14LPP eine Kompensation der höheren Leckströme bewirkt, ist in Summe die Gesamtleistungsaufnahme vergleichbar.

Last, but not least: Einfachere Design-Regeln gegenüber FinFET-Designs reduzieren den Entwicklungsaufwand, was insbesondere für Designs mit kleineren Stückzahlen relevant ist.

STMicroelectronics konnte seinen 28-nm-FD-SOI-Prozess kaum monetarisieren, da die höheren Wafer-Kosten gegenüber 28-nm-HKMG nicht durch kleinere Die-Flächen kompensiert werden konnten. Samsung hingegen konnte im Jahr 2015 allein zwölf Tape-Outs berichten, 2016 sollen es ebenso viele werden. Ob die Koreaner die FD-SOI-Roadmap fortführen werden (was einigen Entwicklungsaufwand bedeutet), ist derzeit unklar.

Mit 22FDX hat Globalfoundries eine Lücke gefunden, die weder TSMC noch Samsung abdecken, und die sich an preissensitive IoT-Anwendungen mit limitiertem Energiebudget richtet. Marktforscher sehen darin ein signifikantes Marktvolumen, das – und das ist eine weitere gute Nachricht – im Gegensatz zu künftigen FinFET-Entwicklungen am Standort Dresden in Deutschland abgegriffen werden kann.

- FD-SOI: Preiswerte Alternative zu FinFET

- FD-SOI löst das PD-SOI-Problem

- So geht es weiter!