A/D-Wandler

Wandlung extrem

Fortsetzung des Artikels von Teil 2

Erfassung und Verarbeitung der digitalen Daten

Die ADC12D1X00-Familie ermöglicht die Wahl zwischen verschiedenen Datenausgabe-Betriebsarten. Für den Anschluss an FPGAs, die nicht mit der vollen Datenrate des Ausgangs arbeiten können, unterstützen die ADCs die nicht gemultiplexte Ausgabe der I- und Q-Kanäle. In diesem Demux-Modus gibt der ADC zwei aufeinanderfolgende Datenproben gleichzeitig an zwei, jeweils mit der halben Datenrate arbeitenden 12-bit-Datenbussen aus (1:2-Demultiplexing). Wird der Wandler für den einkanaligen Betrieb konfiguriert und im Interleaved- oder DES-Modus (Dual-Edge Sampling) betrieben, verdoppelt sich die Abtastrate von 1,8 auf 3,6 GSPS. In dieser Betriebsart stehen an den vier Bussen gleichzeitig vier aufeinanderfolgende Datenproben zur Verfügung (1:4-Demultiplexing). Diese Methode, den digitalen Ausgang zu demultiplexen, reduziert die Datenrate auf die Hälfte der Abtastrate, verdoppelt dafür aber die Zahl der ausgegebenen Daten-Bits. Für FPGAs, die mit der vollen Ausgangs- Datenrate dieser ADCs arbeiten können, ist auch die direkte 1:1- Ausgabe der Daten (Non-Demux) möglich.

Bei 3,6 GSPS im 1:4-Demux-Modus erfolgt die Ausgabe der 12-bit-Daten synchron zu einem 900-MHz-Takt. Doch selbst bei dieser reduzierten Datenrate wären einige FPGAs und Latches mit der direkten Erfassung der Daten überfordert. Es ist deshalb vorteilhaft, die DDR-CLK-Option zu nutzen, welche die Daten bei steigenden und fallenden Flanken des Taktsignals ausgibt.

Obgleich die Datenrate bei DDR-Signalisierung unverändert bleibt, halbiert sich die Abtast-Frequenz erneut auf besser beherrschbare 450 MHz. Der auf dem Referenzdesign-Board (ADC12D1X00RB) verwendete Virtex- 4-Baustein von Xilinx enthält zwei Digital-Clock-Manager (DCM), die es ermöglichen, Taktsignale intern zu generieren und zur Phasenlage des ankommenden Datensignals zu synchronisieren. Für das Debugging kann der ADC12D1X00 völlig unabhängig vom Taktsignal Prüfmuster an den vier Ausgangs- Ports generieren. Der Wandler wird dabei deaktiviert und stattdessen ein Prüfmuster-Generator an die Ausgänge angeschlossen. Die Prüfmuster- Ausgabe ist im DES- und im Nicht- DES-Modus identisch: An jedem Port liegt ein eindeutiges 12-bit-Wort, das, wie im Datenblatt beschrieben, zwischen 1- und 0-Werten alterniert.

Umstieg auf SDR-Architekturen

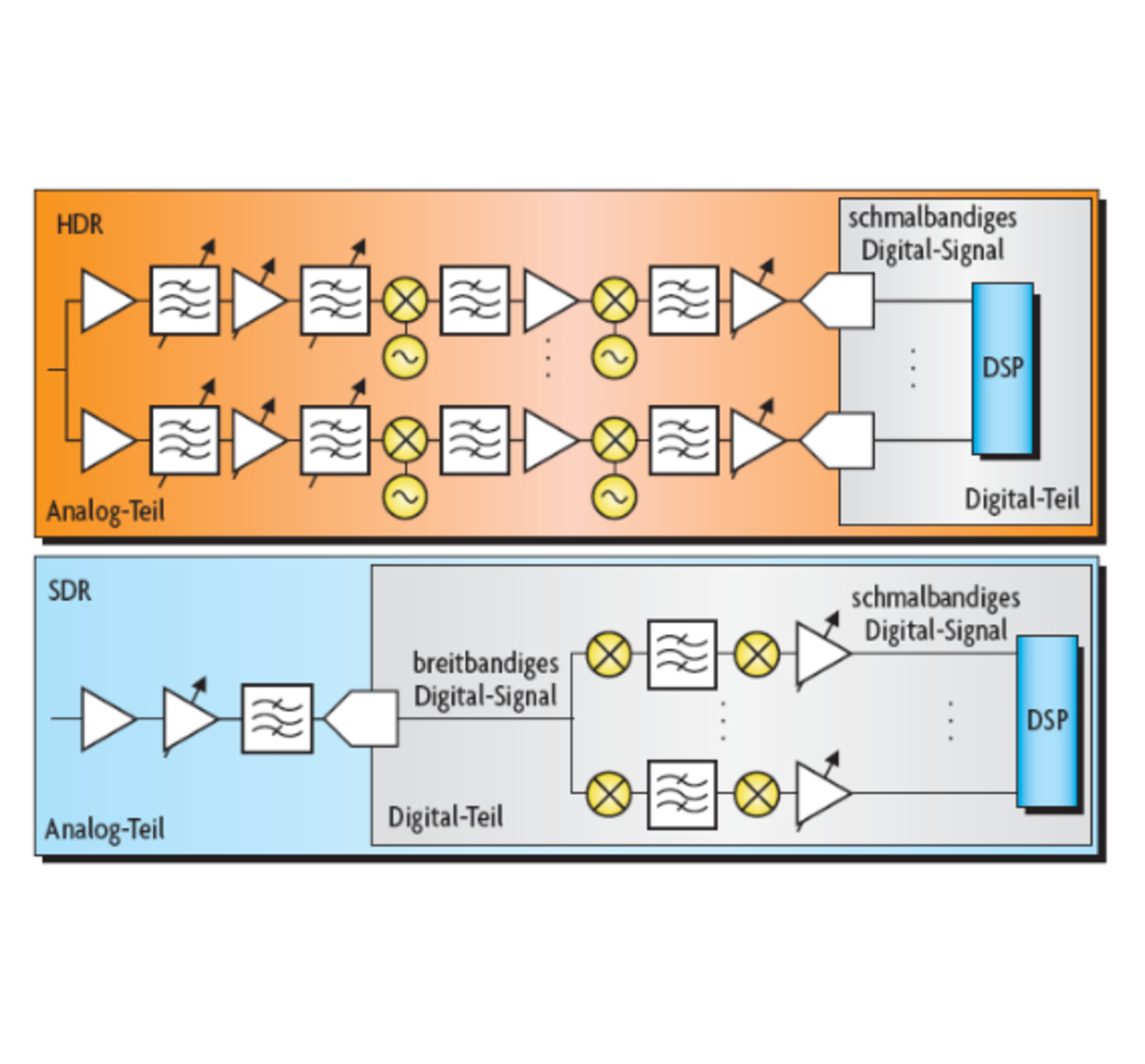

Die wichtigsten Merkmale einer Software- Defined-Radio-Lösung (SDR) werden nicht im analogen, sondern im digitalen Bereich festgelegt. Mischung, Abwärtswandlung, Filterung und weitere Signalverarbeitungs- Funktionen sind in einem FPGA oder ASIC angesiedelt, während in einer HDR-Architektur (Hardware-Defined-Radio) der Großteil der Verarbeitung mit analogen Bauelementen erfolgt. Zu den vielen Vorteilen der SDR-Technik gehören die höhere Flexibilität, die geringere Komplexität, weniger Platzbedarf und Stromaufnahme sowie niedrigere Hardware-Entwicklungs- und Redesignkosten.

Jobangebote+ passend zum Thema

Zur Aktualisierung dieses Konzepts ist es notwendig, die Digitalisierungsstufe näher an die Antenne zu rücken. Mit diesem Verfahren lässt sich das gesamte gewünschte Signalband digitalisieren, ohne dass komplexe, nichtlineare Mischer, LOs und Filter (ZF und Basisband) erforderlich sind. Zwar gibt es die SDR-Technik in unterschiedlichen Ausprägungen schon seit einigen Jahren, doch hat die A/D-Wandler-Technologie ihren Einsatz auf wenige Applikationen beschränkt, in denen 8- und 10-bit-Architekturen ausreichten. Ein Vergleich zwischen SDR- und HDR-Architektur ist in Bild 3 dargestellt.

Mit der Einführung dieser neuen 12-bit-Technologie können viele neue Systeme von den Vorteilen der SDR-Architekturen profitieren. Dazu gehören Prüfinstrumente (Spektrumanalysatoren, Digitaloszilloskope), Radarsysteme, Telekommunikations- Equipment (Satelliten, optische Übertragungsstrecken), Mehrkanal- Set-Top-Boxen, Funkaufklärungs- und Lidar-Systeme (Light Detecting And Ranging). Der Umstieg auf die SDR-Technik wird in jeder einzelnen Anwendung den Bauteileaufwand, die Materialkosten, den Platzbedarf und die Stromaufnahme reduzieren und außerdem für uneingeschränkte Flexibilität und Programmierbarkeit sorgen. Die Möglichkeit zum Upgrade, die die Wiederverwendung einheitlicher analoger Front-End-Module vorsieht, wird darüber hinaus dazu beitragen, zukünftige F&EAufwendungen zu senken.

Der Autor:

| Paul McCormack |

|---|

| ist Marketing Manager von Nationals High- Speed-Produktgruppe. Er ist seit 2001 bei National Semiconductor tätig und beschäftigt sich vorwiegend mit Applikationen, in denen Breitband-Datenwandler, -Verstärker und -Frequenz-Synthesizer eingesetzt werden. Er hat an der Queens University von Belfast studiert und besitzt ein Diplom im Fach Electrical & Electronic Engineering. |

Paul.McCormack@nsc.com

Literatur:

[1] Informationen über Hochgeschwindigkeitswandler: www.national.com/analog/adc/ultra_high_speed_adc

- Wandlung extrem

- Ultraschnelle Zusatz-Schaltungen

- Erfassung und Verarbeitung der digitalen Daten