A/D-Wandler

Wandlung extrem

Eine neue A/D-Wandlerfamilie erreicht Abtastraten bis 3,6 GSPS bei einem Eigenrauschen von –148,6 dBm/Hz. Angesichts der Tatsache, dass es der nächste konkurrierende 12-bit-Baustein lediglich auf 1 GSPS bringt, ist es interessant, zu untersuchen, wie dieser Leistungs-Sprung möglich ist und auf welche Weise diese Kombination aus Schnelligkeit und Rauscharmut erreicht wurde. Darüber hinaus werden Architektur und Prozesstechnologie dargestellt und welche Arten von Taktschaltungen benötigt werden. Abschließend werden die Anwendungsgebiete genannt, die von einer solchen Technologie profitieren können.

Beim Design von A/D-Wandlern im GSPS-Bereich ist die Auswahl an Architekturen nicht mehr sehr groß – am besten eignen sich die Flash- und die Folding-Architektur. Alle übrigen Architekturen (Pipeline, Subranging, Multi-Step) bedienen sich irgendeiner Art von Entscheidungsschleife. In Pipeline-Architekturen etwa wird das abgetastete Analogsignal zunächst von einem niedrig auflösenden A/D-Wandler digitalisiert, anschließend von einem D/AWandler wieder in ein analoges Signal verwandelt, um ein Fehlersignal zu generieren, das wiederum digitalisiert und von einer geeigneten Steuerungslogik verarbeitet wird. Diese Folge von Abläufen begrenzt zwangsläufig die Abtastrate, die von Pipeline-Architekturen maximal erreicht werden kann. Abhilfe bringt es, mehrere Pipeline- A/D-Wandler im Interleaved-Modus zu betreiben, doch bringt dies Nachteile in Bezug auf die Leistungsaufnahme.

Theoretisch gesehen sollte zwar die Flash-Architektur (Parallelwandler) die höchste Geschwindigkeit erreichen, denn der Zeitaufwand für eine Umwandlung wird hier ausschließlich von der Schaltgeschwindigkeit der parallel arbeitenden Komparatorkette bestimmt. Sie hat aber den gravierenden Nachteil, dass für eine Auflösung von N bit immerhin 2N – 1 Komparatoren benötigt werden, was den Flächen- und Strombedarf signifikant erhöht, sobald Auflösungen von mehr als 8 bit benötigt werden. Hinzu kommt, dass bei einer Auflösung von 8 bit oder mehr der Geschwindigkeit eine weitere Grenze gesetzt wird, weil das Codieren der Ausgänge so vieler Komparatoren seine Zeit dauert.

Jobangebote+ passend zum Thema

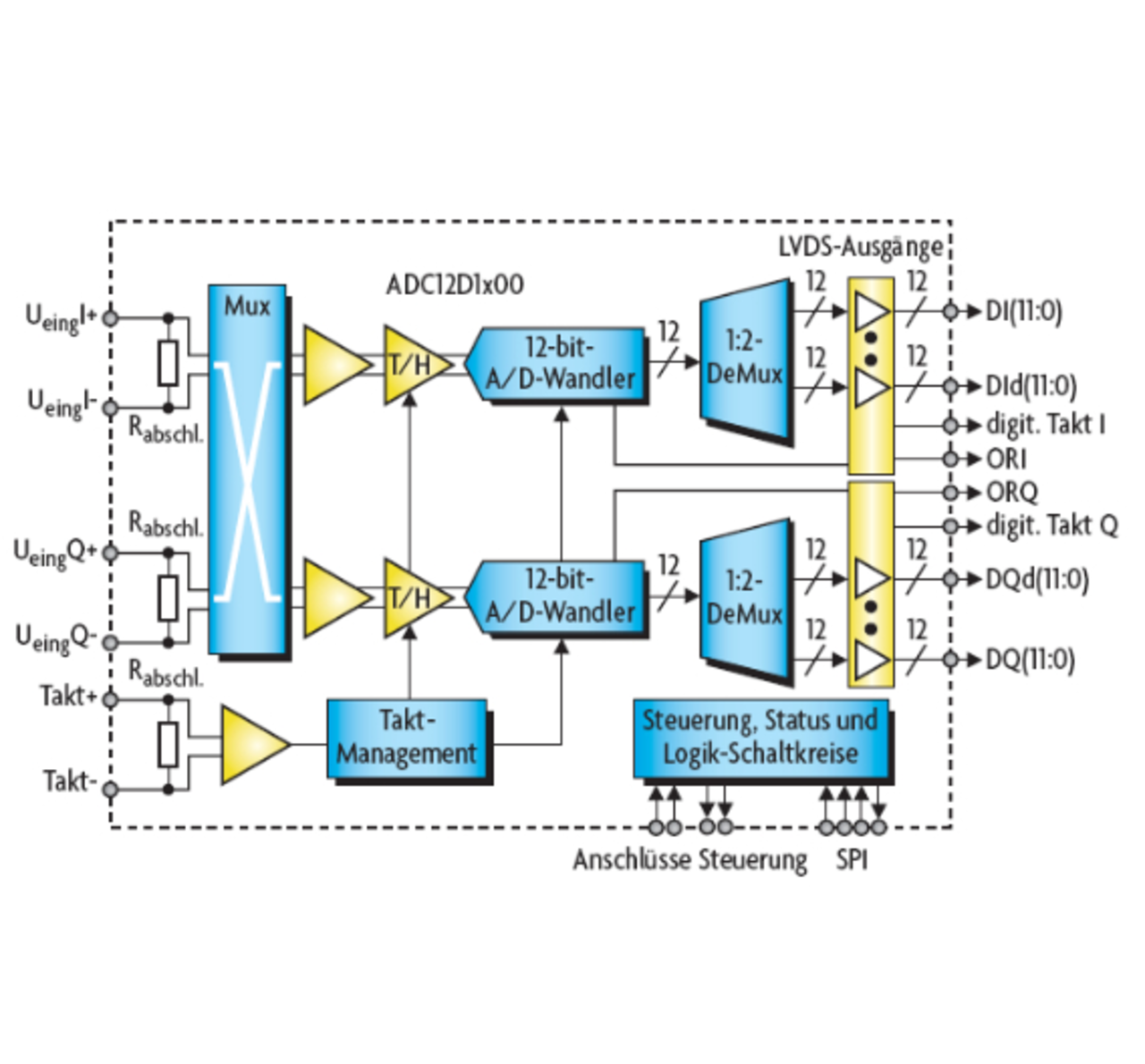

Aus diesem Grund basiert Nationals neue 12-bit-A/D-Wandlerfamilie ADC12D1X00 auf einer Folding-Architektur im Verbund mit den Vorteilen der Interpolation sowie einer für den Anwender transparenten Kalibrierung. Bild 1 gibt die Verarbeitungsschritte im Wandler schematisch wieder.

Die Folding-Architektur ist nahezu identisch mit der Flash-Architektur, jedoch werden die Komparatoren hier, abhängig vom Folding-Grad, mehrfach genutzt, sodass ihre Anzahl deutlich reduziert werden kann. Wenn F der Folding-Grad ist, beträgt die Zahl der für einen Wandler mit N bit Auflösung benötigten Komparatoren 2N/F + F – 2. Durch die Interpolation wird außerdem die Zahl der erforderlichen Front-End-Verstärker minimiert, was die Belastung des Eingangssignals verringert und die Leistungsaufnahme weiter senkt.

Der Nachteil der Folding-Technik ist die höhere Offset-Empfindlichkeit verglichen mit der Flash-Architektur. Um diese Effekte zu kompensieren, kommt im ADC- 12D1800 ein On-Chip-Kalibrierverfahren zum Einsatz, das Offsets in den Vorverstärker-Stufen des A/D-Wandlers korrigiert. Hierdurch wird die Krümmung der INL-Kurve von Folding- Architekturen reduziert.

Folding, Interpolation und On- Chip-Kalibrierung sorgen zusammen für eine signifikante Reduzierung der Chipfläche und der Leistungsaufnahme im Vergleich zu anderen Architekturen. Die chip-interne Kalibrierung wird nach dem Einschalten der Betriebsspannung selbsttätig angestoßen und kommt ohne externe Signale oder Steuerungsschaltungen aus.

Die Produktion dieser Wandlerfamilie erfolgt in einem CMOS-Prozess mit 0,18-μm- Geometrie, der von National Semiconductor eigens mit der Vorgabe entwickelt wurde, bei minimaler Verlustleistung ein optimales Rauschverhalten zu erzielen.

Andere ultraschnelle A/D-Wandler basieren dagegen auf Bipolar- oder BiCMOS-Prozessen, die in der Regel mindestens zwei Versorgungsspannungen erfordern und eine beträchtliche Leistungsaufnahme aufweisen. Der Doppel-Wandler ADC- 12D1800 (Bild 2) kommt mit einer einzigen Versorgungsspannung von 1,9 V aus und nimmt lediglich 2,05 W je Kanal auf.