Embedded Computing / Testspezifizierung

Automatisierung von IP- bis auf SoC-Ebene

Fortsetzung des Artikels von Teil 4

PSS auf Subsystem- und SoC-Ebene

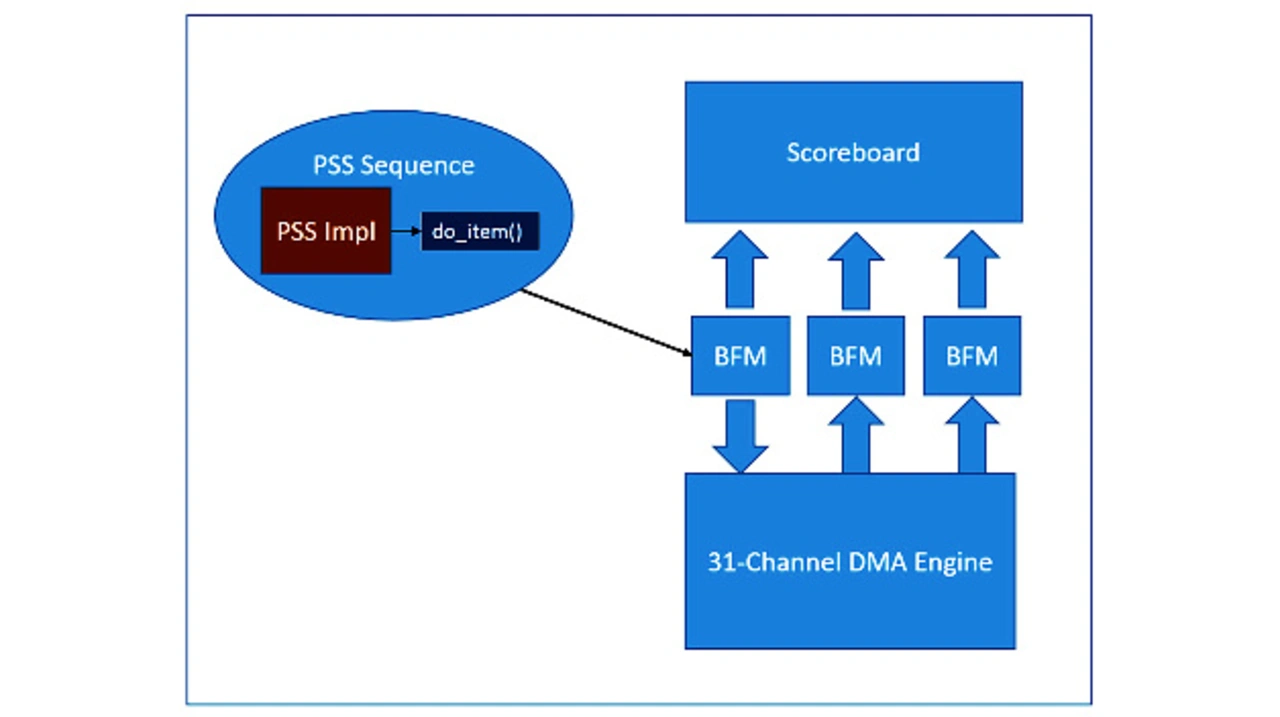

Hier ändern sich sowohl Verifikationsgegenstand als auch -methode. Es soll die Integration der DMA-Funktionseinheit mit anderen Blöcken im Subsystem oder SoC verifiziert werden. Wesentlicher Unterschied ist ein – vor allem auf SoC-Ebene – eingebetteter Prozessor, auf dem Testaktivitäten mit Code laufen sollen. Ausgangspunkt bei Umgebung auf Subsystemebene ist das Blockdiagramm Bild 9.

Jobangebote+ passend zum Thema

Die DMA-Funktionseinheit befindet sich nun im Kontext eines Subsystems, das einen Prozessor (mit einem Bus-Funktionsmodell) und andere IP enthält.

Die Migration der PSS-Beschreibung in diese Subsystem-/SoC-Umgebung erfolgt in zwei Schritten:

- Modellierung der Testanforderungen

- Spezifizierung der neuen Umgebung zur Integration

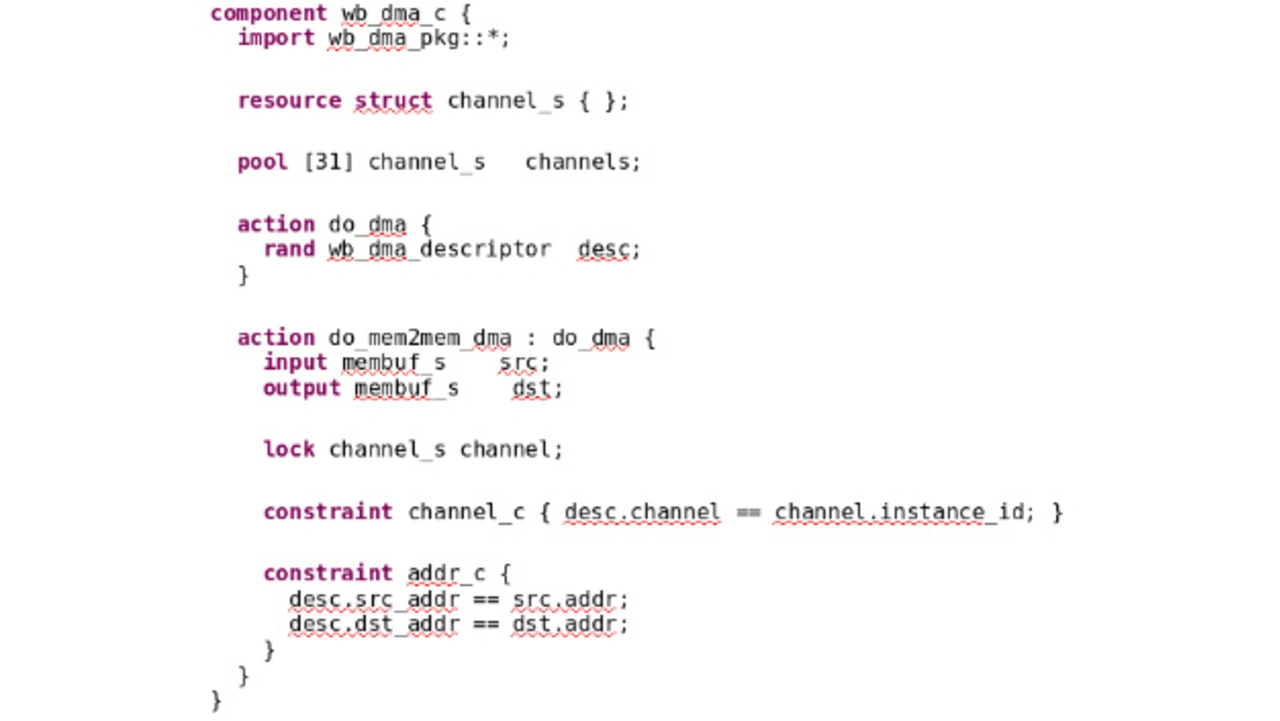

Zur Verifikation der Integration mit anderer IP, erfolgen mehrere parallele DMA-Transfers. Zunächst wird die Komponente dma_c zur Ressourcenspezifikation (hier 31 DMA-Kanäle) erweitert. Weiterhin wird ein neuer Aktionstyp generiert, der einen DMA-Kanal belegt und seine Datenflussanforderungen spezifiziert (Bild 10).

Die aktualisierte DMA-Komponente und Aktion (Bild 11) spezifizieren nun, dass:

- der DMA über 31 Kanalressourcen verfügt (unter Verwendung des Ressourcen-Pools),

- jede DMA-Operation einen Quellspeicherpuffer besitzt und einen Zielspeicherpuffer erzeugt,

- jede Operation do_mem2mem_dma mit Ursprung do_dma den Zugriff auf einen DMA-Kanal erfordert (mittels Lock-Feld),

- der im DMA-Deskriptor spezifizierte Kanal auch die DMA-Operation zugewiesen bekam und

- jene für die DMA-Operation verwendeten Quell- und Zieladressen mit dem Quell- und Zielspeicherpuffer übereinstimmen.

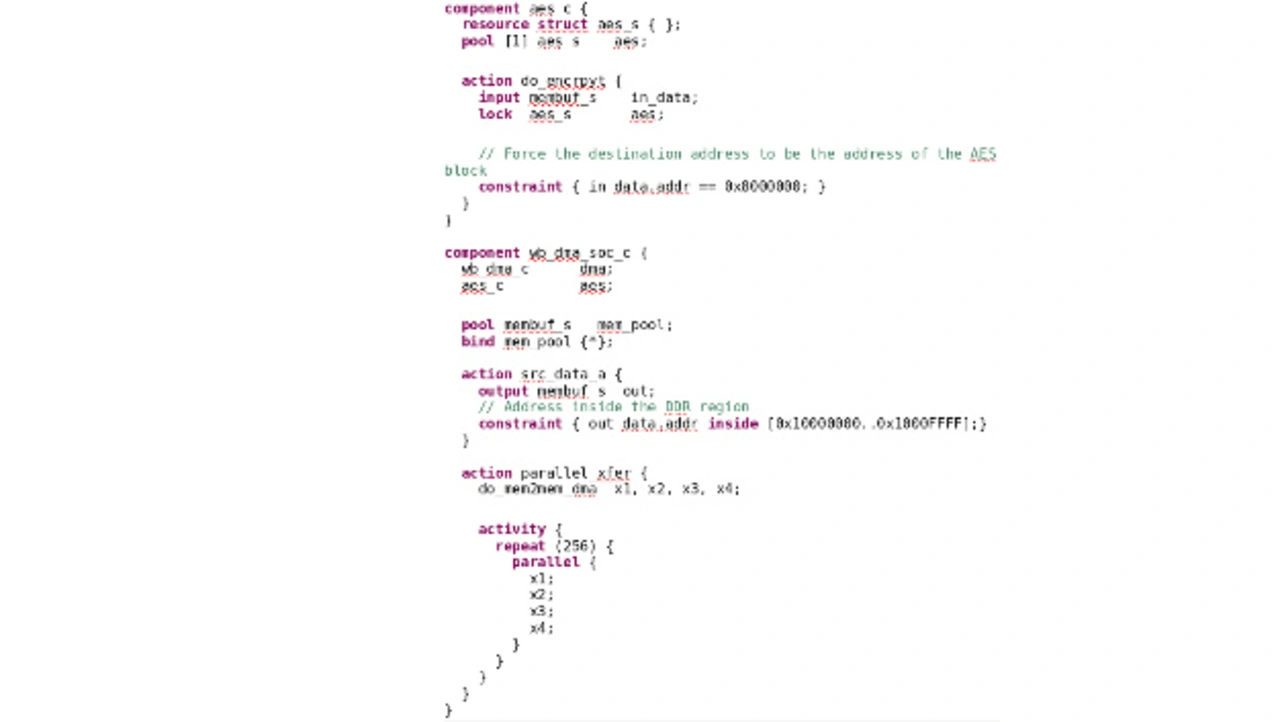

Um Details hinzuzufügen, wird eine Komponente aes_c zur Modellierung von Operationen auf dem AES-Block erstellt. Die Aktion do_ encrypt belegt dabei einen Speicherpuffer; die Adresse der Eingabedaten soll der Pufferadresse des AES-Blocks entsprechen.

Da die membuf_s Eingänge bidirektional sein sollen, zwingt diese Vorgabe die DMA, das AES -Gerät einzubinden, wenn eine do_mem2mem_dma-action Daten an eine do_encrypt-action sendet. Zur Spezifizierung, dass nur eine einzelne Operation auf dem AES-Block durchgeführt wird, nutzt die Komponente aes_c einen Ressourcenpool. Schließlich wird eine Komponente festgelegt, die das System zur Spezifikation der verfügbaren Ressourcen (DMA- und AES-Blöcke) bildet. Zudem wird auf oberster Ebene eine Aktion zur Durchführung von parallelen DMA-Transfers definiert, sodass vier parallele DMA-Operationen erfolgen.

Diese Teilspezifikation legt weder Datenursprung noch -ziel fest. Um die Erzeugung legaler Szenarien zu gewährleisten, ergänzt PSS die Nebenbedingungen:

- Jede der vier parallelen Übertragungen erfolgt auf einem anderen DMA-Kanal,

- nur eine Operation läuft jeweils auf dem AES-Block.

Diese partielle Spezifikation erzeugt komplexe Testszenarien aus einfachen, knappen Spezifikationen.

- Automatisierung von IP- bis auf SoC-Ebene

- Die PSS-Grundlagen

- Wiederverwendung von SystemVerilog-Regeln

- Szenarien beschreiben

- PSS auf Subsystem- und SoC-Ebene

- Integration auf SoC-Ebene