Embedded Computing / Testspezifizierung

Automatisierung von IP- bis auf SoC-Ebene

Fortsetzung des Artikels von Teil 1

Die PSS-Grundlagen

Portable Stimulus zielt auf eine erhöhte Abstraktionsebene und die Automatisierung komplexer Testszenarien auf Subsystem- und SoC-Ebene. Grundlage der PSS ist die bekannte, auf Constraints basierende Transaktionslevel-Verifikation. Entsprechend unterstützt die Accellera PSS zufällige und nicht zufällige Datenfelder und Strukturen, bekannte SystemVerilog-Constraints und aus objektorientierten Sprachen bekannte Vererbungsmuster.

SystemVerilog erstellt Szenarien unter Mischung von zufälligem mit prozeduralem Code, was Portierbarkeit und Modifizierbarkeit einschränkt. Eine PSS-Aktion kann sowohl primitives Verhaltenselement sein, als auch zur Verkapselung von komplexem Verhalten, das leicht wiederverwendet und angepasst werden kann, genutzt werden; komplexe Aktionen führen sequentielle wie parallele Unteraktionen aus. Iterationen werden ebenfalls als Unteraktionen definiert.

Dedizierte Konstrukte modellieren die Aktionsressourcen und regeln ihre Kommunikation. Damit werden Regeln geschrieben, die legale Szenarien begrenzen, welche das Werkzeug automatisiert generiert. Dies ist ähnlich den Datenbeschränkungen, welche Grenzen einer legalen Transaktion spezifizieren und damit einem Constraintsolver die automatische Generierung vieler legaler Transaktionen ermöglichen.

PSS auf Blockebene

Die Anwendung von Portable Stimulus in Block-Level-Verifikationsumgebungen bringt enorme Vorteile, weil Portable-Stimulus-Tools sehr effiziente und zielgerichtete Testgenerierungen ermöglichen. In einer Block-Level-Umgebung lassen sich durch effiziente Testerzeugung die Ziele der funktionalen Coverage viel schneller erreichen und Fehler früher im Verifikationszyklus finden. Anwender von Mentors Questa inFact berichten über ein zehn- bis hundertmal effizienteres Erreichen der Coverageziele als bei zufälliger Erzeugung der Stimuli.

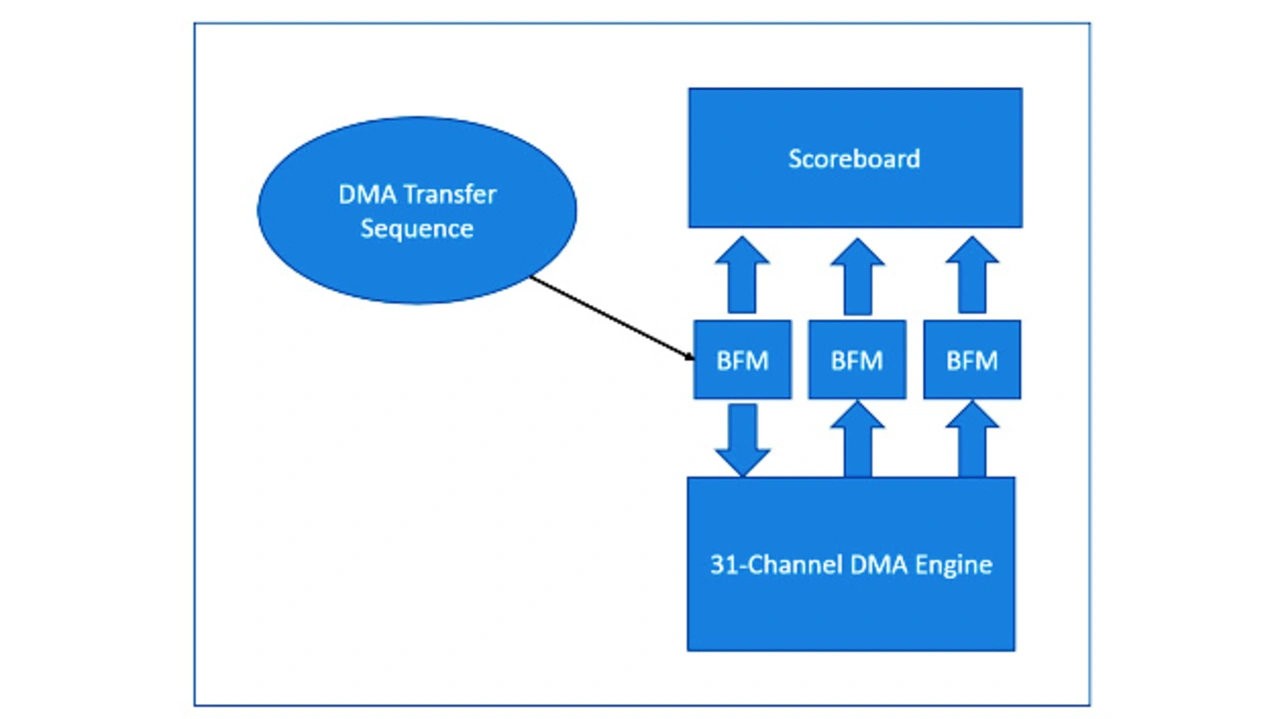

Ebenso wird der Coverageumfang ohne Aufstocken der Simulationsressourcen erweitert. Als Arbeitsbeispiel dient eine mehrkanalige DMA-Funktionseinheit. In ihr charakterisiert eine Transferbeschreibung die Transfergröße, Ursprungs- und Zieladressen sowie die Inkrement-Einstellungen der Adressen und detaillierte Übertragungsoptionen von Speicherübertragungen.

Jobangebote+ passend zum Thema

Zur Verifizierung der DMA-Implementierung sollen sämtliche Kombinationen dieser Transfer-Deskriptor-Felder auf Blockebene angewandt werden.

Bild 2 zeigt eine vereinfachte Ansicht der diese IP umgebenden UVM-Testbench. Die DMA-Funktion wird durch eine UVM-Sequenz ausgeführt, die Register in der DMA-Funktionseinheit gemäß einer DMA-Deskriptorklasse programmiert.

- Automatisierung von IP- bis auf SoC-Ebene

- Die PSS-Grundlagen

- Wiederverwendung von SystemVerilog-Regeln

- Szenarien beschreiben

- PSS auf Subsystem- und SoC-Ebene

- Integration auf SoC-Ebene