Low-Power-Design mit SoCs

Mehr Leistung, weniger Power

Fortsetzung des Artikels von Teil 1

Aktuelle SoCs: High Performance oder Low Power?

Derzeit gibt es drei Hersteller, die SoCs im Sinne einer Kombination von Prozessor und FPGA auf einem Chip anbieten. Da sind zum einen die beiden großen FPGA-Hersteller Xilinx und Altera, die unterschiedliche Ausführungen im Programm haben, und zum anderen der auf Sicherheit und Low-Power-FPGAs spezialisierte Hersteller Microsemi. Die Tabelle vergleicht die Produkte der drei Hersteller angesichts wesentlicher Aspekte. Was direkt beim Blick auf die Tabelle auffällt, ist, dass alle drei Hersteller beim Prozessor auf die ARM-Architektur setzen. Altera und Xilinx verwenden hierbei Cortex-A9-Prozessoren, die mit einer Taktrate von bis zu 1 GHz im High-End-Bereich anzusiedeln sind. Altera bietet zwei verschiedene SoC-Typen an, die nach der verwendeten FPGA-Architektur unterschieden werden. Xilinx fasst alle seine SoCs unter dem Produktnamen Zynq zusammen, wobei auch hier zwei verschiedene FPGA-Architekturen zum Einsatz kommen. Während alle Chips von Xilinx einen Dual-Core ARM Cortex-A9 enthalten, bietet Altera auch ein Cyclone-V-SoC mit nur einem Prozessorkern an.

Microsemi, dessen Produkte eher im Low-Power-Bereich angesiedelt sind, verwendet einen Cortex-M3-Kern. Die von Microsemi eingesetzte FPGA-Technologie ist Flash-basiert und unterstützt einige weitere Funktionen, die besonders auf sichere Designs abzielen. Damit soll einerseits das Kopieren oder Reverse Engineering von Designs verhindert werden und andererseits der Einsatz der SmartFusion-Chips in sicherheitskritischen Anwendungen ermöglicht werden. Microsemi gibt an, dass der Energieverbrauch ihrer Flash-basierten Produkte um 50 % geringer ist als der herkömmlicher SRAM-basierter FPGAs.

Jobangebote+ passend zum Thema

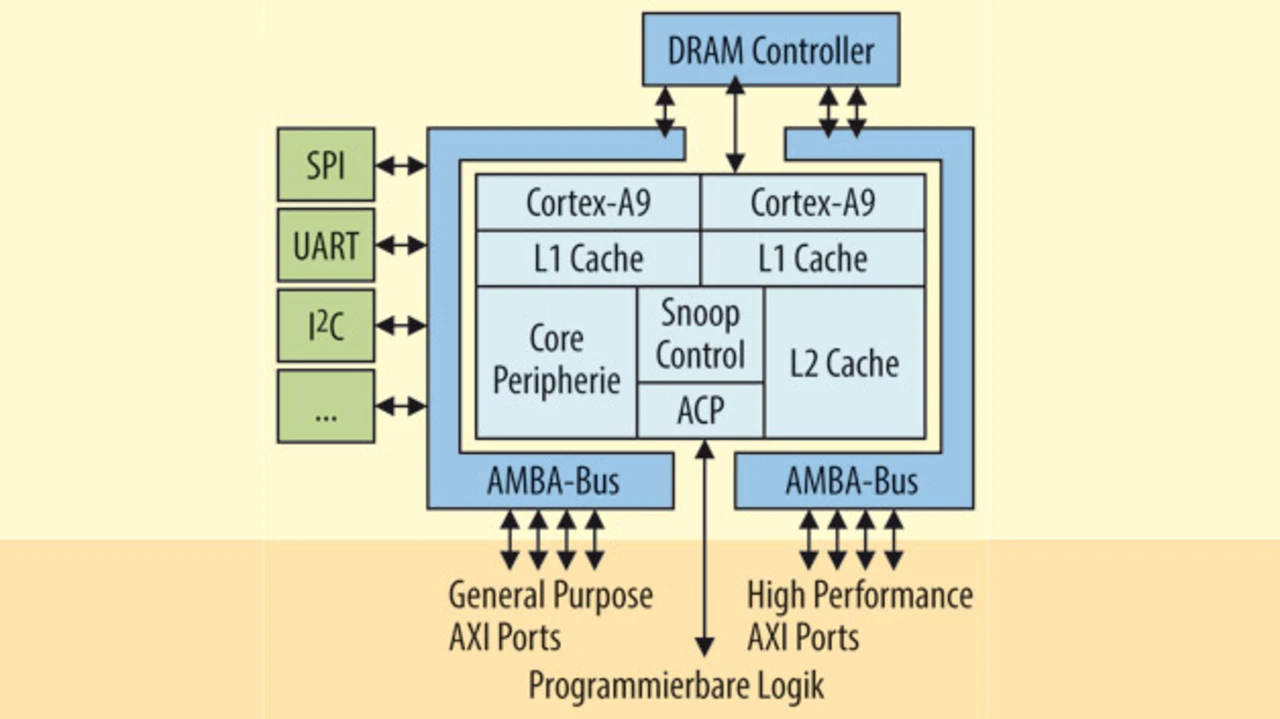

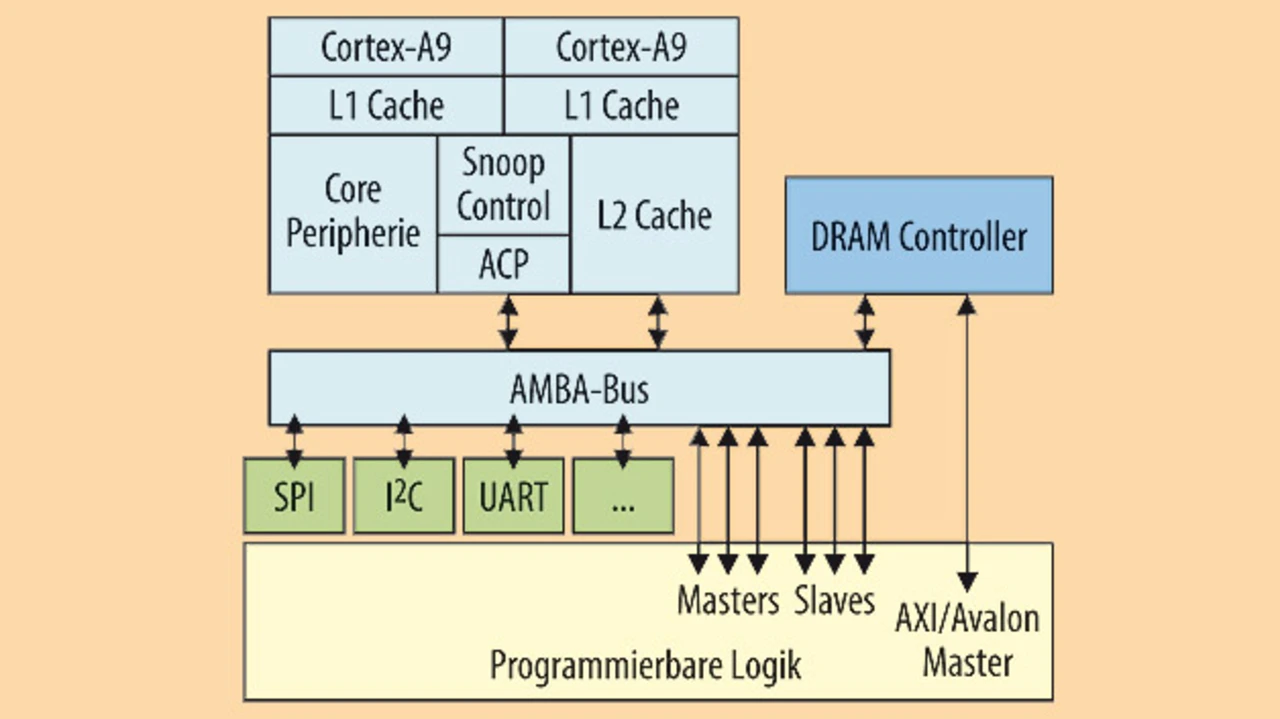

Ein weiterer wichtiger Unterschied zu vielen Urahnen der SoCs und Systemen mit einer Soft-CPU ist die Trennung zwischen Prozessorsystem und FPGA. Während bei älteren Architekturen wie dem Virtex4-FX der Memory Controller und sämtliche Peripherie im FPGA instanziiert werden musste, sind bei den neuen SoCs sowohl der FPGA als auch das Prozessorsystem eigenständig. In den Bildern 1 und 2 ist dies beispielhaft an der Architektur des Xilinx Zynq und des Cyclone V SoC von Altera zu sehen. Die Prozessoren sind in einem eigenen Block untergebracht, der einen Memory Controller, das Cache-Subsystem, das Bussystem und eine große Zahl von Standardperipherie wie SPI, CAN, I2C und UARTs enthält. Dieser Block ist physikalisch im Silizium des SoCs implementiert, verbraucht also keine Ressourcen im FPGA und ist sofort verfügbar, sobald der Chip mit Spannung versorgt wird.

Die eigentliche Leistungsfähigkeit und Flexibilität der Kombination aus FPGA und Prozessor entsteht durch die enge Kopplung der beiden Systeme. Sowohl beim Zynq als auch beim Cyclone V existieren mehrere AXI4-Busschnittstellen, die einen Datenaustausch zwischen Prozessorblock und FPGA ermöglichen. In beiden Bausteinen gibt es sowohl Master als auch Slave Ports vom FPGA zum internen Systembus des Prozessorblocks. Damit ist es z.B. möglich, mit der DMA Engine des Prozessorblocks auf anwendungsspezifische Hardware im FPGA zuzugreifen. Umgekehrt ist eine Nutzung der Peripherie des Prozessorblocks aus dem FPGA heraus möglich. Um bei datenintensiven Anwendungen im FPGA den internen Systembus des Prozessors nicht zu überlasten, bieten beide Bausteine einen separaten Bus zwischen Memory Controller und FPGA an. Hier können Daten direkt zwischen FPGA und Hauptspeicher übertragen werden.

Eine besonders enge Kopplung zwischen FPGA und Prozessor ist über den Accelerator Coherency Port (ACP) möglich, der sowohl in den Chips von Altera als auch in denen von Xilinx vorhanden ist. Hier ist ein kohärenter Datenaustausch zwischen Prozessor und FPGA möglich. Dabei können Daten direkt zwischen dem FPGA und dem L2 Cache des Prozessorsystems ausgetauscht werden, ohne dass der Umweg über den Hauptspeicher genommen werden muss. Dadurch wird sichergestellt, dass die Daten, die zwischen Prozessor und FPGA ausgetauscht werden, konsistent sind, ohne dass ein Cache Flush durchgeführt werden müsste.

Durch diese Möglichkeiten, applikationsspezifische Hardware eng an das Prozessorsystem zu koppeln, können leistungsfähige Embedded-Applikationen entwickelt werden. So wird die (theoretisch) mögliche Speicherbandbreite zwischen FPGA und Hauptspeicher beim Zynq von Xilinx mit 9600 MB/s [2] angegeben. Diese Bandbreite ist mit einer Lösung aus getrenntem FPGA und Prozessor nur schwer zu erreichen.

- Mehr Leistung, weniger Power

- Aktuelle SoCs: High Performance oder Low Power?

- Toolchain

- Enge Kopplung zwischen Prozessor und anwendungsspezifischer Hardware durch SoCs