Evolution in der Datenübertragung

Der lange Weg von 1-Gbit/s-NRZ zu 224-Gbit/s-PAM4

Im Lauf der Jahrzehnte haben neue Anwendungen mit immer höheren Anforderungen die Datenübertragungsraten von 1-Gbit/s-NRZ auf 224-Gbit/s-PAM4 erhöht. Welche Entwicklungsschritte es über die Jahre gab und welche Designherausforderungen sich bei 224-Gbit/s-PAM4 stellen, wird hier erläutert.

Neuerungen bei der halbleiterbasierten Signalaufbereitung und -rückgewinnung haben die Datenraten erhöht, indem sie das zulässige Signal-Rausch-Verhältnis (SNR) zu immer höheren Nyquist-Frequenzen verlagern. Es lässt sich feststellen, dass jede nachfolgende Signalisierungstechnik auch das elektromechanische Design komplexer macht, das erforderlich ist, um die Kanalphysik zu berücksichtigen und das SNR der aktiven Bauelemente zu berücksichtigen. Diese Entwicklungen haben die Grundlage für neue Designziele geschaffen, sie ermöglichen ein besseres Verständnis heutiger Anforderungen an die physikalische Schicht von 224-Gbit/s-PAM4.

Jobangebote+ passend zum Thema

Blick auf die historische Entwicklung

Mit den verschiedenen Geschwindigkeitsstufen entwickelt sich auch das Design der physikalischen Schicht von Leiterplatten, Kabelbaugruppen und Steckern weiter. Die Anpassungen bei Datendurchsatz und Latenzzeit stellen nun zuvor akzeptable Designkompromisse infrage.

Die Anforderungen an die schnelle Datenübertragung steigen stetig, um den Entwicklungen am Markt wie Cloud-Computing, künstliche Intelligenz (KI), 5G und dem Internet der Dinge gerecht zu werden. Obwohl es Überschneidungen in den Details gibt, soll ein kurzer Rückblick helfen, die technische Entwicklung von 1-Gbit/s- bis zu den heutigen 224-Gbit/s-Datenraten zu veranschaulichen.

… vor 30 Jahren

Vor etwa 30 Jahren drehte sich die Diskussion um Return to Zero (RZ) gegenüber Non-Return to Zero (NRZ). Die meisten Signale innerhalb des Rechenzentrums (in oder zwischen den Racks) waren unsymmetrisch, bis Twisted-Pair-Ethernet aufkam. Entwickler bei Cray gingen damals bis an die Grenzen, um NASA-Workloads zu unterstützen, die über mehrere Rechenknoten mit einer Datenrate von 80 MHz unter Verwendung von differenziellen Paaren liefen. Im Vergleich dazu waren die ersten IBM-PCs zu jener Zeit mit 4,77 MHz getaktet.

Damals wurden die Prozessortakte geteilt statt multipliziert. Leiterplatten (Printed Circuit Boards, PCBs) wurden von Verdrahtungsboards auf mehrlagige FR4-Leiterplatten umgestellt und buchstäblich von Hand mit echtem Klebeband abgeklebt. Für Drucker kamen mehradrige Kabel und für Netzwerke Koaxialkabel zum Einsatz. RJ45 fand bei Telefonen Verbreitung, und ICs ersetzten einzelne Komponenten auf den Leiterplatten. Im Labor war es noch möglich, Prototypen von Schaltungen mithilfe von Prototyping-Boards zu erstellen und Signale mit einem Oszilloskop zu messen. Für die Simulation genügten pauschale Werte (L, R, C, k), um die meisten Unstetigkeiten zu modellieren.

… vor 20 Jahren

Vor etwa 20 Jahren begann die NRZ-Signalübertragung zu dominieren. Beim Übergang von 1- auf 3- und dann 6-Gbit/s-NRZ wurde die Aufmerksamkeit des mechanischen/elektrischen Designs auf geometrische Änderungen gelenkt. Generell wurde der Steckverbinder oder die Leiterplatte aber immer noch als Verlustkomponente behandelt. Durch die NRZ-Designanforderungen verdoppelte sich die Kanalbandbreite, während sie anfälliger für Störungen wurde. Um Datenfehler zu verringern, wurde das SNR durch eine höhere Leistung und zusätzliche Entzerrungstechniken verbessert.

Electronic Design Automation (EDA) für Leiterplatten kam zusammen mit Gerber-Dateien auf den Markt. Die Steckverbindertechnik für Daten um- fasste die Edgecard und den 9-poligen D-Sub. Die Belastung von Oszilloskopen näherte sich ihrer Grenze, VNA (Vector Network Analyzer) und die FFT-Analyse (Fast-Fourier-Transformation) setzte sich durch. Für die Simulation fanden manchmal Pauschalwerte (L, R, C, k) Verwendung, während SPICE-Modelle für die Simulation von Übertragungsleitungen in- tegriert wurden, um Unstetigkeiten zu simulieren.

… vor 15 Jahren

Vor etwa 15 Jahren begann der Über-gang von 10- auf 16- und 25-Gbit/s- NRZ. Backplane-Kabel wurden zur Norm, und viele Unternehmen entwickelten Backplane-Demoboards, um Anwendungen mit 1 m Leiterbahnlänge nachzubilden. Pauschale Komponentenmodelle für Steckverbinder oder Unterbrechungen in Übertragungsleitungen reichten dann nicht mehr aus. Wie in der HF-Branche üblich, wurden die gängigen Bonddrähte, PCB-Vias und Steckverbindersegmente mit eigenen S-Parameter-Komponenten dargestellt. Das Übersprechen entwickelte sich zu einem zunehmend kritischen Faktor in der Entwicklung.

Signalintegritätslabore verfügten über 50-/100-Ω-Datengeneratoren mit Oszilloskopen mit hoher Bandbreite für die Zeitbereichsanalyse. Neben jedem Zeitbereichstestsystem befand sich ein VNA. Gelegentlich kamen auch HF-Tastköpfe zum Einsatz, aber die meisten Prüfvorrichtungen basierten auf SMA-Neuerungen. Etwa zu dieser Zeit entstand eine spezialisierte Gruppe von Signalintegritätsexperten in den Reihen der Elektrotechniker.

… vor 10 Jahren

Vor etwa 10 Jahren begann der Übergang von 28- auf 56-Gbit/s-PAM4, was sich auf das Design von Übertragungsleitungen auswirkte und eine Signaländerung bei der Modulation von NRZ zu PAM4 mit sich brachte. Mit dem Ziel, die Datenraten weiter zu erhöhen, übernahm die Industrie die Pulsamplitudenmodulation (PAM) aus der optischen Industrie. PAM4 ist im optischen Bereich allgegenwärtig, was die Übernahme in Kupferverbindungen mit großer Reichweite im Vergleich zu anderen Modulationsverfahren erleichtert.

In Kupferleitungen nutzt PAM4 vier Spannungspegel, um zwei Datenbits pro Symbol darzustellen. Durch die Codierung von zwei oder mehr Bits pro Symbol erhöht PAM die Datenrate, ohne die erforderliche Kanalbandbreite zu erhöhen. Die Folgen für die Signalisierung und das Design der Übertragungsleitungen sind eine höhere Empfindlichkeit gegenüber Rauschen und Abweichungen bei der Einfügungsdämpfung.

Dies führte in der Branche zum Übergang von 28-Gbit/s-NRZ zu 56-Gbit/s- PAM4 oder im Fall von PCIe von 32-Gbit/s-NRZ zu 64-Gbit/s-PAM4. Der Anwendungsbereich war entweder Vernetzung oder Datenverarbeitung. In beiden Fällen wurde beim Kanaldesign das gleiche UI (Unit Interval) und die gleiche Nyquist-Frequenz eingehalten. Nachteil: Die daraus resultierenden mehreren Signalisierungsebenen machten ein besseres Kanal-SNR nötig, was Aufmerksamkeit auf unbeabsichtigte Signalkopplung (Übersprechen) und Einfügungsdämpfung erforderte.

Dabei wurde dem Übersprechen mehr Aufmerksamkeit gewidmet, insbesondere am Ende und an den Übergängen zwischen den Komponenten: Steckverbinder zu Leiterplatte, Steckverbinder zu Kabel/Leiterplatte und Steckverbinder zu Steckverbinder. Die Testgeräte im Labor waren hauptsächlich VNAs. Die neue Aufgabe lautete: weniger Stichleitungen in Leiterplatten (Back-Drilling) und Stecker.

Der Zusammenhang zwischen gemessenen S-Parametern und vorausschauender Analyse für HF-Simulatoren stellte sicher, dass Zeitbereichssimulationen die Bitfehlerrate (BER) richtig einschätzen konnten. Mit Ethernet für Cloud-Computing und dem IoT stieg die Leitungsdatenrate von 56- auf 112-Gbit/s- PAM4, wodurch sich die Nyquist-Frequenz auf etwa 28 GHz verdoppelte, um 112-Gbit/s-PAM4 zu unterstützen. Der Schwerpunkt bei der Entwicklung lag dabei auf Impedanzübergängen entlang kürzerer Steckverbinderpfade und elektrischen Stichleitungen von circa 1 mm und länger. Gleichzeitig wurde die Anzahl der Kanäle von 16 auf 32 erhöht, wodurch sich der effektive Durchsatz bei gleichem Platzbe-darf verdoppelt hat.

Die Erhöhung der Dichte stand im Gegensatz zu Methoden, die Leitungen trennten, um das Rauschen zu reduzieren. Stattdessen wurden häufig Sender- und Empfängerpaare gruppiert, um die Auswirkungen der Nahkopplung zu verringern. Bei der selektiven Kanalgruppierung auf Leiterplatten werden unterschiedliche Schichten für Senden und Empfangen verwendet, um Rauschen zu reduzieren. Bei der Konstruktion von Steckverbindern werden absichtlich größere physische Abstände zwischen Sende- und Empfangspaaren vorgesehen.

In Entwicklungslaboren und Fertigungslinien kommen 67-GHz-VNAs zum Einsatz. Entwickler führen dabei Zeitbereichsanalysen mit Serienhalbleiterbausteinen durch. Daher hat sich die Signalintegritätstechnik zu einer eigenen Disziplin entwickelt.

Aktuelle Technik

Der Übergang von 112- zu 224-Gbit/s- PAM4 verdoppelt die Nyquist-Frequenz. Früher dauerten Geschwindigkeitsübergänge drei bis fünf Jahre. Jetzt gibt es 224-Gbit/s-PAM-Designs, bevor 112-Gbit/s-PAM4 überhaupt die Chance hatte, sich als Marktführer durchzusetzen. Entwickler im Bereich Signalintegrität sorgen sich jetzt über Stichleitungen, Unterbrechungen in der Übertragungsleitung und Öffnungen von 0,7 mm. Für Steckverbinder wird damit der Submillimeter-Bereich erreicht. Zum Vergleich: Der gesamte Kanal kann über 1 m lang sein, wobei jede Unstetigkeit physikalischer Übergänge zählt.

Die Wellenlängen sind inzwischen so kurz, dass typische Öffnungen/Resonanz-hohlräume ebenso wichtig sind wie der Signalpfad. Öffnungen, ob im Signal, im Rückweg oder zwischen Komponenten, sind zu einem kritischen Teil des Designs von Übertragungsleitungen geworden.

Design-Herausforderungen bei 224-Gbit/s-PAM4

Modell und Messung: Um besser zu verstehen, wie sich 224-Gbit/s-PAM4 auf das Design auswirkt, sollen die Herausforderungen der Signalintegrität in Bezug auf Korrelation, Ungleichgewicht der Übertragungsleitung und Versatz innerhalb eines Signalpaares betrachtet werden.

Das Einhalten der Entwicklungszeit (ein Schritt vor der Markteinführung) erfordert fortschrittliche analytische Vorhersagetechniken/-methoden. Es ist nicht immer möglich, die physikalischen Kanalzeiten zu erstellen und abzustimmen, bevor die entsprechenden Halbleiterbausteine eintreffen. Die Modelle müssen daher so genau wie möglich sein. Alle Abweichungen zwischen modellierten und vorhergesagten Korrelationen müssen verstanden werden, um die Zielvorgaben für die Entwicklungszeit zu erfüllen.

Im Frequenzbereich ist die Beseitigung von Fehlern auf Testplatinen entscheidend. Verbesserungen sind nötig bei Testgeräten, Testvorrichtungen, Kalibrierung und Testplatinen. Da diese Systeme oft bis zu 1 Million US-Dollar kosten, ist zu überlegen, was in der Fertigungsumgebung unbedingt erforderlich ist.

Zunehmend wichtiger wird, dass Messungen und Modelle mit dem Design übereinstimmen. Alle Fehler, die im Frequenzbereich liegen, machen sich im Zeitbereich bemerkbar. Bei Korrelationen zwischen Messung und Modell sollten die folgenden Szenarien berücksichtigt werden:

➔ Wenn die Messung schlechter ist als das Modell, wie reagiert man?

➔ Wenn die Messung besser ist als das Modell, was glaubt man?

➔ Was ist eine gute Korrelation? Innerhalb von 1 dB? Wenn ja, für welche Frequenzparameter?

➔ Wie wirken sich die einzelnen Frequenzbereichsparameter auf die Augenöffnung aus?

➔ Wie wirken sich die einzelnen Frequenzbereichsparameter auf die BER aus?

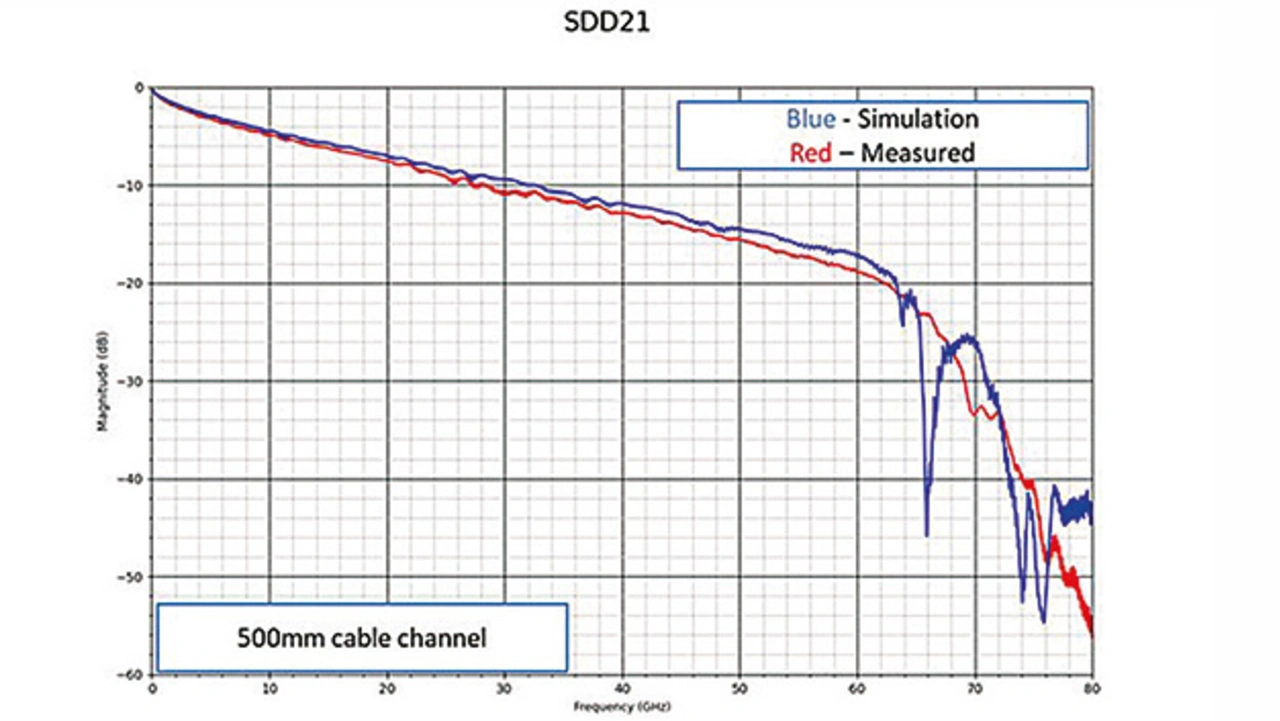

Als Beispiel soll ein Kanal dienen, bestehend aus einem Stecker, einer 500 mm langen Kabelbaugruppe und einem weiteren Stecker. In Bild 1 zeigt die rote Kurve (Messung) einen höheren Gesamtverlust, hat aber nicht die in der Simulation gezeigten Resonanzspitzen bei >60 GHz. Bei einem Nyquist-Wert von 56 GHz ist das vorteilhaft.

Leider kennt man im Vorhersagemodus die tatsächlichen Ergebnisse nicht. Wenn die Einfügungsdämpfung im Rahmen des Budgets liegt, sollte man sich damit dann zufrieden geben? Würden nur die Vorhersageergebnisse betrachtet, würde man Zeit darauf verwenden, die Resonanzspitze zu entfernen, obwohl es vielleicht besser gewesen wäre, sich auf die Verluste bei niedrigeren Frequenzen zu konzentrieren.

Frühzeitige Messungen verbessern den Fokus.

In diesem Beispiel hilft es, den Unterschied zwischen der Resonanzspitze (blau) und der sanften Abschwächung (rot) zu erkennen, um den tatsächlichen Kanal zu verstehen und somit die Zeit bis zum Design zu verkürzen. Der Unterschied in der Einfügungsdämpfung trägt zu einem besseren Verständnis der mit dem Breitbandverhalten verbundenen physikalischen Zusammenhänge bei.

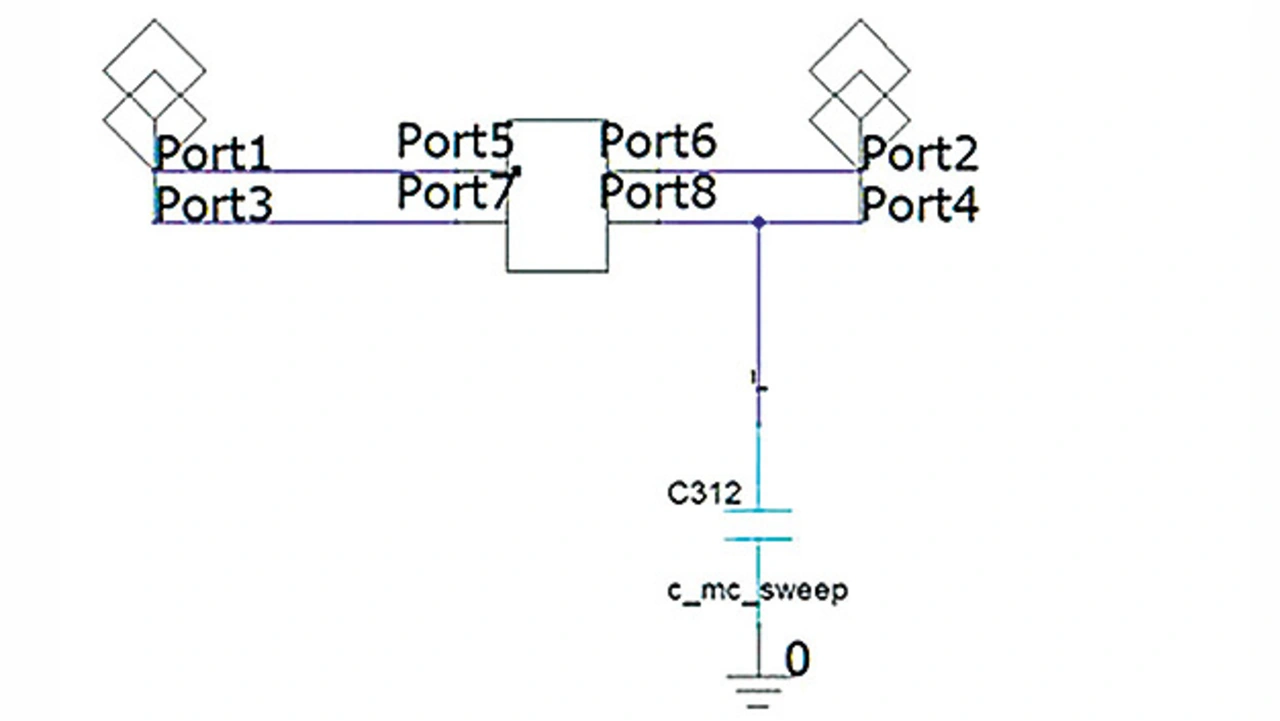

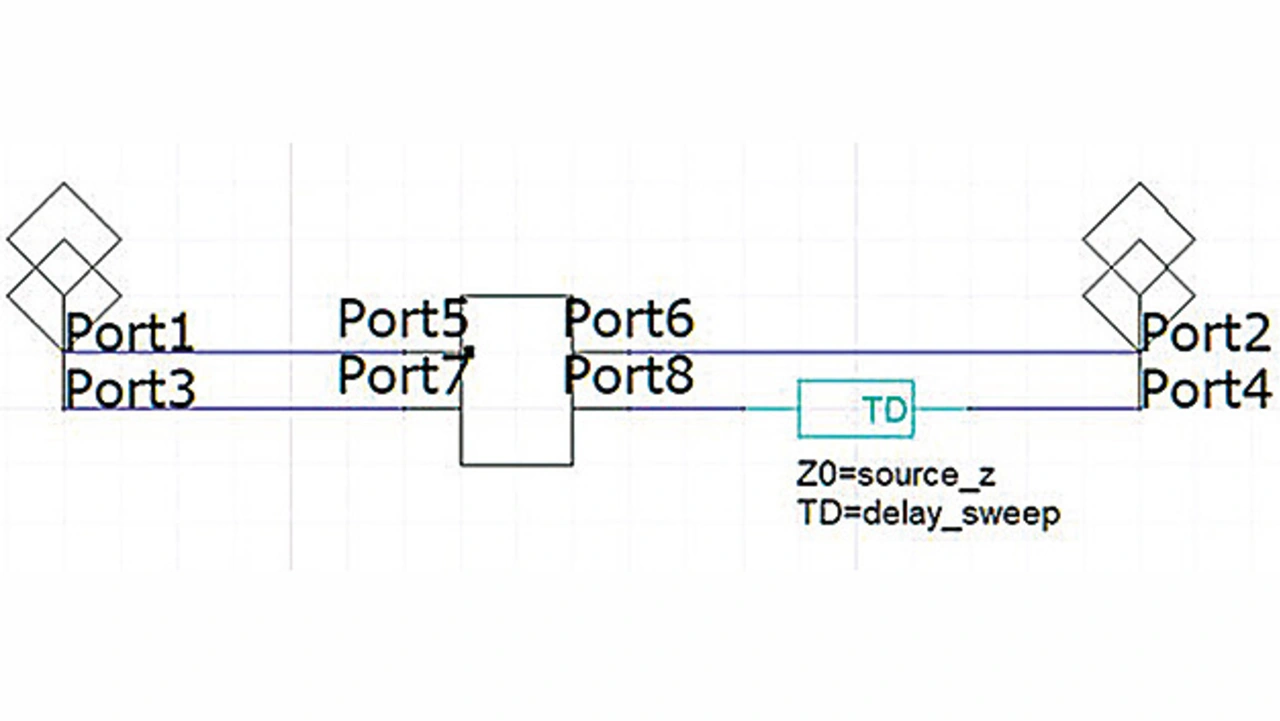

Unsymmetrie der Übertragungsleitung: Betrachtet man denselben 500-mm-Kanal wie im obigen Beispiel. Diesmal jedoch mit einer absichtlich hinzugefügten Störung (Bild 2). In der realen Welt könnte dies eine unangepasste Lötstelle zwischen den P- und N-Drähten darstellen. Der Kanal mit zwei Anschlüssen ist im mittleren S-Parameter-Block enthalten.

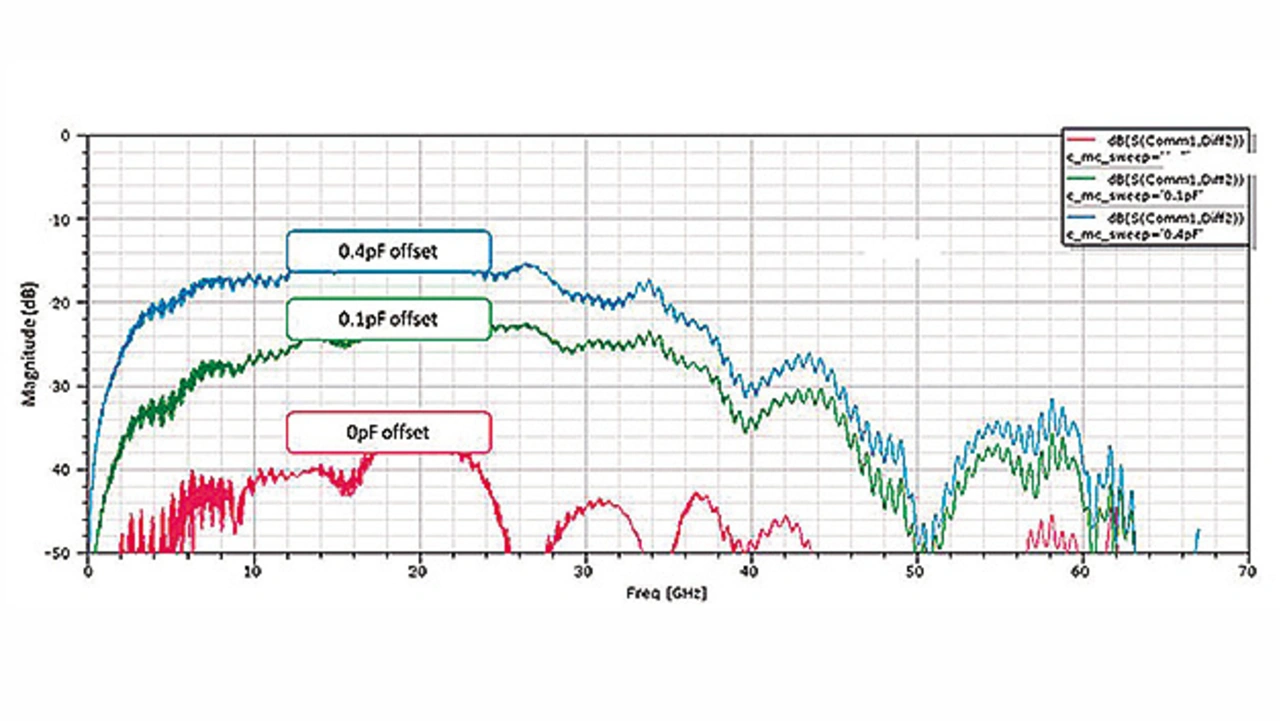

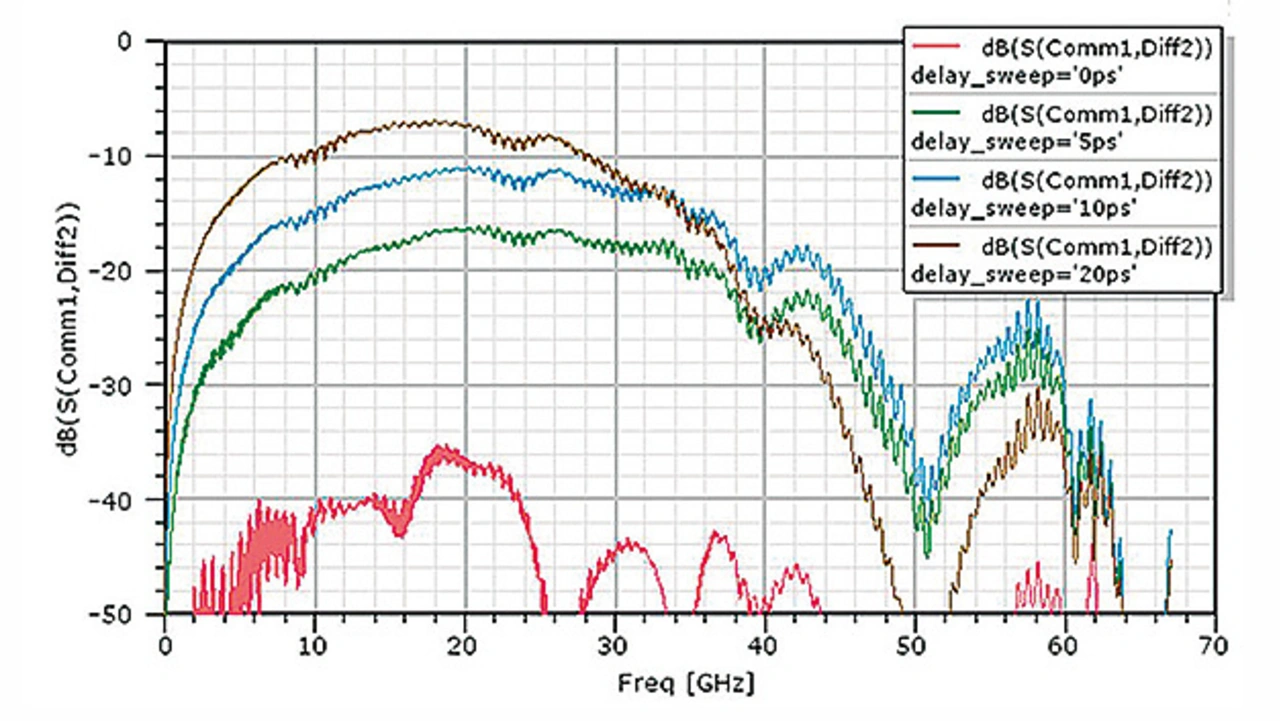

Ein schneller Durchlauf des Simulators zeigt eine Auswirkung auf die Modenumwandlung. Diese Änderung ist interessant, gibt aber nicht unbedingt Aufschluss über die tatsächlichen Auswirkungen auf die Systemleistung (Bild 3).

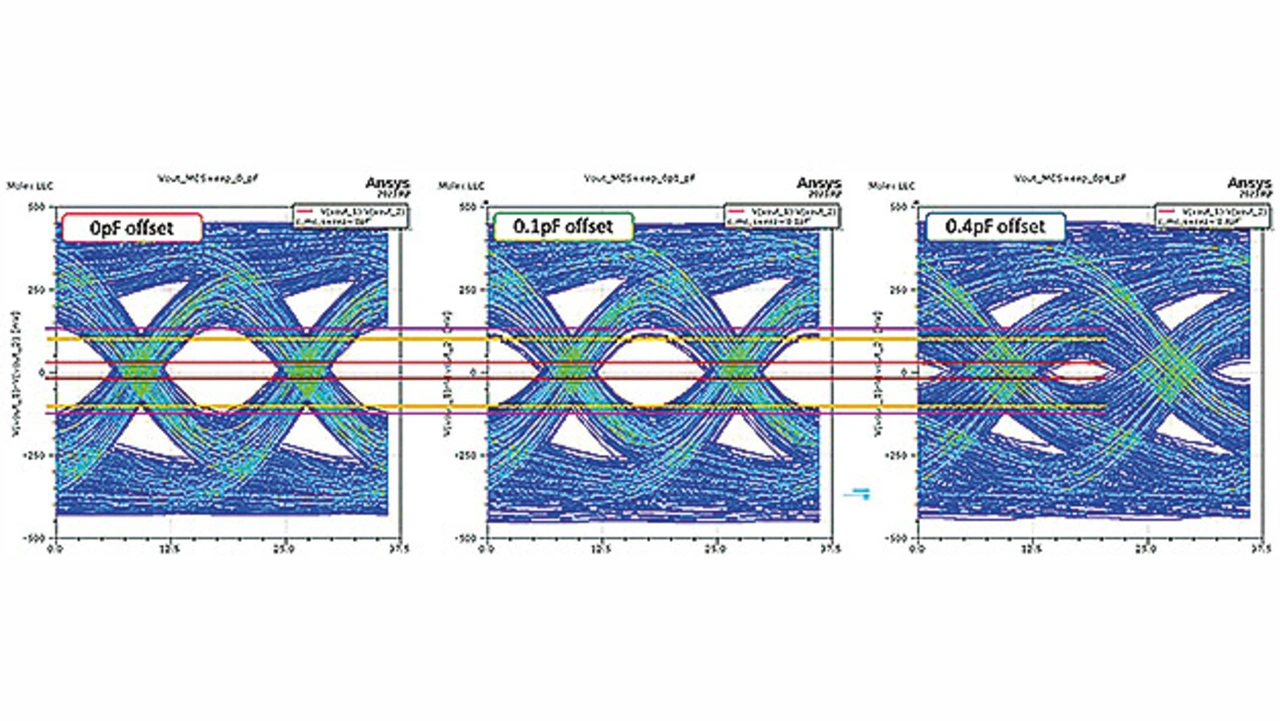

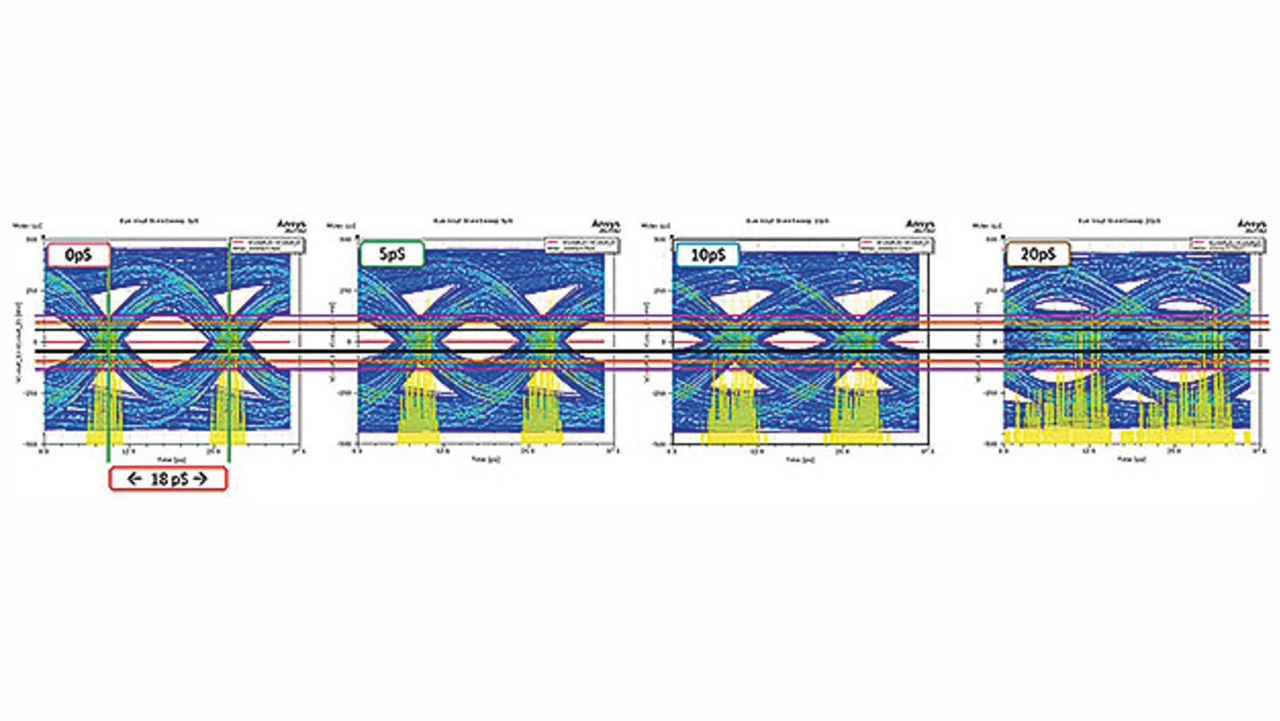

Als nächsten Schritt betrachtet man die Auswirkungen auf die Augendiagramme, die aus pseudozufälligen Binärsequenz-Bitströmen (PRBS) erzeugt werden. Da weder auf der Sende- noch auf der Empfangsseite eine Signalisierungskompensation erfolgt, zeigt sich hier ein interessanteres Bild (Bild 4).

Selbst bei einer Unsymmetrie von 0,1 pF sind die Augenöffnung reduziert, was zu einer geringeren Kanalmarge führt.

Versatz innerhalb eines Paares: Während der Designphase wird viel Zeit und Energie darauf verwendet, den Versatz von Übertragungsleitungen zu beseitigen. Versatz ist aus Gründen wichtig, die andere in der Branche hervorgehoben haben.

Der Kanal im folgenden Beispiel ist wie zuvor Pad-to-Pad, aber dieses Mal sind zwei Kabelbaugruppen mit einer Gesamtlänge von über 1 m miteinander verbunden. Dies ist ein Beispiel für einen Kanal mit drei Anschlüssen, bestehend aus einem Stecker, einer 200-mm-Kabelbaugruppe, einem Stecker, einer 500-mm-Kabelbaugruppe und einem weiteren Stecker.

Hier wurde auf einer der Leitungen eine verlustfreie Verzögerung hinzugefügt, die eine Beeinträchtigung des PCB-Versatzes darstellt (Bild 5). Die dreifache Steckverbindung ist im mittleren S-Parameter-Block enthalten.

Wird eine der Leitungen des differenziellen Paares etwas verlängert, stellen wir wiederum eine Auswirkung auf die Modenumwandlung fest (Bild 6). Wie zuvor ist die Änderung der Modenumwandlung interessant, zeigt aber möglicherweise nicht die tatsächlichen Auswirkungen auf die Systemleistung. Es fällt auf, dass sich diese Modenumwandlungen nicht sonderlich von der Unsymmetrie der Übertragungsleitung unterscheiden.

Die Diagramme in Bild 7 zeigen, dass der Wechsel vom idealen Kanal zu einem Kanal mit einem anderen Versatz Auswirkungen auf das Augendiagramm hat. Aus Sicht der Datenintegrität ist selbst bei einer Verzögerung von 5 ps eine kleinere Augenöffnung festzustellen, was zu einer geringeren Kanalmarge führt.

Wichtige Erkenntnis: Das Schließen des Auges im Zeitbereich und die Modenumwandlung im Frequenzbereich können ähnliche Reaktionen aufweisen, die durch unterschiedliche Abweichungen verursacht werden. Man sollte auf geringfügige Design- und Prozessabweichungen achten, wenn die Laborergebnisse des Frequenzbereichs im Zeitbereich bewertet werden sollen.

Tipps für 224-Gbit/s-PAM4-Designs

Ein funktionsübergreifender Designansatz ist am besten: Systementwickler, die mit Kabel-/Stecker- und Halbleiterteams zusammenarbeiten, finden den richtigen Kanal am schnellsten. Die Teams müssen frühzeitig in den Kanal-Entwicklungsprozess eingebunden werden, um erweiterbare und skalierbare Architekturen bereitzustellen. Wichtige Rollen dabei sind: Hardwareentwicklung, Systemarchitektur, Signalintegrität, mechanische und thermische Integrität.

Zuerst die Leistungsziele und dann die Spezifikationen definieren: Beginnen Sie mit Zielvorgaben, die den Beteiligten die Möglichkeit geben, gemeinsam Betriebsbudgets zu entwickeln, die später in Komponenten aufgeteilt werden. Seien Sie bei den Margen transparent. Die Spezifikationen ergeben sich dann aus dem betriebsbereiten Prototyp und den korrelierten Modellen.

Zusammenhänge bestätigen: Stellen Sie sicher, dass es einen Zusammenhang zwischen Modell und Messung für die S-Parameter und den Zeitbereich gibt. Man muss verstehen, wie sich die Parameter des Frequenzbereichs auf die Ergebnisse im Zeitbereichs auswirken.

Anwendungen erfordern Signalintegrität und mechanische Integrität: Auch wenn die Signalanforderungen immer kritischer werden, nehmen die Anforderungen an die Signaldichte (differenzielle Paare pro Fläche) zwischen den Generationen weiter zu. Damit ist mehr Entwicklungsaufwand für mechanische Parameter wie Normalkräfte, Robustheit und Wischfestigkeit erforderlich. Alle diese Faktoren sind mit dem Formfaktor der Anwendung (Servergehäuse und Kühlung) verknüpft. Kleine Abweichungen vom vorgesehenen Design können die Kanalmarge verringern.

Der Autor

Augusto Panella

ist Director Interconnect Technology bei Molex.