3D-Power-Packaging für PoL-Wandler

Power-Module folgen dem Moore‘schen Gesetz

Über Jahrzehnte folgten Prozessoren und komplexe ICs dem Moore‘schen Gesetz. Die zugehörigen Spannungsregler schrumpften jedoch bis vor Kurzem nicht im gleichen Maße. Eine neue Wandlergeneration, die mit 3D-Packaging-Techniken produziert sind, zeigt enorme Verbesserungen bei der Leistungsdichte.

Als Gordon Moore, Mitbegründer von Fairchild und Intel, 1965 in der populären Zeitschrift »Electronics« seine Prognose veröffentlichte, dass sich die Anzahl der Transistoren in einem komplexen IC von Jahr zu Jahr ungefähr verdoppeln würde, tat er dies mit einem Prognosezeitraum von zehn Jahren. Seine Vorhersage, die als Moore‘sches Gesetz bekannt wurde, lautete, dass sich ausgehend von etwa 50 Komponenten in einem IC im Jahr 1965 bis 1975 voraussichtlich rund 65.000 auf einem 6 mm × 6 mm großen Chip Platz befinden würden.

Seine Vorhersage traf ein, denn der Intel 8086, der 1976 auf den Markt kam, verfügte über 29.000 Transistoren bei einem Prozessmaßstab von 3,2 µm. Moore revidierte dann seine Schätzung auf eine Verdoppelung alle zwei Jahre. Heute hat sich der Anstieg der Komplexität zwar verlangsamt, aber TSMC strebt für 2025 einen Maßstab von 2 nm an, was eine erstaunliche Reduzierung der Chipgröße um den Faktor 1600 bedeutet.

Ab 2022 wird die höchste Transistoranzahl in einem kommerziell erhältlichen Mikroprozessor, und zwar in Apples Arm-basiertem Dual-Die-System M1 Ultra, das in einem 5-nm-Prozess hergestellt wird, 114 Milliarden betragen. Dieses »System on a Chip« besteht aus zwei Chips mit einer Fläche von jeweils 420 mm2. Prozessinnovationen wie 3D-Transistoren und »Die-Stacking« haben dafür gesorgt, dass sich die Rechenleistung pro mm2 Grundfläche auf einem ähnlichen exponentiellen Kurs befindet (Bild 1).

Komplexität,

aber auch Stromverbrauch gestiegen

Allerdings ist der Strombedarf von Prozessoren und jetzt auch SoCs nicht im gleichen Maße gestiegen wie die Anzahl der Transistoren, weil die Kapazitäten der Geräte mit abnehmender Transistorgröße sinken. Dies führt zu geringeren dynamischen Verlusten und einer niedrigeren Stromaufnahme. Zudem hat die Verkleinerung dazu geführt, dass Versorgungsschienen mit niedrigerer Spannung verwendet werden, um Ausfälle zu vermeiden. Dies hat ebenfalls zu einer geringeren Leistungsaufnahme beigetragen. Dennoch ist die Leistungsaufnahme von etwa 1 W beim Intel 4004 auf 150 W oder mehr bei den neuesten Bauteilen gestiegen, und die Stromaufnahme erhöhte sich von 67 mA auf etwa 150 A, was einem Faktor von 2200 entspricht.

Durch den drastischen Anstieg des Stromverbrauchs ist es notwendig geworden, dass die erforderlichen Spannungsregler sehr nahe am Prozessor angebracht werden, um übermäßige Spannungsabfälle zu vermeiden und die geforderten hohen Spitzenströme zu liefern, was eine Herausforderung für die Stromversorgungsdesigner darstellt. Als Moore 1965 seinen Artikel schrieb, hatte ein 150-W-DC/DC-Wandler die Größe und das Gewicht eines Ziegelsteins, und selbst mit der neu erfundenen Schaltnetzteiltechnik wären die Verluste hoch gewesen.

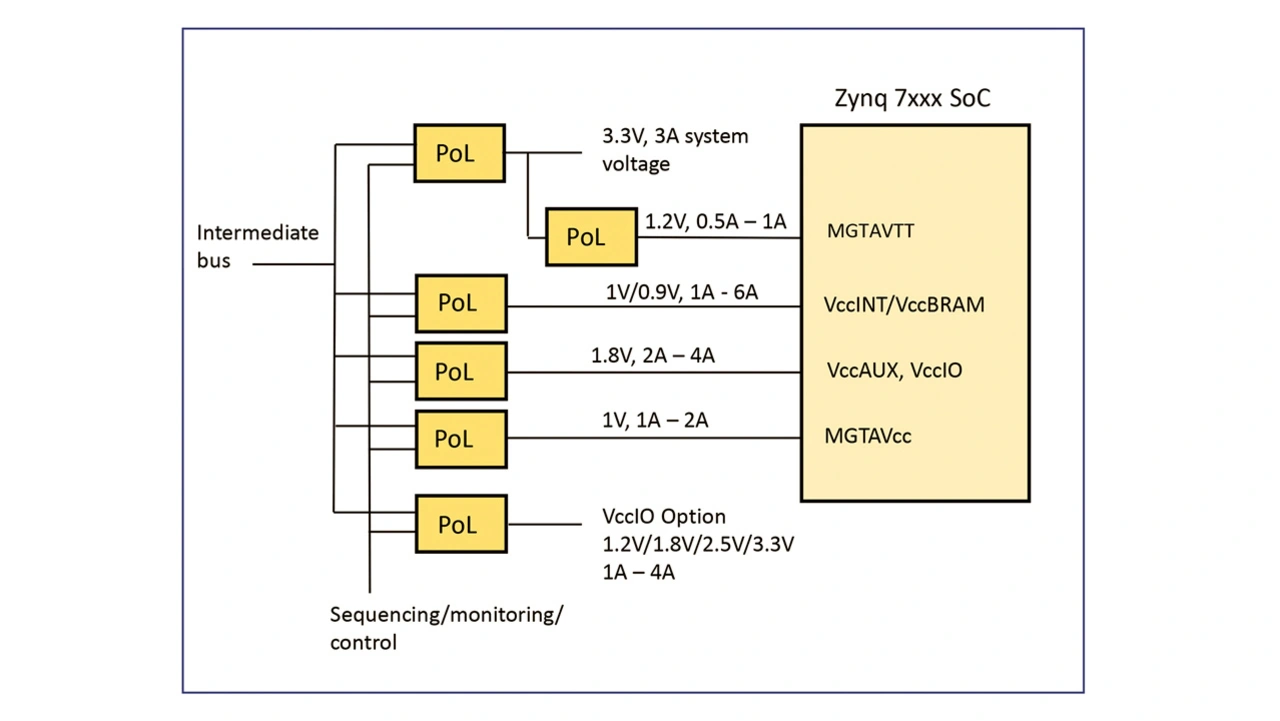

Zwar hat sich der Wirkungsgrad im Laufe der Zeit durch Techniken wie etwa die synchrone Gleichrichtung und bessere Halbleiter verbessert, aber bis vor Kurzem war ein leistungsstarker DC/DC-Wandler für den »Point of Load« (PoL) sehr groß. Im Allgemeinen griffen die Modulhersteller dabei auf vertikale SIP- und unbequeme Through-Hole-Formate zurück, um Platz auf der Platine zu sparen, was auf Kosten der Höhe und des Luftstroms ging. Prozessoren und komplexe ICs wie ASICs und FPGAs benötigen mehrere Spannungsschienen, allerdings in der Regel mit geringerer Leistung. So benötigt der Zynq 7000 von Xilinx beispielsweise fünf Schienen, die typischerweise von 1 bis 3,3 V reichen (Bild 2).

Topologien der PoL-Wandler

haben sich nicht geändert

Im Prinzip haben sich die in PoL-Wandlern verwendeten Umwandlungstopologien über mehrere Jahrzehnte hinweg kaum verändert. Es werden Buck-, Boost- und Buck-Boost-Schaltungen verwendet, die nach wie vor einen Halbleiterschalter, eine Diode oder einen Synchronwandler, eine Induktivität und einen Kondensator mit Pulsbreiten- oder Frequenzmodulation zur Regelung einsetzen. Die Schalter wurden so weiterentwickelt, dass sie geringere statische und dynamische Verluste aufweisen und mit höheren Frequenzen arbeiten. Auch die Materialien der Induktionskerne und Kondensatoren wurden schrittweise verbessert, um die Verluste zu verringern. Infolgedessen hat sich der Wirkungsgrad erhöht, was wiederum eine bessere Leistungsdichte ermöglicht hat – PoL-Wandler konnten sich bei gleicher Last und Temperaturerhöhung verkleinern. Aber: Der Nutzen ist nicht dem Moore‘schen Gesetz gefolgt, und so machen Leistungswandler nach wie vor einen großen Teil der genutzten Platinenfläche aus.

Ein Teil des Problems mit der Größe des PoL-Wandlers besteht darin, dass traditionell diskrete Komponenten auf einem Substrat mit geringer Integration verwendet wurden. Dies ergibt sich aus der einfachen Tatsache, dass es sich um Leistungswandler handelt, die unweigerlich Wärme abführen, sodass große Komponenten erforderlich waren, um den Temperaturanstieg gering zu halten. Außerdem ist es schwierig, die Spule und ihren Kern nicht nur als sperriges diskretes Bauteil herzustellen, und die Ferritkerntechnologie hat sich über die Jahrzehnte nur in kleinen Schritten verbessert.

Konkret bedeutet dies, dass eine minimale Anzahl von Spulenwindungen erforderlich ist, die zudem dick genug sein müssen, um den höheren Strömen ohne Überhitzung standzuhalten. Konsequenz dessen ist ein sperriges Bauteil. Zwar sinkt die Anzahl der erforderlichen Windungen mit steigender Schaltfrequenz bei gleicher Kernflussdichte und Ausgangsrestwelligkeit, aber umgekehrt steigen die Schaltverluste des Kerns und des PoL-Wandlers, sodass ohnehin ein größerer PoL erforderlich ist, um die Wärme abzuführen. All dies bedeutet, dass die Verkleinerung von PoL-Wandlern im Gegensatz zu Prozessoren direkt zu thermischen Problemen führt und die Gesamtgewinne begrenzt.

- Power-Module folgen dem Moore‘schen Gesetz

- DC/DC-Wandler müssen IC-ähnlich werden

- Leistungsmodule für alle Anwendungen