Tipps für einphasige Buck-Controller

Grenzen überwinden

Fortsetzung des Artikels von Teil 1

Grenzstrom des internen Reglers

Diese häufig übersehene Spezifikation wandert langsam in den roten Bereich, wenn bei parallelgeschalteten FETs mit hohen Schaltfrequenzen gearbeitet wird. Der vom internen Regler gezogene Strom lässt sich mit Gleichung 1 berechnen:

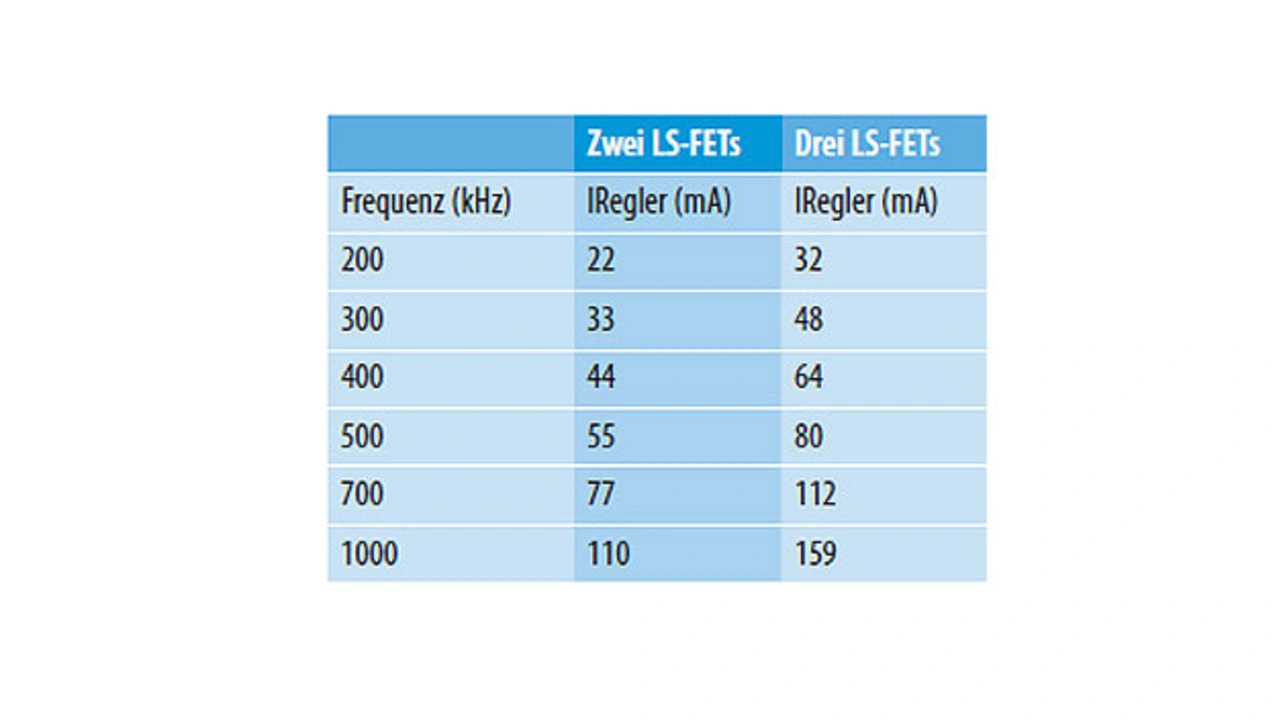

Darin sind Qg_HS und Qg_LS die Gesamt-Gate-Ladungen des High-Side- bzw. des Low-Side-FET vom Ursprung bis zu dem Punkt, an dem die Gate-Spannung gleich der Treiberspannung ist. Tabelle 2 gibt an, welche Ströme in Konfiguration 2 bei verschiedenen Frequenzen gezogen werden. Der VDD-Grenzstrom für den LM27402 ist 106 mA (typ.).

Um konservativ vorzugehen, wird die Grenze um 20 % niedriger, also bei 85 mA angesetzt. Controller, die für hohe Ströme geeignet sind, weisen einen hohen Grenzstrom für den Regler auf. Beispiele sind der TPS53819A (152 mA) und der TPS40400 (100 mA).

Spannung des internen Reglers

Ist die Spannung des internen Reglers höher, können die besten RDS(on)-Werte für die FETs erzielt werden. Die Schaltzeit und somit auch die Schaltverluste werden ebenfalls beeinflusst.

Mit Gleichung 2 lässt sich die zum Ansteuern eines FET verfügbare Gate-Spannung berechnen:

Darin ist Ugate die Ausgangsspannung des Gate-Treibers und UGS die Miller-Spannung. Mit Gleichung 3 lässt sich der zum Ansteuern des FET verfügbare Strom berechnen:

Darin ist Rdrive der Pull-up-Widerstand des Treibers und Rgate der Gate-Widerstand des FET. Gleichung 4 dient zum Berechnen der Schaltzeit, die der Strom zum Ansteigen benötigt:

Hier handelt es sich bei Qgd_Miller um die Ladung, die während der Zeit, in der sich der Baustein auf dem Miller-Plateau befindet, in das FET-Gate injiziert wird.

Gleichung 5 dient zur Berechnung der Übergangsverluste, die während der Übergangszeit ttrans entstehen:

Darin handelt es sich bei UIN um die Eingangsspannung, bei IOUT um den Ausgangsstrom, bei fSW um die Schaltfrequenz.

Pull-up-Widerstand

Ein niedrigerer Wert für den Pull-up-Widerstand des HS-FET (gemäß Gleichung 3) führt zu einem höheren Gate-Strom und kürzeren Übergangszeiten, was wiederum die Schaltverluste senkt. Für hohe Ströme ausgelegte Controller besitzen einen Pull-up-Widerstand von 1,5 Ω oder weniger. In einigen Datenblättern oder Auswahlhilfen ist die Angabe des maximalen Stroms zur Ansteuerung des Gates hervorgehoben. Das kann jedoch irreführend sein, da die maximalen Ströme beim Berechnen der Übergangszeiten wie in Gleichung 4 nicht berücksichtigt werden.

Überlegungen zum Tastverhältnis

Es ist sinnvoll, das vom Controller unterstützte maximale und minimale Tastverhältnis daraufhin zu überprüfen, ob es den Anforderungen des Designs gerecht wird.

Für Beispiel 2 gilt: UIN = 12 V, UOUT = 10 V, IOUT = 50 A.

Zunächst einmal wird ein Controller benötigt, der ein Tastverhältnis von 83 % unterstützt. Der LM27403 erfüllt dieses Kriterium. Angesichts des großen Tastverhältnisses muss ein HS-FET mit niedrigem RDS(on) gewählt werden. Leider weist ein FET mit niedrigem RDS(on) typischerweise einen höheren Qgd-Wert auf, was höhere Schaltverluste nach sich zieht. Wenn gute FETs verfügbar sind, wird dieser Einfluss allerdings abgemildert. Im vorliegenden Fall wurde der TPHR9003NL gewählt, der sich durch eine geringe Gate-Ladung auszeichnet. Das große Tastverhältnis verlangt außerdem, dass den Verlusten des HS-FET besondere Aufmerksamkeit gewidmet wird. Wegen des hohen Stroms und des großen Tastverhältnisses wurden zwei FETs parallelgeschaltet, wobei die Auswirkungen der Parallelschaltung durch die Wahl einer Schaltfrequenz von 200 kHz minimiert werden. Die Verwendung zweier HS-FETs des Typs TPHR9003NL und eines LS-FET vom Typ TPHR9003NL ergibt die folgenden Leitungs- und Schaltverluste:

- Leitungsverlust der HS-FETs: 1,16 W, Schaltverlust = 3,6 W; Gesamtverlust: 4,85 W

- Leitungsverlust des LS-FET: 0,48 W, Schaltverlust = 0,071 W; Gesamtverlust: 0,55 W

Da zwei parallelgeschaltete HS-FETs zum Einsatz kommen, muss der Gesamtverlust zur Berechnung des Temperaturanstiegs durch zwei dividiert werden:

- Temperaturanstieg der HS-FETs: 2,425 W × 44,6 °C/W = 108 °C

- Temperaturanstieg des LS-FET: 0,55 W × 44,6 °C/W = 25 °C

Liegt hierbei die maximale Sperrschichttemperatur der FETs von 150 °C zugrunde, ergibt sich eine maximale Umgebungstemperatur von etwa 40 °C. Um den zulässigen Temperaturbereich zu vergrößern, benötigen die HS-FETs eine Zwangsbelüftung und/oder Kühlkörper. Die Belüftung senkt den θJA-Wert und begrenzt den Temperaturanstieg der HS-FETs auf etwa 50 °C. Der Wirkungsgrad des Designs von 97,88 % zeigt, warum Angaben zum Wirkungsgrad irreführend sein können: Auch bei einem hohen Wirkungsgrad können die in den HS-FETs entstehenden Verluste zu einer Erwärmung führen, die eine Zwangsbelüftung erforderlich macht.

Das Parallelschalten von mehr FETs trägt zur Senkung der Leitungsverluste bei, jedoch führt das Hinzufügen von mehr parallelgeschalteten Kondensatoren zu höheren Schaltverlusten. Zum Beispiel ergibt eine Parallelschaltung aus drei HS-FETs vom Typ TPHR9003NL folgende Verlustrechnung:

- Leitungsverlust der HS-FETs: 0,77 W, Schaltverlust = 5,53 W; Gesamtverlust: 6,3 W

Damit entfiele auf jeden FET ein Verlust von 2,1 W. Zwar stellt das gegenüber den 2,425 W bei Verwendung zweier FETs eine Verbesserung dar, aber zum Erzielen eines Designs, das über einen weiten Temperaturbereich zuverlässig ist, wäre ein Reduzieren des θJA-Werts per Zwangsbelüftung die bessere Wahl. Auch ein niedrigerer Pull-up-Widerstand des Treibers (Rdrive) würde dazu beitragen, die Schaltverluste zu senken.

Der Autor

Mathew Jacob

ist Anwendungstechniker bei Texas Instruments. In den Teams für Produktdefinition und Systemanwendung war er bereits in verschiedenen Positionen tätig. Jacob hat einen Bachelor-Abschluss in Elektronik und Nachrichtentechnik von der Madurai Kamaraj University in Indien.

- Grenzen überwinden

- Grenzstrom des internen Reglers