DESIGN-Praxis

Schlüsselwortsuche auf Mikrocontrollern

Fortsetzung des Artikels von Teil 5

Ressourcenbeschränkte NN-Architektur-Exploration

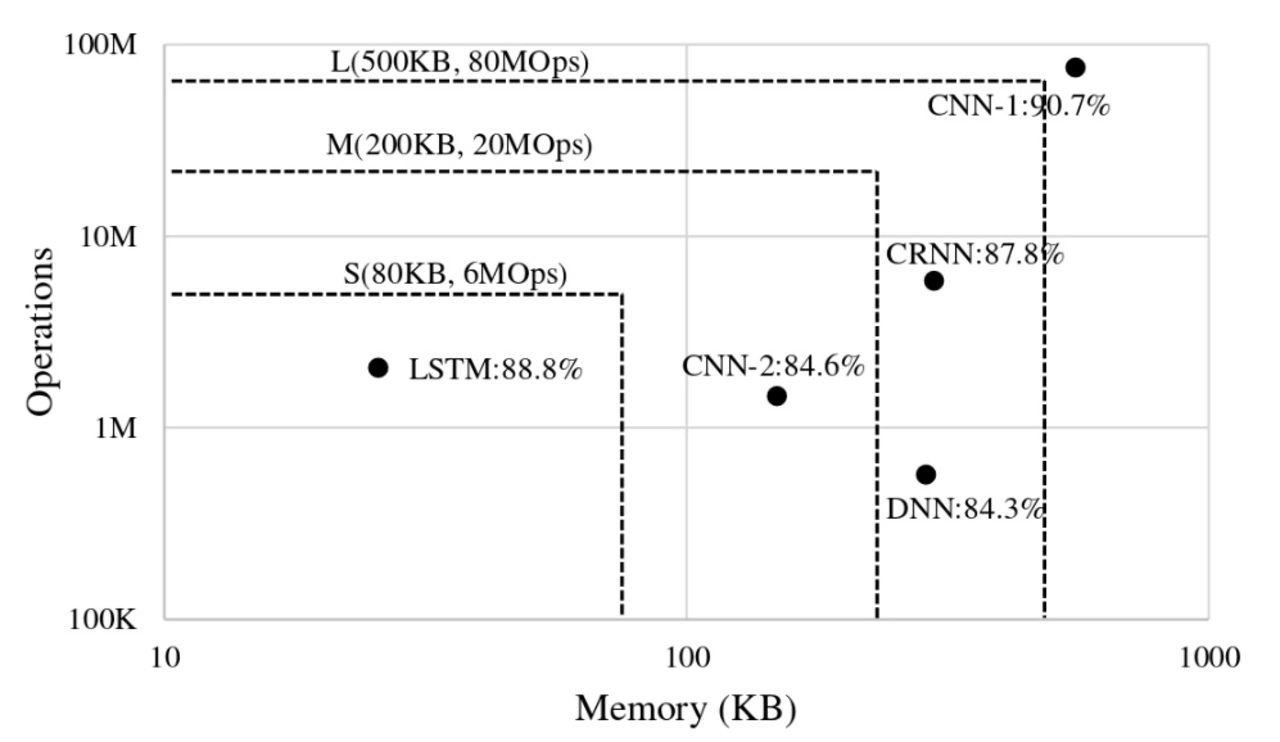

Bild 5 zeigt die Operationsanzahl pro Folgerung, Speicheranforderungen und Trefferanzahl der Netzwerkmodelle einer früheren Arbeit auf der Google-Sprachkommandobasis. Dabei wurden die Begrenzungsboxen nach Tabelle 3 eingezeichnet. Eine ideale Implementierung besitzt eine hohe Trefferrate, niedrigen Speicher- und Rechenbedarf, befindet sich also nah am Koordinatenursprung des Rechtecks.

Außer der LSTM-Modelle passt kein Weiteres in die Region S mit 80 KB/ 6 MOps. CNN-2, CRNN und DNN passen in M und L, weisen aber geringere Trefferwahrscheinlichkeiten als CNN-1 auf, das außerhalb der Klassifizierung liegt.

Jobangebote+ passend zum Thema

Wie Bild 1 zeigt wird jedes Eingangssignal in TxF Merkmale zerlegt.

Ihre Anzahl beeinflußt Modellgröße, Rechenzeit und Trefferrate. Die Schlüsselparameter dafür sind die Anzahl der MFCC-Merkmale pro Intervall (F) und Versatz (s).

Die Anzahl der Merkmale pro Audiointervall bestimmt die Anzahl der Gewichte in voll-verbundenen und rekursiven Ebenen, aber nicht in den Faltungsebenen, da die Gewichte dort wiederverwendet werden.

Die Versatzzeit (s) bestimmt die Anzahl der pro Folgerung verarbeiteten Intervalle (T). F und S bestimmen damit die Operationsanzahl pro Folgerung. Ein effizientes Netzwerk maximiert somit die Trefferrate unter Minimierung von TxF, bei kleinem F und/oder großem s.

Die NN-Architekturen und ihre Hyperparameter zeigt Tabelle 4. Das LSTM-Modell in der Tabelle beinhaltet dabei Schlüssellochverbindungen und Ausgangprojektionsebenen, aber keine LSTM-Modelle. CRNN nutzt eine Faltungsebene im Anschluss an eine GRU. Auch werden die Faltungs-/vollvernetzten und rekursiven Ebenen normiert. Während der Folgerung können die Normierungsparameter in die Gewichte der Faltungsebenen einbezogen werden. Daher tragen diese Schichten nicht zur Rechenzeit bei.

| NN | Hyperparameter |

|---|---|

| DNN | Anzahl und Größe der vollverbundenen Schichten |

| CNN | Anzahl der Faltungsebenen: Merkmale/Kernelgröße/Streckenlänge, Linear-Ebenen-Dimension, VV-Ebenen-Größe |

| Basic LSTM | Anzahl der Gedächtniszellen |

| LSTM | Anzahl der Gedächtniszellen, projizierte Speichergröße |

| GRU | Anzahl der Speicherzellen |

| CRNN | Faltungsmerkmale/Kernelgröße/Streckenlänge, GRU-Anzahl und Gedächtniszelle, VV-Größe |

| DS-CNN | Anzahl der DS-Faltungsebenen, DS-Faltungs-Merkmale / Kernelgröße / Streckenlänge |

Tabelle 4: NN-Hyperparameter

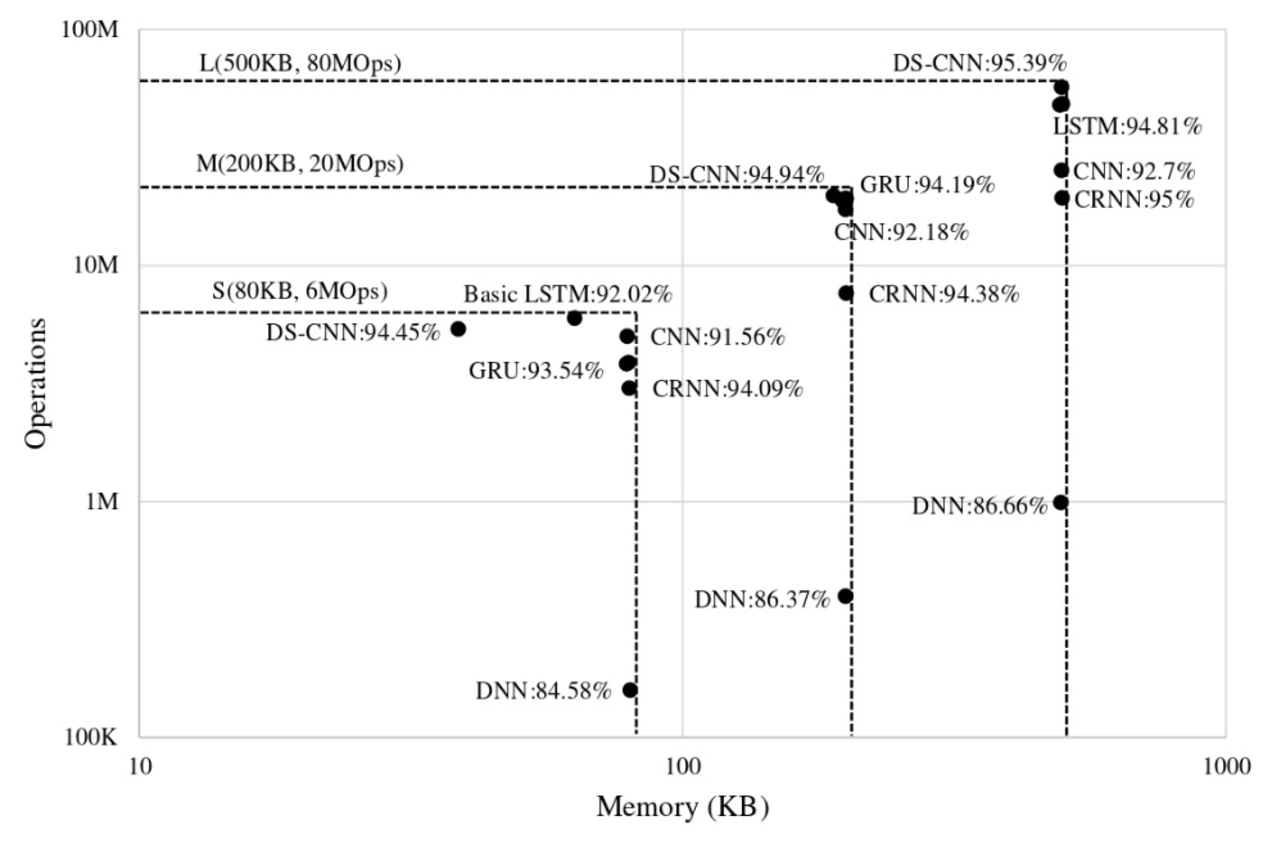

Eine Exploration des Hyperparameterraumes dieser Modelle führt zum Vergleich der jeweils besten Implementierungen:

| NN | S(80 Kb, 6 MOps) | M(200 Kb, 20 MOps) | L(500 Kb, 80 MOps) |

|---|---|---|---|

| Acc | Mem | Ops | Acc | Mem | Ops | Acc | Mem | Ops | |

| DNN | 84,6%|80 Kb|158,8K | 86,4%|199,4 Kb|397,0K | 86,7%|496,6 Kb|990,2K |

| CNN | 91,6%|79,0 Kb|5,0M | 92,2%|199,4 Kb|17,3M | 92,7%|497,8 Kb|25,3M |

| Basic LSTM | 92,0%|63,3 Kb|5,9M | 93,0%|196,5 Kb|18,9M | 93,4%|494,5 Kb|47,9M |

| GRU | 93,5%|78,8 Kb|3,8M | 94,2%|200,0 Kb|19,2M | 94,7%|499,7 Kb|48,4M |

| CRNN | 94,0%|79,7 Kb|3,0M | 94,4%|199,8 Kb|7,6M | 95,0%|499,5 Kb|19,3M |

| DS-CNN | 94,4%|38,6 Kb|5,4M | 94,9%|189,2 Kb|19,8M | 95,4%|497,6 Kb|56,9M |

Tabelle 5: Die besten NNs aus der Hyperparametersuche. Die Tabelle zeigt den Speicherbedarf bei 8-bit-Gewichten.

| NN-Modell | 32-bit floating point | 8-bit quantisiert |

|---|---|---|

| Train | Val. | Test | Train | Val. | Test | |

| DNN | 97,77% | 88,04% | 86,66% | 97,99% | 88,91% | 87,60% |

| BASIC LSTM | 98,38% | 92,69% | 93,41% | 98,21% | 92,53% | 93,51% |

| GRU | 99,23% | 93,92% | 94,68% | 99,21% | 93,66% | 94,68% |

| CRNN | 98,34% | 93,99% | 95,00% | 98,43% | 94,08% | 95,03% |

Tabelle 6: Trefferraten bei 8-bit-Quantisierung und voll-präzisen Netzwerken

DNNs sind speicherzentriert und erzielen geringere Trefferraten die gegen 87% konvergieren. CNNs erzielen höhere Trefferraten sind aber durch die Gewichte der vollverbundenen Schichten beschränkt. RNNs (i.e. Basic LSTM, LSTM, GRU) erzielen höhere Trefferraten als CNNs, weisen geringere Modellgrößen und Rechenoperationen auf und beweisen, dass die Trefferwahrscheinlichkeit unter Ausnutzung der Zeitkorrelation ohne zusätzliche Ressourcen erhöht werden kann.

CRNNs erzielen in der Kombination der Vorteile beider Methoden noch höhere Trefferwahrscheinlichkeiten bei weniger Rechenschritten. Die DS-CNN-Architektur erzielt die höchsten Trefferraten und zeigt gute Skalierungseigenschaften, die auf ihre tiefe Architektur mit stufenweise separablen Faltungsebenen, zurückgeht.

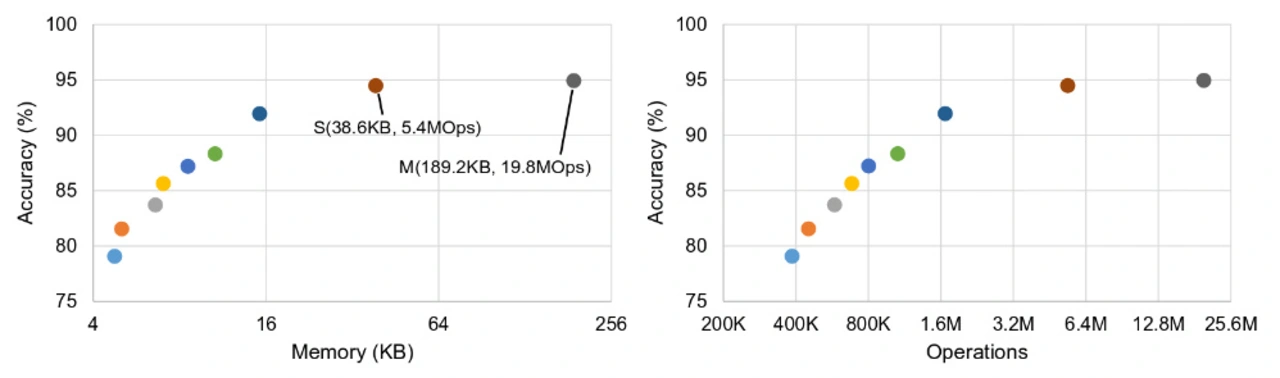

Um die Skalierbarkeit solcher Modelle für kleinere Mikrocontrollersysteme mit weniger als 8 Kb Speicher zu studieren, wird der Explorationsraum für das DS-CNN-Modell erweitert. Bild 7 zeigt die Trefferrate, Speicher-/Rechenanforderungen bei diesen ressourcenbeschränkten Geräten. Diese nach unten skalierten DS-CNNs erzielen höhere Trefferraten als DNNs bei gleicher Operationszahl aber mindestens 10-facher Speicherauslastung.

DUT

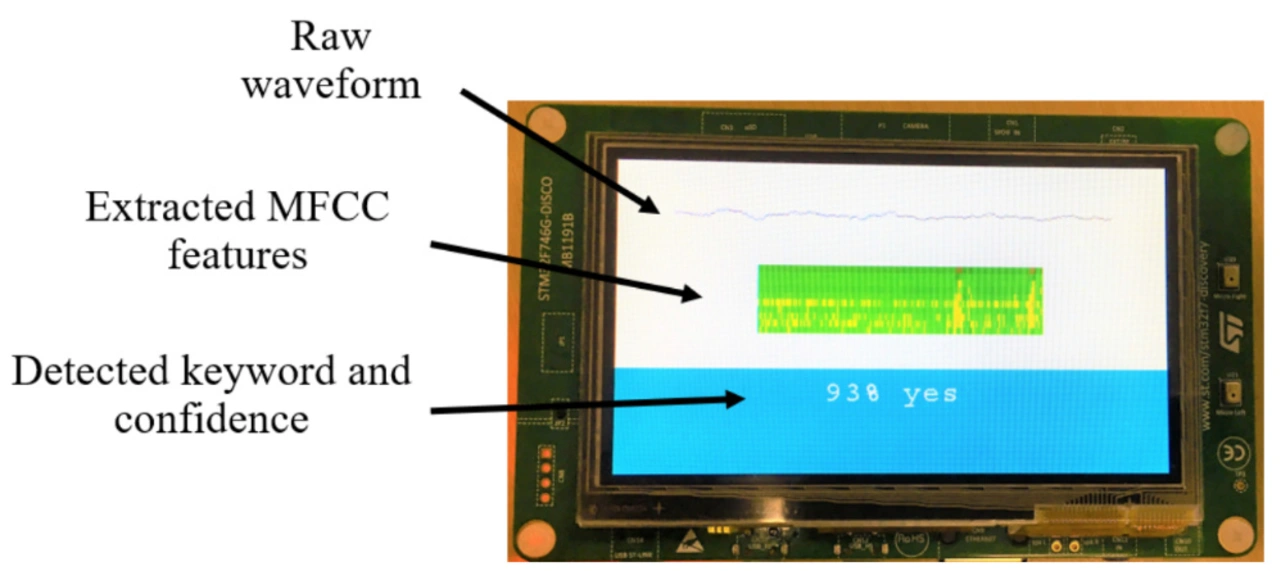

Die Schlüsselwortsuche wurde auf einem Cortex-M7-basierten STM32F746G-DISCO-DevKit mit CMSIS-NN-Kernels getestet (Bild 8). Das DNN-Model nutze dabei 8-bit-Gewichte und Aktivierungsfunktionen. Die Schlüsselwortsuche zieht zehn Folgerungen pro Sekunde. Jede Folgerung, einschließlich des Speicherzugriffes, Merkmalsextraktion und DNN-Ausführung dauert 12 ms. Der Mikrocontroller kann zur Steigerung der Energieeffizienz in den WFI-Modus geschaltet werden.

Die Schlüsselwortsuche belegt über 70 Kb Speicher, einschließlich 66-Kb-Gewicht, 1 Kb für die Aktivierungsfunktionen und 2 Kb für Audio-I/O und MFCC-Extraktion.

Fazit

Hardware-optimierte Neuronale-Netzwerk-Architektur ist ein Schlüssel um effiziente Ergebnisse auf Speicher- und Rechenleistungsbeschränkten Mikrocontrollern zu erlangen. Verschiedene Neuronale Netze zur Schlüsselwortsuche auf Mikrocontrollern wurden zum Vergleich ihrer Trefferraten und Ressourcenanforderungen pro Folgerung auf der Google-Sprachkommando-Basis trainiert. Diese 32-bit-floating-point Modelle wurden in 8-bit-fixed-point-Versionen konvertiert, ohne einen Verlust der Trefferrate oder Notwendigkeit einer neuen Trainingsphase. Weiterhin wurde ein durch Google MobileNet inspiriertes neues DS-CNN-Modell trainiert.

Auf Basis eines generischen Mikrocontrollersystems können die Speicher-/Ressourcenschranken in drei Klassen unterteilt werden. Stufenweise separable CNNs erzielen in jeder Klasse die höchste Trefferwahrscheinlichkeit und sind damit am skalierbarsten.

Code, Modelldefinition und vortrainierte Modelle sind auf gitHub verfügbar [1].

Referenzen

[1] https://github.com/ARM-software/ML-KWS-for-MCU

[2] Sercan O Arik, Markus Kliegl, Rewon Child, Joel Hestness, Andrew Gibiansky, Chris Fougner, Ryan Prenger and Adam Coates, Convolutional recurrent neural networks for small-footprint keyword spotting, https://arxiv.org/abs/1703.05390

- Schlüsselwortsuche auf Mikrocontrollern

- Mikrocontrollergrundlagen

- Neuronale Netze zur SWS

- Experimente und Ergebnisse

- Ressourcen-basierte Klassifizierung von Neuronalen Netzen zur Schlüsselwortsuche

- Ressourcenbeschränkte NN-Architektur-Exploration