Eine Frage der Architektur

Präzise HF-Prüfungen mit RasPi-basiertem DDS-Signalgenerator

Fortsetzung des Artikels von Teil 1

Softwarearchitektur und Kalibrierung

A: Softwaresteuerung

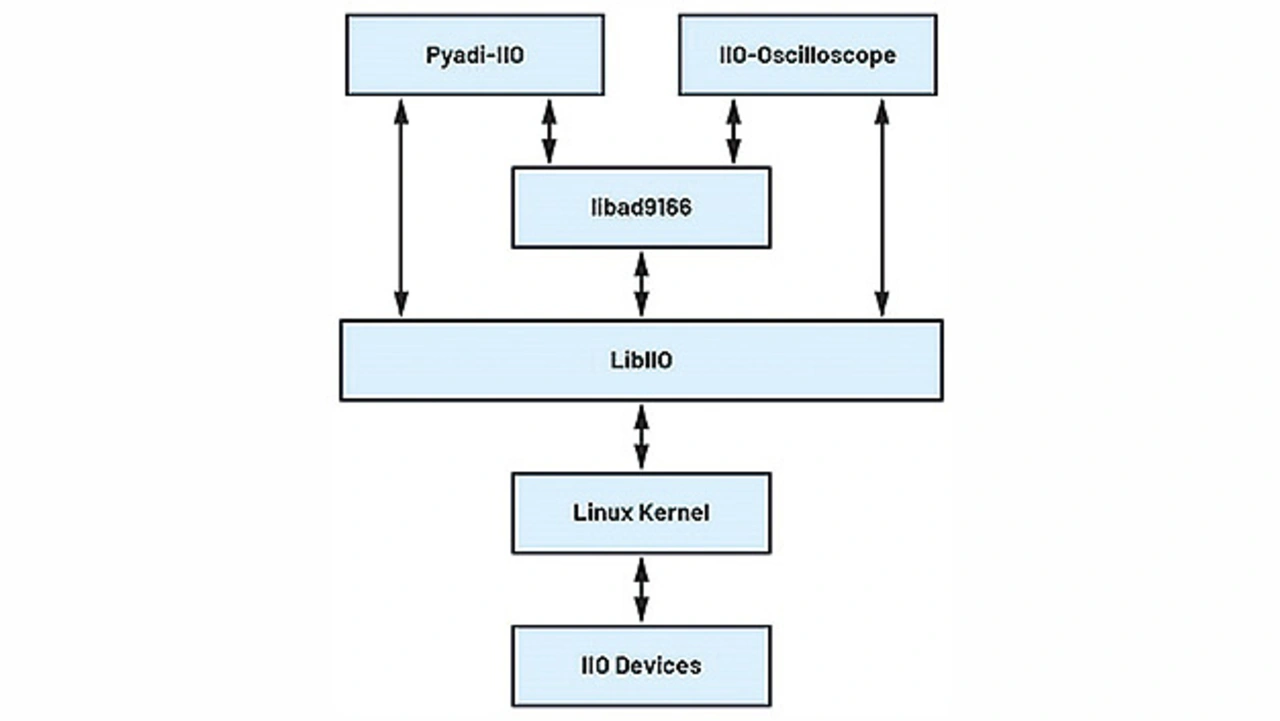

Bei allen Anwendungen, die einen Signalgenerator beinhalten, sollte die Steuerung der Messgeräte einfach und flexibel sein. Der CN0511 kann als Plug-and-Play-System betrachtet werden, da er nur eine SD-Karte mit einem Kuiper-Linux-Image benötigt, die in den Raspberry Pi eingesteckt wird. Das Kuiper-Linux-Image enthält die gesamte Software, die zur Steuerung des Signalgenerators erforderlich ist. Es stehen zwei Methoden zur Änderung der Ausgangsleistung und -frequenz zur Verfügung: Das PyADI-IIO-Modul kann verwendet werden, um den Code zu schreiben, oder die grafische Benutzeroberfläche (GUI) des IIO-Oszilloskops kann zur Eingabe des gewünschten Ausgangssignals verwendet werden.

Das PyADI-IIO ist ein Python-Abstraktionsmodul für ADI-Hardware mit industriellen Input/Output(IIO)-Treibern. Dieses Modul stellt vereinfachte und leicht zu verwendende Python-Methoden und -Attribute zur Steuerung der Hardware bereit. Das Board kann mit sehr einfachen Python-Codezeilen gesteuert werden, die lokal oder aus der Ferne ausgeführt werden können. Ein beliebiger Frequenzdurchlauf zum Testen anderer Geräte kann mit einer einfachen FOR-Schleife und einigen wenigen Verzögerungsgliedern erstellt werden.

Das IIO-Oscilloscope ist eine plattformübergreifende GUI-Anwendung, bei der die Amplitude der Ausgangsleistung sowie die Frequenz als Eingabe vom Benutzer benötigt werden.

Jobangebote+ passend zum Thema

Beide Module, PyADI-IIO und IIO-Oscilloscope, liefern das Ausgangssignal der Sperrschichttemperatursensoren: eines im PLL-IC und das andere im Vektorsignalgenerator-IC. Bild 9 zeigt diese beiden Softwaremodule sowie die anderen Komponenten, die für die Kommunikation mit dem CN0511-Board benötigt werden (libAD9166, LibIIO und der Linux-Kernel). Die in Bild 9 dargestellte libAD9166 ist eine weitere Bibliothek, die für die genaue Steuerung der Ausgangsleistung erforderlich ist und auf dem Kuiper-Image vorinstalliert ist. Diese Bibliothek enthält den für die Ausgabe der kalibrierten Leistung erforderlichen C++-Code und ist spezifisch für dieses Board. Die Theorie, die hinter der Kalibrierung steht, wird in Abschnitt B erläutert: Kalibrierung der Ausgangsleistung.

B: Kalibrierung der Ausgangsleistung

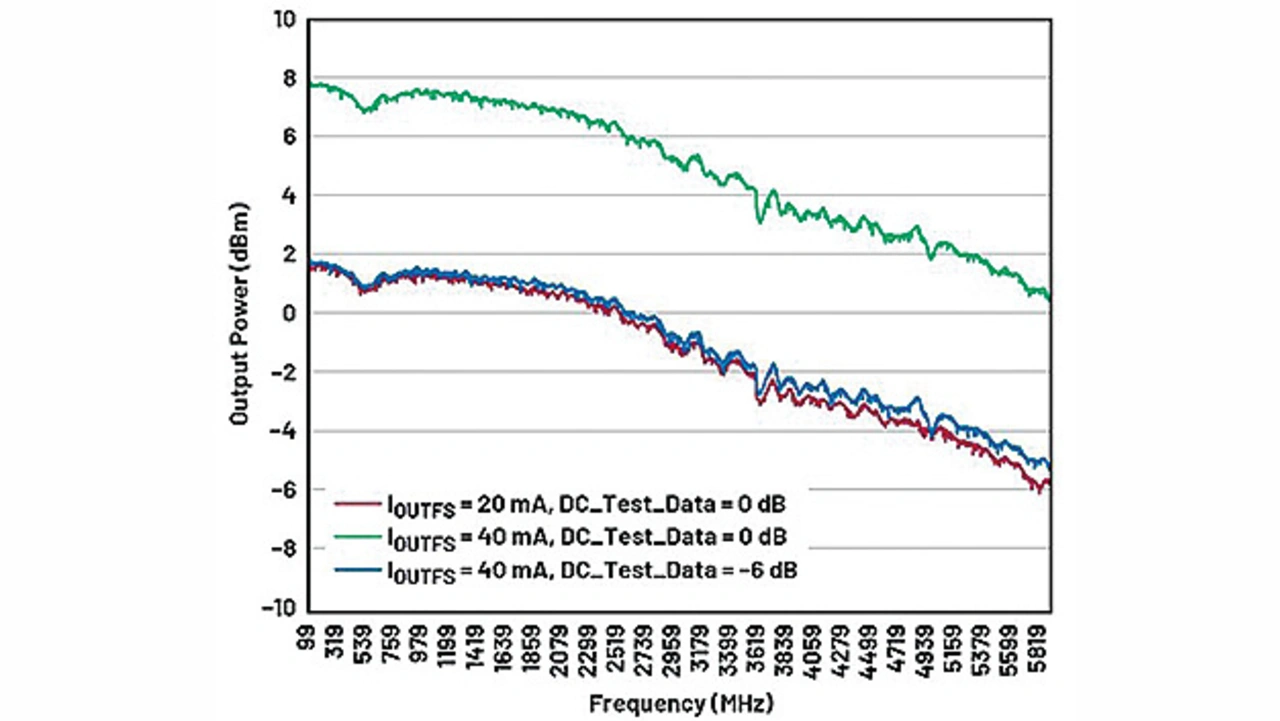

Bei Signalgeneratoranwendungen ist die Bandflachheit ein kritischer Parameter. Beim vorgestellten System wird die Charakteristik der Ausgangsleistung in Abhängigkeit von der Frequenz hauptsächlich durch den Ausgang des Vektorsignalgenerators bestimmt. Mit zunehmender Frequenz sinkt die Ausgangsimpedanz gegenüber ihrem Gleichstromwert. Diese Änderung der Ausgangsimpedanz wirkt sich zusammen mit einer eventuellen Impedanzfehlanpassung an der Last direkt auf die Ausgangsleistung aus. Darüber hinaus wirkt sich ein vorhersagbarer Sinc-Roll-off ebenfalls auf den Frequenzgang der Ausgangsleistung aus.

Die gemessene unkalibrierte Ausgangsleistung in Abhängigkeit von der Frequenz wird in Bild 10 dargestellt und besprochen. Um diese unerwünschten Faktoren zu vermeiden, wurde eine Softwarekalibrierung der Ausgangsleistung in Abhängigkeit von der Frequenz implementiert.

Die Einstellelemente, mit denen die Ausgangsleistung korrigiert werden kann, sind zwei Register des AD9166: das 10-Bit-Register, das den Skalenendwert des Stroms einstellt, Ioutfs_reg (Adressen 0x42 und 0x41), und das 16-Bit-Register, das den Skalenendwert des Stroms einstellt, Iout_reg (Adressen 0x14E und 0x14F). Diese beiden Register steuern den Ausgangsstrom des DAC des AD9166, der auch den Eingangsstrom für den Verstärker des AD9166 darstellt (Bild 3).

Ioutfs_reg bietet einen Aussteuerungsbereich der Ausgangsleistung von etwa 10 dBm, ein perfekter Wert für die Korrektur der in Bild 10 gezeigten unerwünschten Charakteristik.

Messungen ergaben, dass jedes Leiterplattenmuster die gleiche Form der in Bild 10 gezeigten Kennlinie aufwies, mit Ausnahme eines unterschiedlichen Offsets. Unter Berücksichtigung dieser Erkenntnis wurden zwei Kalibrierungsroutinen entwickelt. Die erste Kalibrierungsroutine wird nur einmal durchgeführt und liefert die Parameter, die für die Korrektur der gesamten Kennlinie erforderlich sind, sodass diese flach wird. Die zweite Routine korrigiert den Offset-Fehler zwischen den einzelnen Boards und wird als Produktionskontrolle für jedes Board durchgeführt. Beide Kalibrierungsroutinen werden mittels Ausgangsmessungen, Berechnungen und Registeranpassungen auf der Grundlage von Berechnungen durchgeführt.

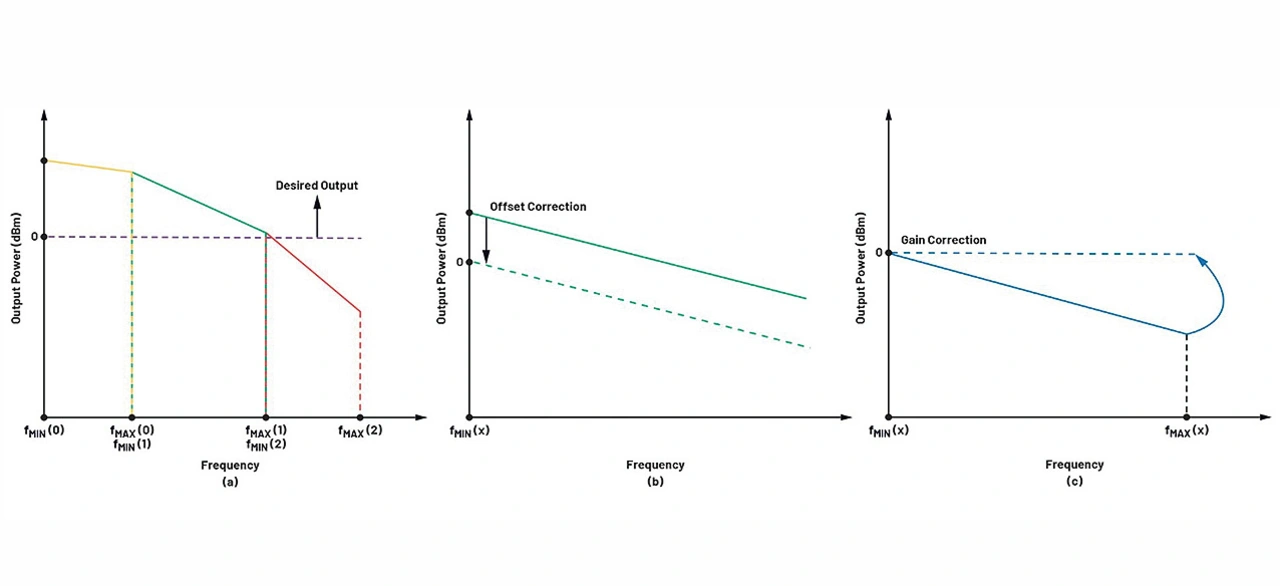

Die Grundidee der ersten Kalibrierungsroutine ist in Bild 11 dargestellt. Zunächst wird die gesamte Kennlinie aus Bild 10 in mehrere Frequenzintervalle aufgeteilt, die durch Liniensegmente von fmin[x] bis fmax[x] approximiert werden können, wobei x der Index des Intervalls ist, x ∈ [0, 31], und x ein ganzzahliger, positiver Wert ist. Für das eigentliche Design wurden 31 Intervalle gewählt, wobei in Bild 11a zur besseren Veranschaulichung nur drei Intervalle dargestellt sind. Für jedes Intervall müssen zwei Konstanten ermittelt werden: eine namens Offset_correction für die Offset-Korrektur, (Bild 11b), und eine namens Gain_correction für die Gain-Korrektur, (Bild 11c). Zur Nachverfolgung der Intervalle muss zudem der Parameter fmin[x] gespeichert werden.

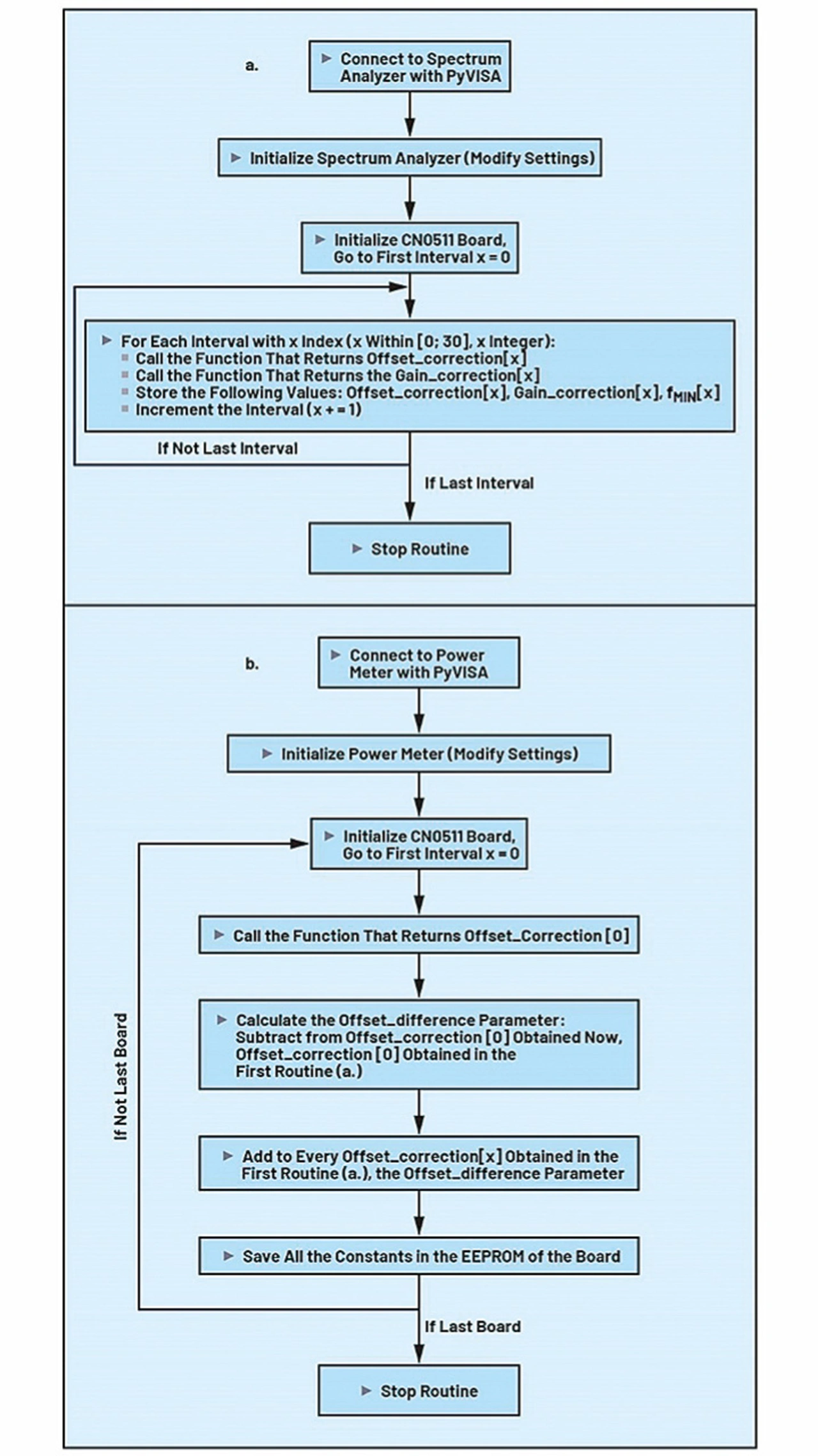

Bild 12 zeigt ein Pseudocode-Flussdiagramm, in dem die Funktionsweise der ersten Kalibrierungsroutine dargestellt ist. Zur Durchführung dieses Algorithmus ist ein sehr genauer Spektrumanalysator zur Messung der Ausgangsleistung erforderlich (hier wurde der Keysight E5052B/R&S FSUP verwendet). Die sich aus der ersten Routine ergebenden Parameter (Bild 12a) werden in der zweiten Kalibrierungsroutine verwendet, die in Bild 12b dargestellt ist.

Die zweite Kalibrierungsroutine (Bild 12b) wird für jedes Leiterplattenmuster in einem Produktionstest ausgeführt und fügt dem Parameter Offset_correction für jedes Intervall die gleiche Konstante hinzu. Am Ende der zweiten Routine werden die geänderten Parameter Offset_correction[x] sowie Gain_correction[x] und fmin[x] für jedes Intervall im EEPROM des Boards gespeichert.

Zur Einstellung der kalibrierten Ausgangsleistung wird in der Software die Gleichung verwendet, um den Wert im Register Ioutfs_reg zu berechnen, der zur Anpassung der Ausgangsleistung an die Frequenz fx erforderlich ist. fx ist die Frequenz innerhalb des Intervalls x: fx ∈ [fmin[x], fmax[x]), wobei fx eine reelle positive Zahl ist und fmin[x] die minimale Frequenz des Intervalls mit dem Index x ist.

Wie in der Gleichung zu sehen, müssen drei Parameter auf der Karte gespeichert werden, um die Ausgangskorrektur für jedes Intervall x zu ermöglichen: Offset_correction[x], Gain_correction[x], und fmin[x].

Systemleistung

A: Kalibrierte Ausgangsleistung

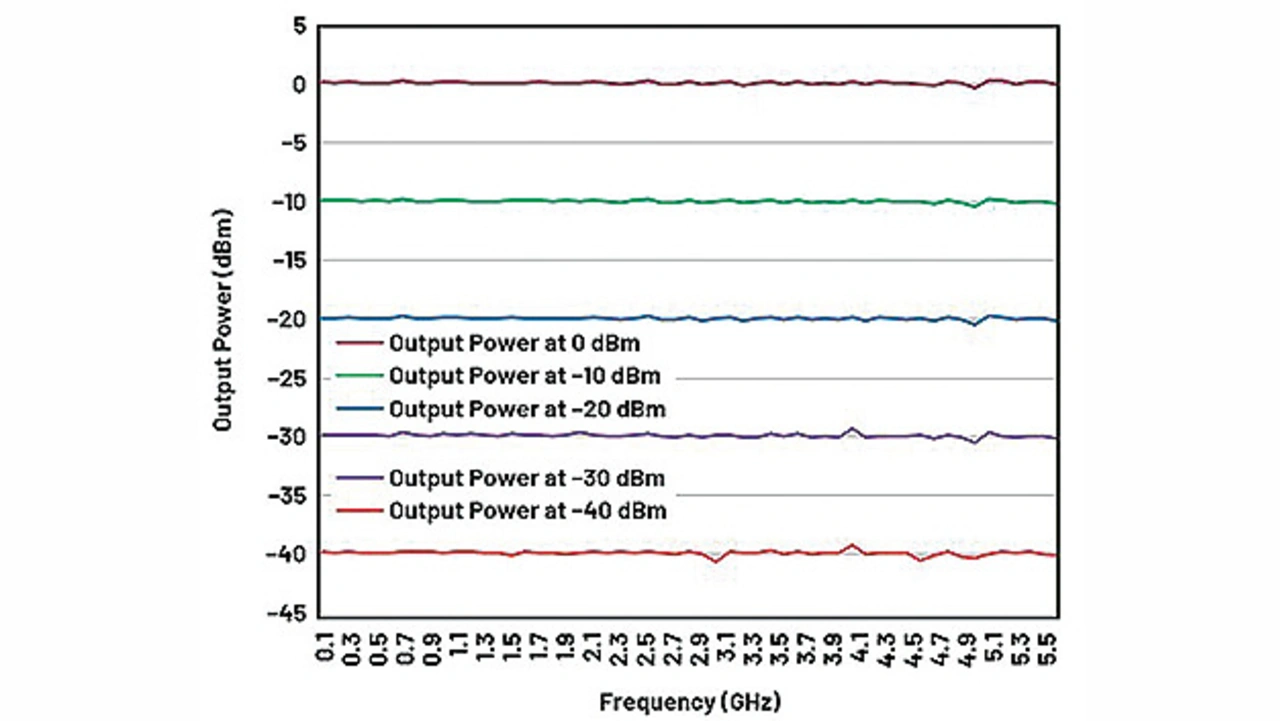

Bild 13 zeigt die breitbandige kompensierte Bandflachheit des CN0511 bei verschiedenen Ausgangsleistungspegeln. Für jede zwischen 0 dBm und -40 dBm eingestellte Ausgangsleistung beträgt die Genauigkeit ±0,5 dBm im gesamten Band von DC bis 5,5 GHz.

B: Phasenrauschen

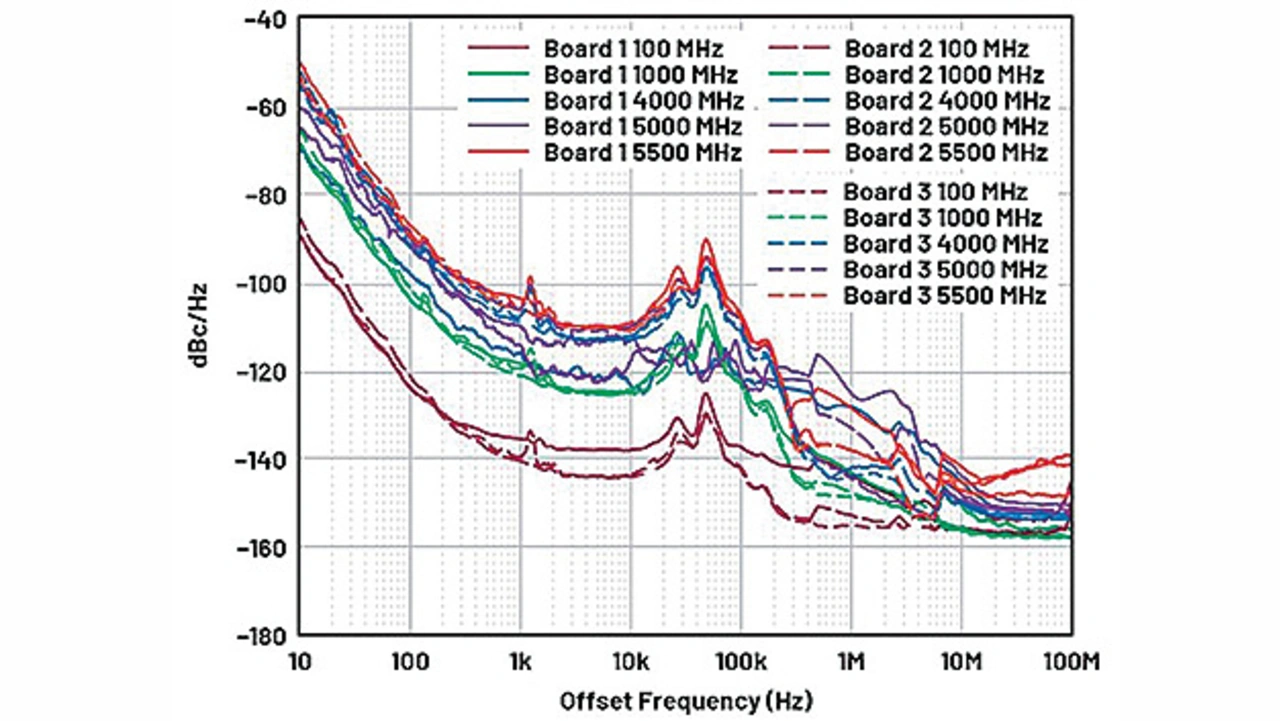

Die Qualität der Taktquelle sowie ihre Schnittstelle zum Takteingang des AD9166 haben einen direkten Einfluss auf das Phasenrauschen. Phasenrauschen und Störimpulse bei einem bestimmten Frequenzoffset der Taktquelle übertragen sich direkt auf das Ausgangssignal. Die in Bild 14 dargestellten Kurven zeigen das gemessene SSB-Phasenrauschen in Abhängigkeit vom Frequenzoffset. Alle Daten wurden bei voller Ausgangsleistung ermittelt. Als Systemtaktreferenz wurde der integrierte spannungsgesteuerte CMOS-Quarzoszillator mit 122,88 MHz verwendet.

C: Thermische Leistung

Der Hochgeschwindigkeits-DAC hat je nach Anwendung und Konfiguration eine Leistungsaufnahme von fast 4 W. Er hat ein freiliegendes Chipgehäuse, um den Wärmewiderstand zu verringern und eine direkte Kühlung des Chips zu ermöglichen. Zur Ableitung der Wärme aus dem Gehäuse wird ein mechanischer Kühlkörper mit einem Lüfter verwendet. Mit angebrachten Kühlkörpern erreicht der LTM4622 als höchsten Temperaturmesswert etwa 60,6 °C bei einer Umgebungstemperatur von 25 °C.

Schlussfolgerung

In diesem Artikel wurde eine hochfrequente, verzerrungsarme und rauscharme Signalquelle vorgestellt. Das System ist eine Lösung für einen kostengünstigen HF-Signalsynthesizer, der eine Hochgeschwindigkeits-DAC-basierte DDS-Architektur verwendet. Durch die Verwendung eines Vektorsignalgenerators, der auf einem DDS-Verfahren basiert, bietet das vorgestellte System mehrere Vorteile gegenüber einer einfachen PLL, wie z. B. Einfachheit, geringe Verzerrungen, hochauflösende Abstimmung, nahezu sofortige Frequenzsprünge, Phasen- und Amplitudenmodulation.

Die Vorteile der verwendeten DDS-Architektur liegen in der Möglichkeit der Anpassung und Kalibrierung der Ausgangsleistung sowie der Feinabstimmung der Ausgangsfrequenz. Durch Hinzufügen einer Kalibrierungsroutine zum System erhält der Benutzer einen Ausgangsreferenzton von 0 Hz bis 5,5 GHz mit einer Genauigkeit von ±0,5 dBm und einem Dynamikbereich von 0 dBm bis -40 dBm – eine nahezu perfekte Lösung für ein Laborgerät.

Literatur

1 Paul R. Gray, Paul J. Hurst, Stephen H. Lewis und Robert G. Meyer. Analysis and Design of Analog Integrated Circuits. Wiley, Januar 2009.

2 Mike Curtin and Paul O’Brien. “Phase-Locked Loops for High Frequency Receivers

and Transmitters.” Analog Dialogue, Bd. 33, Nr. 3, Juli 1999.

3 VCO Designers Handbook. Mini-Circuits Corporation, 1996.

4 Leon W. Couch. Digital and Analog Communications Systems. Macmillan Publishing Company, 1990.

5 Peter Vizmuller. RF Design Guide. Artech House, 1995.

6 Jim Surber und Leo McHugh. “Single-Chip Direct Digital Synthesis vs. the Analog PLL.” Analog Dialogue, Bd. 30, Nr. 3, Juli 1996.

EVAL-CN0511-RPIZ User Guide. Analog Devices, Januar 2023.

Die Autoren

Erbe D. Reyta

ist seit 2011 Hardware Application Engineer im »Circuits from the Lab«-Programm von ADI, wo er sich hauptsächlich auf die Entwicklung von Hardware für Präzisionssysteme konzentriert. Er erwarb seinen Bachelor-Abschluss in Elektronik und Kommunikations-technik an der University of the Philippines Diliman und seinen Master-Abschluss in Computertechnik an der University of the City of Manila, Philippinen.

Mihai Bancisor

ist Systems Integration Engineering Manager in der Customer Office Solutions Group und arbeitet seit elf Jahren bei Analog Devices. Seine Schwerpunkte sind Software Defined Radio und System on Module. Er hat einen Bachelor- und einen Master-Abschluss in angewandter Elektronik von der Technischen Universität Cluj-Napoca

Valentin Beleca

ist System Integration Engineer bei Analog Devices, wo er im Bereich Leiterplattendesign arbeitet. Er begann seine Arbeit bei ADI im Februar 2021 in Cluj-Napoca, Rumänien. Er ist derzeit Masterstudent im Studiengang Integrierte Schaltungen und Systeme an der Technischen Universität Cluj-Napoca und hat einen Bachelor-Abschluss in Elektronik und Telekommunikation der Technischen Universität Cluj-Napoca

- Präzise HF-Prüfungen mit RasPi-basiertem DDS-Signalgenerator

- Softwarearchitektur und Kalibrierung