Eine Frage der Architektur

Präzise HF-Prüfungen mit RasPi-basiertem DDS-Signalgenerator

Für HF-Hardwareprüfungen ist eine konfigurierbare, kalibrierte, zuverlässige Signalquelle essenziell. Von Analog Devices kommt nun eine hochintegrierte Lösung für einen synthetischen HF-Signalgenerator auf Grundlage eines Raspberry Pi, basierend auf einer direkten digitalen Synthese-Architektur.

HF-Signalgeneratoren, insbesondere für Mikrowellenfrequenzen, wurden in der Vergangenheit auf der Grundlage von Phase-Locked-Loop(PLL)-Synthesizern erzeugt [1]. Die PLL ermöglicht die Erzeugung einer stabilen Hochfrequenz aus einer Niederfrequenz-Referenz.

Jobangebote+ passend zum Thema

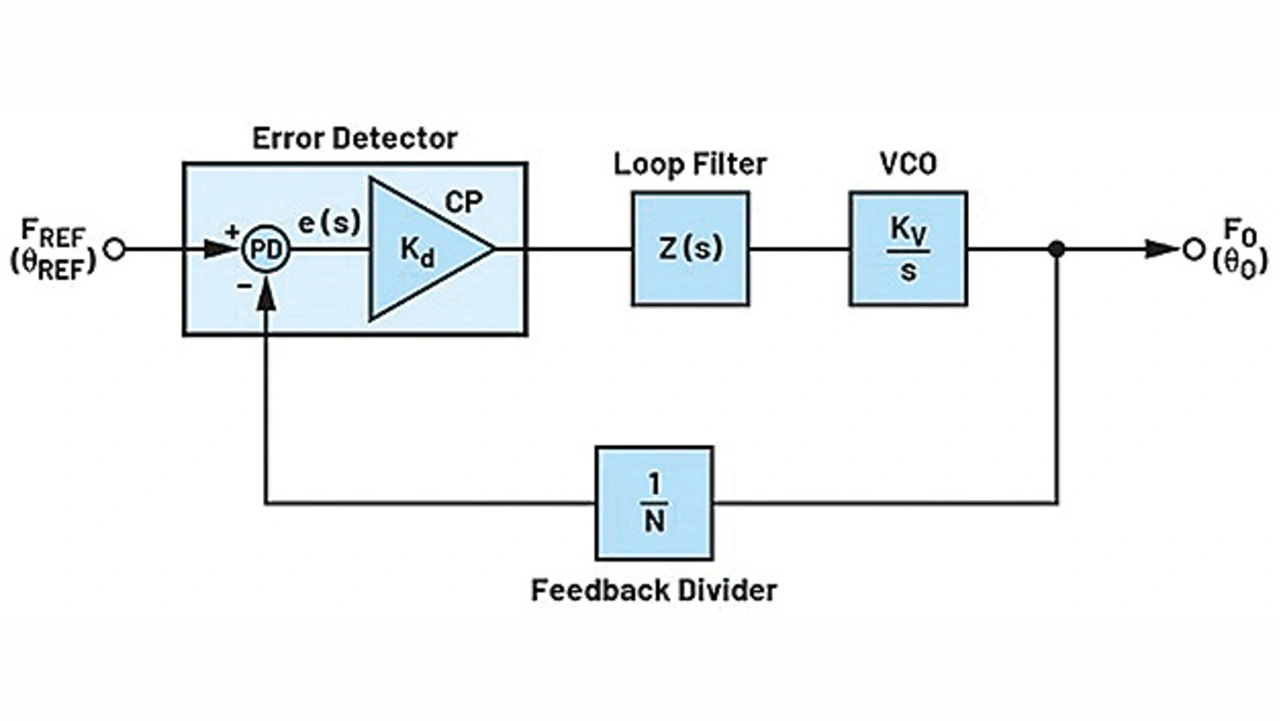

Bild 1 zeigt ein grundlegendes Modell einer PLL. Dieses Modell besteht aus einem Rückkopplungssystem, das sich zusammensetzt aus einem spannungsgesteuerten Oszillator, der die Ausgangsfrequenz variiert, einem Fehlerdetektor, der die Eingangsreferenzfrequenz und die Ausgangsfrequenz vergleicht, sowie einem Frequenzteiler. Die Schleife wird als verriegelt bezeichnet, wenn Ausgangsfrequenz und -phase des Frequenzteilers mit der Frequenz und Phase der Eingangsreferenz übereinstimmen [2-5].

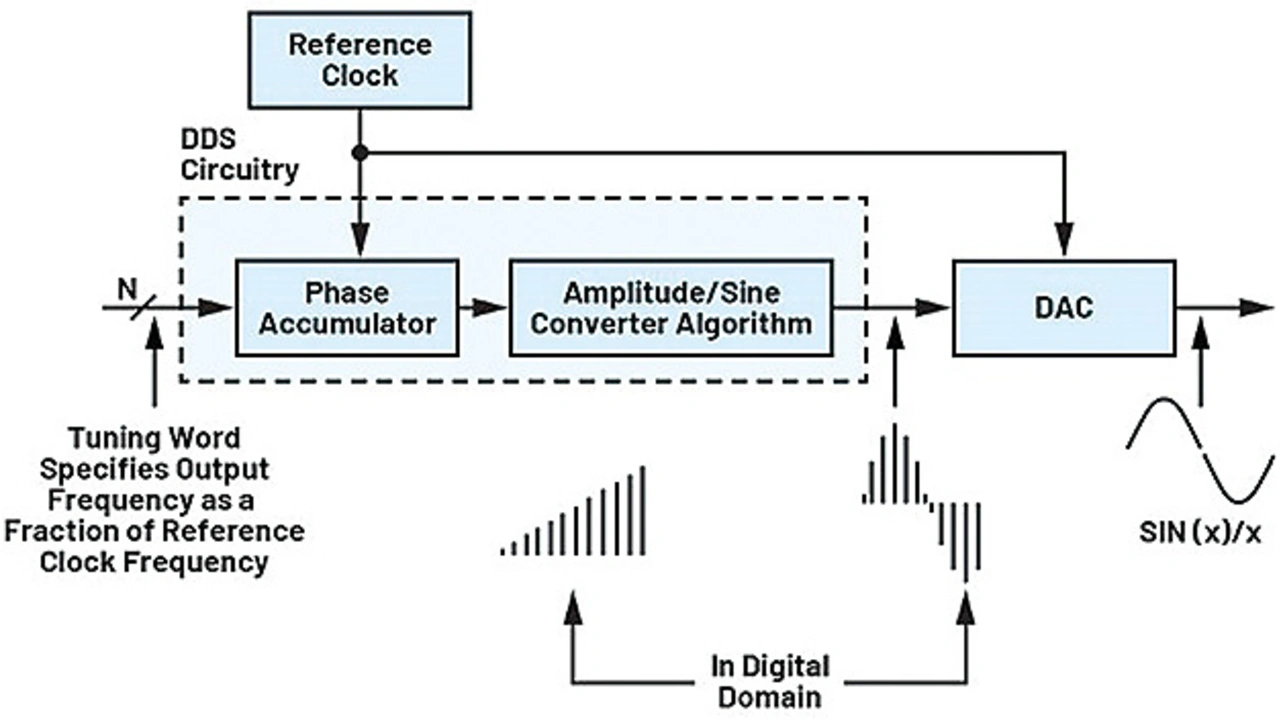

Je nach Anwendung kann eine DDS-Architektur die bessere Alternative zur PLL sein als ein Frequenzsynthesizer. Ein typischer DDS-basierter Signalgenerator ist in Bild 2 dargestellt. Ein Abstimmwort wird einem Phasenakkumulator zugeführt, der die Steigung der Ausgangsrampe bestimmt. Die oberen Bits des Akkumulators werden durch einen Amplituden-zu-Sinus-Wandler und schließlich zu einem DAC geleitet. Eine DDS-Architektur bietet gegenüber einer PLL erhebliche Vorteile. Beispielsweise ermöglicht der digitale Phasenakkumulator beim DDS eine viel feinere Auflösung der Ausgangsfrequenz als ein PLL-basierter Synthesizer.

Die PLL-Schaltzeit ist eine Funktion der Einschwingzeit der Rückkopplungsschleife und der VCO-Ansprechzeit, die naturgemäß langsamer ist als bei einem DDS, der nur durch seine digitale Verarbeitungsverzögerung begrenzt wird. Hinsichtlich der Leiterplattengröße bietet ein DDS eine kleinere Fläche, was sich in einem einfacheren System- design niederschlägt und somit verschiedene Herausforderungen beim Hardware-HF-Design eliminiert [6].

Architektur und Designüberlegungen auf Systemebene

Betrachten wir das Gesamtsystemdesign eines kompletten Sinussignalgenerators von DC bis 5,5 GHz auf Basis einer DDS-Architektur anhand des Circuit Note CN0511.

A: Design auf Systemebene

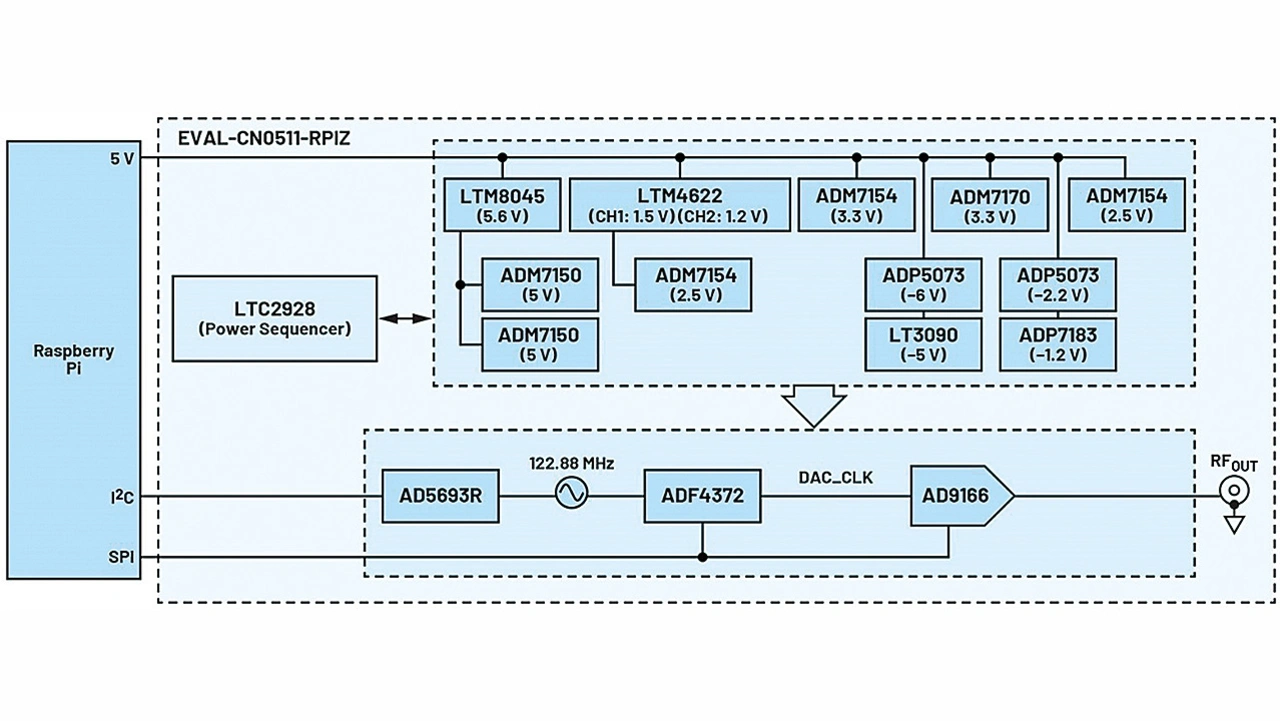

Das in Bild 3 gezeigte System ist ein vollständiger, auf einer DDS-Architektur basierender Sinussignalgenerator für den Bereich von 0 Hz bis 5,5 GHz. Ein Quad-Switch-DAC-Kern und ein integrierter Ausgangsverstärker bieten eine außergewöhnlich geringe Verzerrung über den gesamten Betriebsfrequenzbereich sowie eine angepasste 50-Ω-Ausgangsterminierung. Die On-Board-Taktung umfasst einen Referenzoszillator und eine PLL, wodurch eine externe Taktquelle überflüssig wird. Die gesamte Stromversorgung erfolgt über eine Raspberry-Pi-Platine mit Reglern mit extrem hohem Netzstörunterdrückungsverhältnis (PSRR) und passiver Filterung, um die Auswirkungen der Stromversorgungswandler auf die HF-Leistung zu minimieren.

Die in Bild 3 gezeigte Architektur kann für verschiedene Anwendungen wie Radar, automatisierte Tests, Arbitrary-Waveform-Generatoren und Einzelton-Signalgeneratoren verwendet werden. In diesem Beitrag wird der letztgenannte implementiert. Die folgenden Unterabschnitte beschreiben die integrierten Hauptbausteine, die in der Schaltung der CN0500 eingesetzt werden.

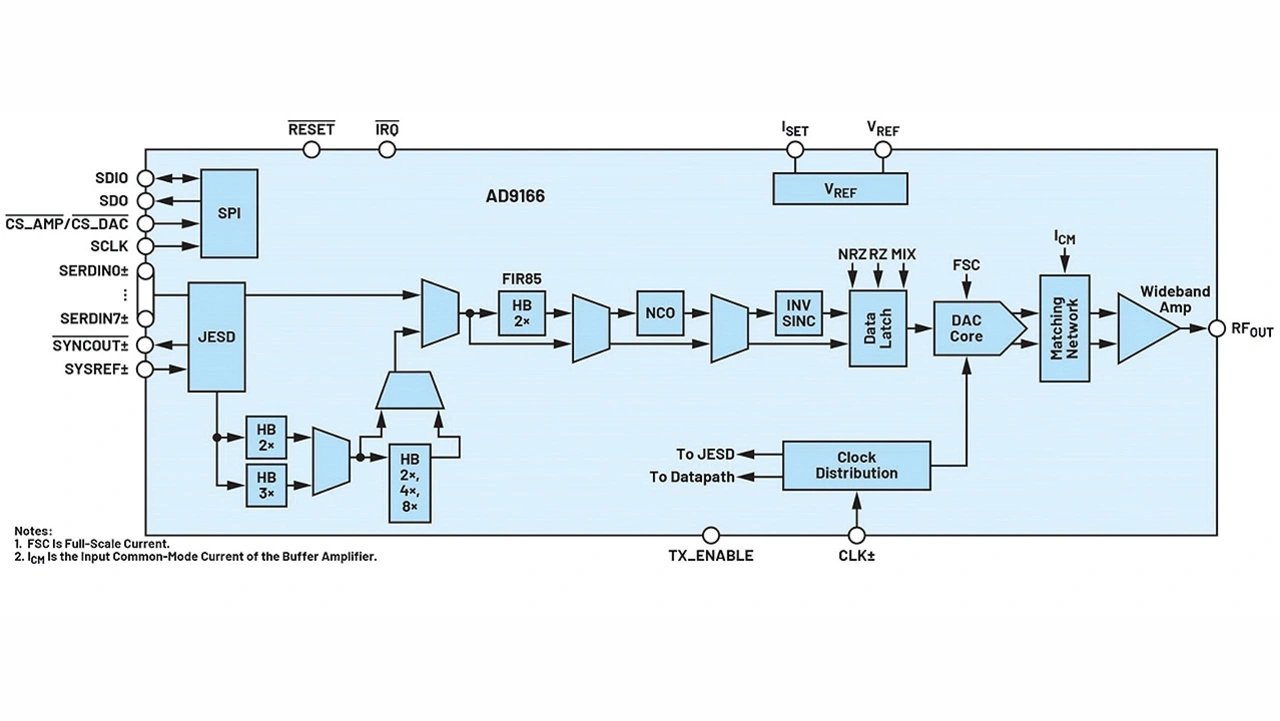

B: Vektorsignalgenerator

Der in Bild 4 gezeigte Vektorsignalgenerator für 0 Hz bis 9 GHz verfügt über einen DAC mit 6 GS/s (1×, Non-Return-to-Zero-Modus), eine JESD204B-Datenschnittstelle mit acht Lanes und 12,5 Gbit/s sowie einen DDS mit mehreren numerisch gesteuerten Oszillatoren (NCOs). Darüber hinaus stellt er einen hochgradig konfigurierbaren digitalen Datenpfad dar, der Interpolationsfilter, inverse SINC-Kompensation und digitale Mischer für eine flexible Spektrumsplanung umfasst.

Das in Bild 4 gezeigte System nutzt den programmierbaren 48-bit-Modulus-NCO des DAC, um digitale Frequenzverschiebungen von Signalen mit sehr hoher Präzision (Frequenzauflösung von 43 μHz) zu ermöglichen. Der NCO für diesen DAC benötigt nur die 100 MHz der SPI-Schreibschnittstelle für die schnelle Aktualisierung des Frequenzabstimmworts (FTW). Die SPI-Schnittstelle ermöglicht zudem die Konfiguration und Überwachung verschiedener Funktionsblöcke in diesem DAC. Die JESD-Lanes werden in diesem Design nicht verwendet, und der Baustein wird nur im NCO-Modus betrieben.

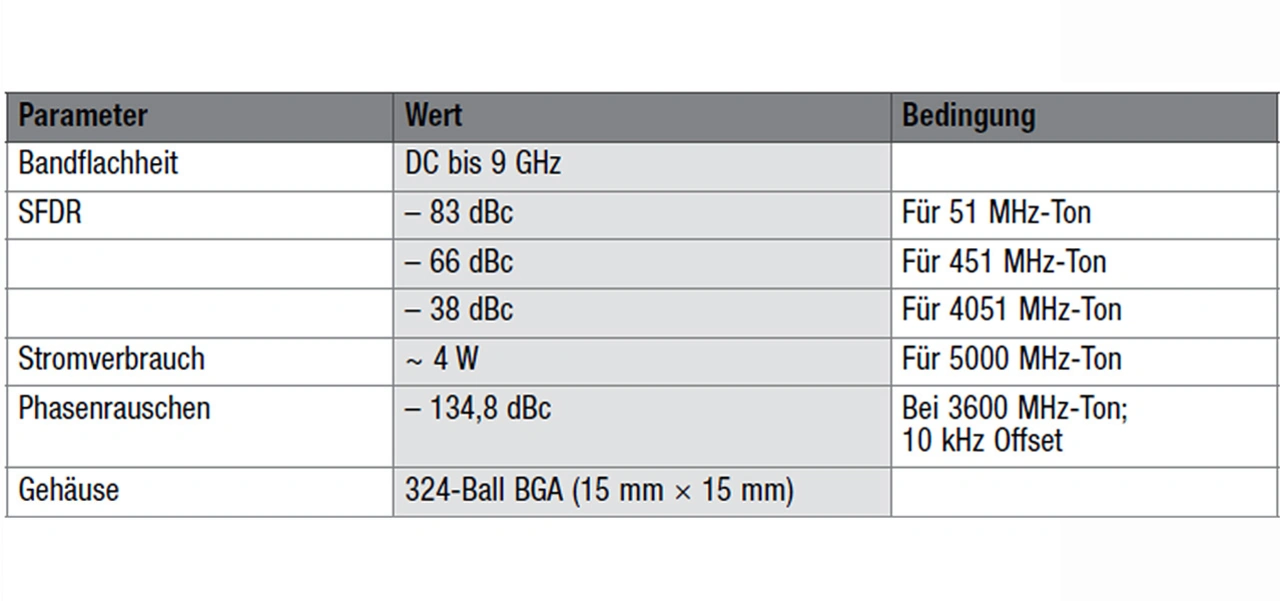

Der in Bild 4 gezeigte Vektorsignalgenerator verfügt über einen integrierten HF-Ausgangsverstärker mit unsymmetrischem und mit 50 Ω abgeschlossenem Ausgang, sodass keine schwierigen HF-Ausgangsschaltungen erforderlich sind. In der Tabelle sind die Vorzüge und Leistungsmerkmale des AD9166 unter verschiedenen Bedingungen aufgeführt.

C: Systemtaktung

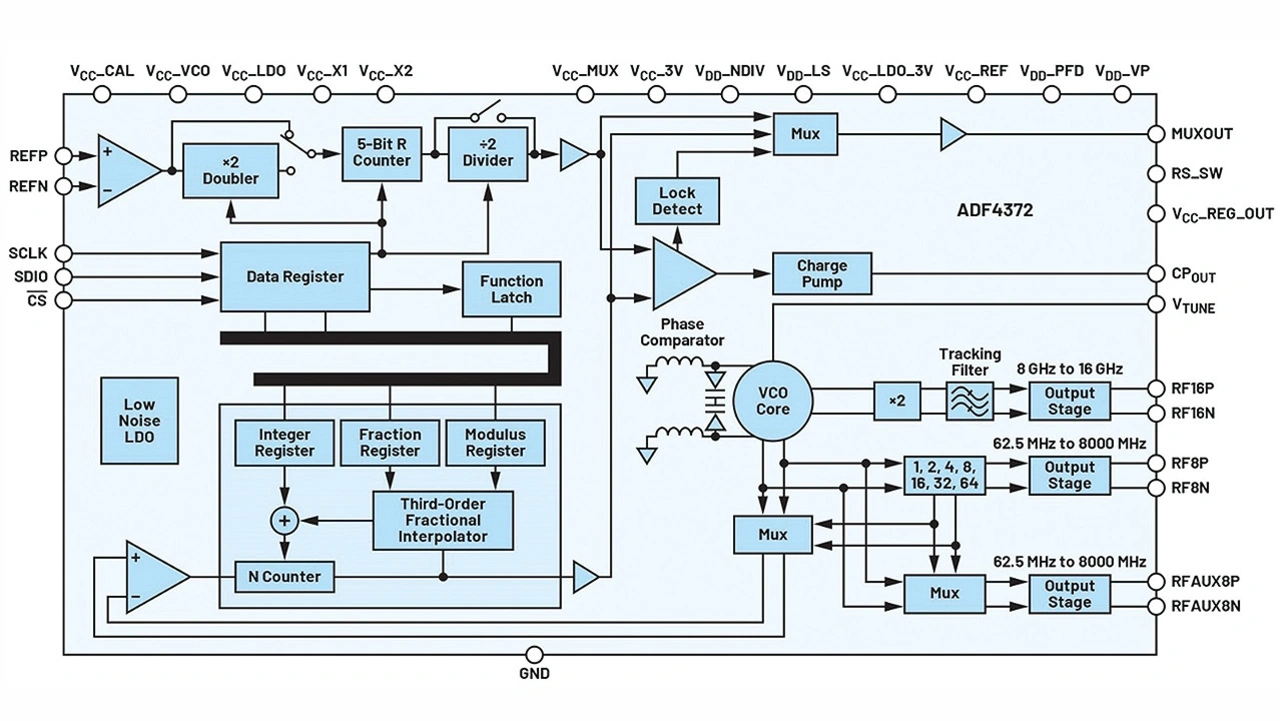

Das System in Bild 2 verwendet die PLL ADF4372 (Bild 5), einen Breitband-Synthesizer mit integriertem VCO, der in Verbindung mit einem externen Schleifenfilter und einer externen Referenzfrequenz die Implementierung von Fractional-N- oder Integer-N-Frequenzsynthesizern ermöglicht. Darüber hinaus ist die VCO-Frequenz mit einer Schaltung zur Teilung durch 1, 2, 4, 8, 16, 32 oder 64 verbunden, die es dem Benutzer ermöglicht, HF-Ausgangsfrequenzen bis herunter zu 62,5 MHz bei RF8x zu erzeugen.

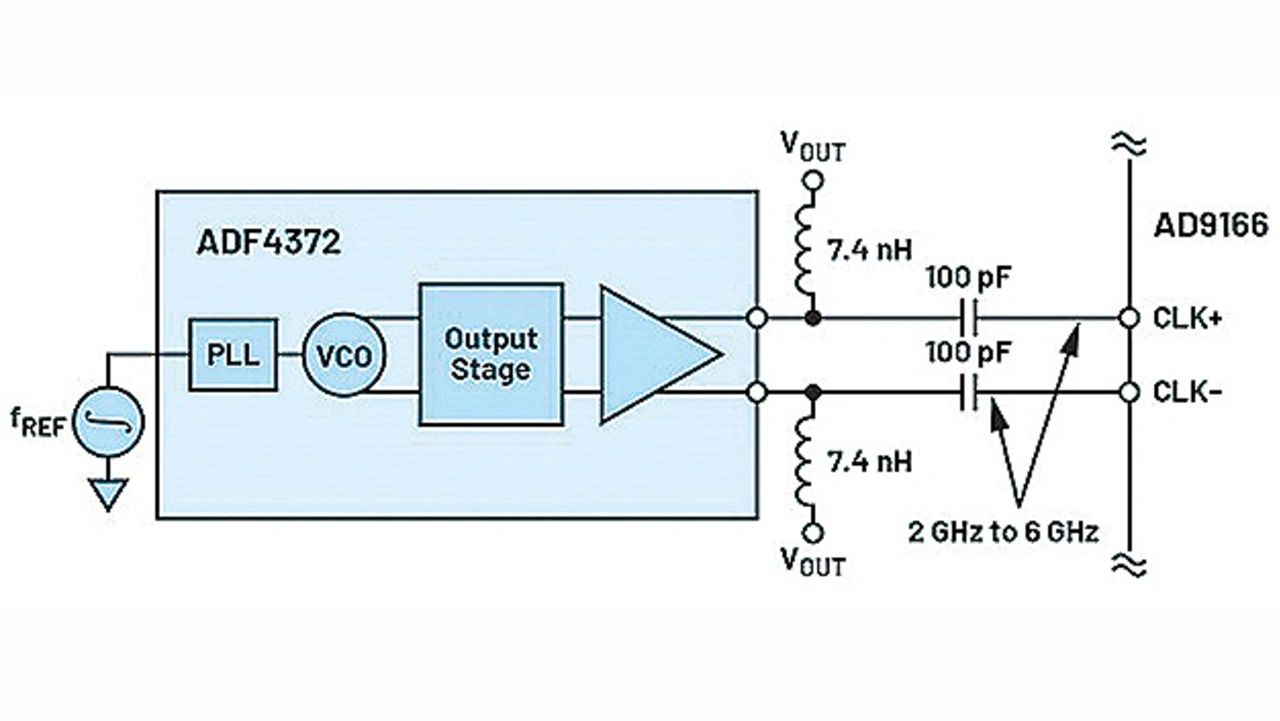

Die Qualität der Taktquelle, z. B. ihr Phasenrauschen und ihre Störungseigenschaften, sowie ihre Schnittstelle zum Hochgeschwindigkeits-DAC-Takteingang wirken sich direkt auf die AC-Leistung aus. Somit werden das Phasenrauschen und andere Spektralanteile direkt auf das Ausgangssignal aufmoduliert. Um eine optimale Leistung hinsichtlich ganzzahliger Grenzstörungen und Phasenrauschen zu erzielen, verwendet der ADF4372 ein unsymmetrisches Referenzeingangs- signal, das dann multipliziert wird, um den Takt für den Hochgeschwindigkeits-DAC zu erzeugen (Bild 6).

D: Architektur der Stromversorgung

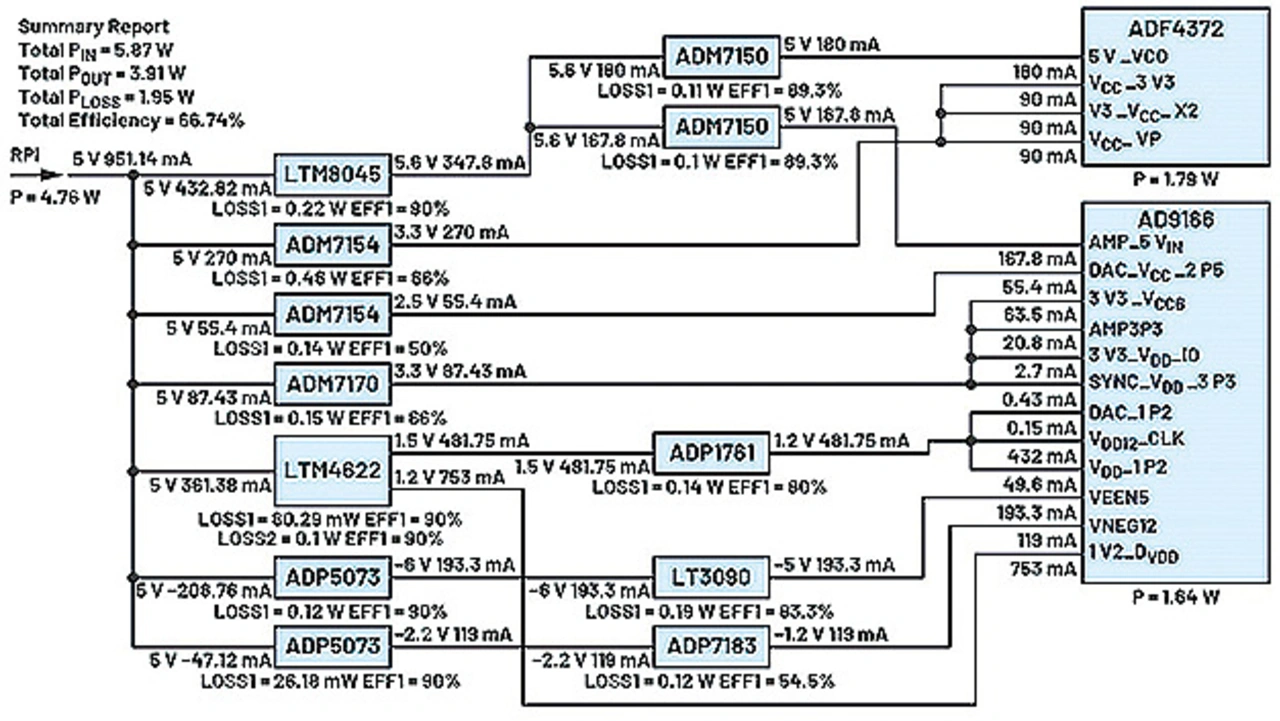

Der in Bild 7 dargestellte System-Stromversorgungsbaum für den CN0511 verwendet die Schaltregler LTM8045, LTM4622 und ADP5073, um einen Wirkungsgrad von 90 % entsprechend der Systemlastanforderungen zu erreichen. Die Low-Dropout-Linearregler (LDOs), wie der ADM7150, ADM7154 und der ADP1761, wurden für die Versorgung von DAC, Verstärker, PLL und VCO aufgrund ihres extrem niedrigen Rauschens und hohem PSRR ausgewählt, um die bestmögliche Phasenrauschleistung zu erzielen.

Der Power-Sequencer-IC LTC2928 wurde verwendet, um sicherzustellen, dass der Hochgeschwindigkeits-DAC in der richtigen Reihenfolge eingeschaltet wird, um eine Beschädigung der internen Schaltung zu vermeiden. Der Power-Sequencer-IC überwacht und verwaltet bis zu vier Versorgungsspannungen und steuert individuell die Einschaltzeit und erfüllt seine anderen Überwachungsfunktionen, einschließlich Unter- und Überspannungsüberwachung und -meldung.

E: Layoutüberlegungen

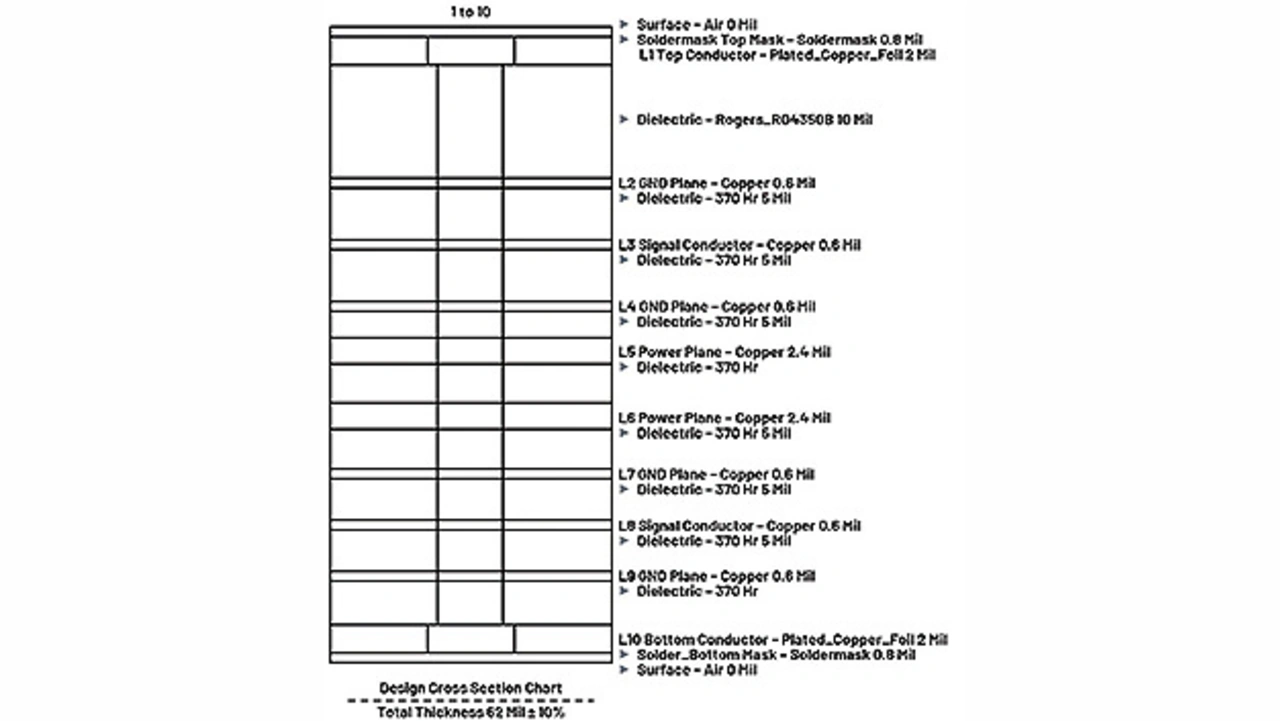

Bei dieser Anwendung, bei der höchste Leistung und höhere Ausgangsfrequenzen erforderlich sind, hat die Wahl des Leiterplattenmaterials einen erheblichen Einfluss auf die Ergebnisse. Bild 8 zeigt den empfohlenen Leiterplattenaufbau des CN0511, bei dem das dielektrische Material 4350 von Rogers auf den Layern verwendet wird, die die HF-Leiterbahnen enthalten, um die Signaldämpfung bei Signalen über 3 GHz zu minimieren, was zudem die beste Signalintegrität am HF-Ausgang gewährleistet.

Die thermische Leistung hängt direkt mit dem Leiterplattendesign und der Betriebsumgebung zusammen. Um die thermische Leistung des Designs zu verbessern, werden thermische Durchkontaktierungen auf dem Thermal Pad der Leiterplatte verwendet.

- Präzise HF-Prüfungen mit RasPi-basiertem DDS-Signalgenerator

- Softwarearchitektur und Kalibrierung