EMV und Störfestigkeit

ICs als EMV-Schwachstellen: Probleme beseitigen

Fortsetzung des Artikels von Teil 3

Lösung der Beeinflussungsprobleme

Eine wichtige Erkenntnis ist, dass neben den direkten Spannungseinbrüchen durch den Störimpuls Einschwingvorgänge angestoßen werden, die zwischen Vdd und Vss Differenzspannung erzeugen und den IC regelrecht abschalten. Der notwendige Wert des Stützkondensators liegt zwischen 1 und 10 nF. Da das Integrieren von Kapazität in den IC Kosten verursacht, sollte der notwendige Wert durch Simulation ermittelt werden. Seit etwa 2005 wurde begonnen, zusätzlich Abblockkondensatoren mit einigen nF in ICs zu integrieren.

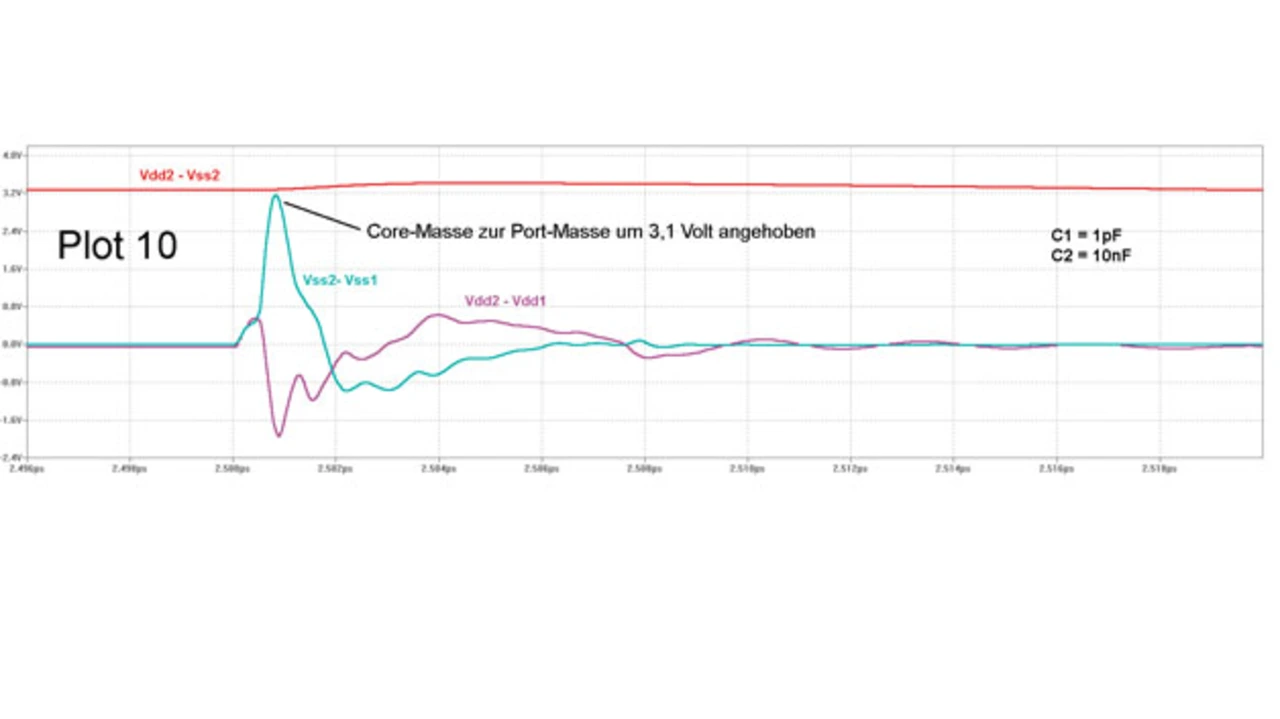

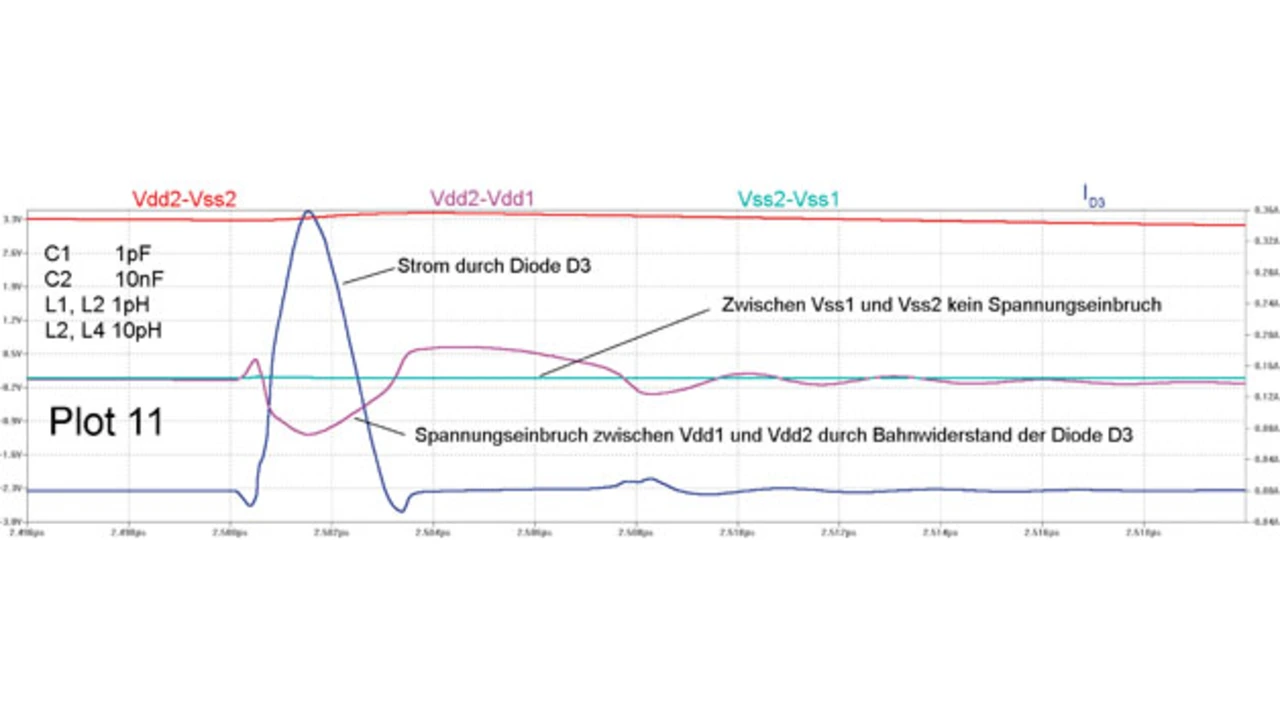

Damit ist das Beeinflussungsproblem des ICs noch nicht vollständig gelöst. Im Bild 5, Plot 09 wird die Spannung Vdd und Vss im Gleichtakt um 3,1 Volt angehoben. Wenn der Port-Bereich Bild 2 mit dem Core-Bereich verbunden wird, werden diese Gleichtaktimpulse als Differenz zwischen den beiden Bereichen stehen. Das kann Signalverbindungen stören. Dieses Fehlerprinzip kann auch zwischen anderen getrennt versorgten Bereichen wirken wie z.B. bei PLLs, Quarzoszillatoren oder Speichern.Für den Plot 10, Bild 6 wurde die gesamte Schaltung Bild 2 aktiviert. Dabei war der Port-Bereich mit C1 = 1pF nicht und der Core-Bereich mit C2 = 10 nF gut abgeblockt. Das entspricht praktischen Anordnungen. Es entstehen Differenzspannungen von reichlich 3 Volt zwischen den Versorgungen beider Bereiche. Diese Differenzspannungen können zwischen den Bereichen liegende Signalverbindungen stören. Wenn man den Portbereich ebenfalls mit 10 nF abgeblockt wird die Differenzspannung gemindert. Das erfordert zusätzliche Kapazität, die in einem IC wirtschaftlich nicht realisierbar ist. Eine bessere Lösung erzielt man mit der Verminderung der Längsinduktivitäten L1 bis L4 des internen Vdd / Vss Systems und erreicht damit, dass die externen Stützkondensatoren wirken können. Niederimpedante und flächige Versorgungssysteme sind Bestandteil einer Entstörstrategie, die auf Bordebene ca. 1995 mit großem Erfolg eingeführt wurde. Auf ICs angewendet ist das Ergebnis ist in Bild 7 dargestellt.

Jobangebote+ passend zum Thema

Die Wirkung ist deutlich, zwischen Vss1 und Vss2 gibt es keinen Spannungseinbruch mehr, nur der Bahnwiderstand, der in der Simulation verwendeten Dioden erzeugt noch einen Einbruch zwischen Vdd1 und Vdd2 von ca. 1 Volt.

Praktisch bedeutet das eine Vermaschung des Vdd / Vss Systems. Vdd und Vss müssten je eine separate Metalllage im Die des IC erhalten. Die Metalllagen müssten, um entsprechend niedrige Induktivitätswerte zu erhalten, aus eng vermaschten Leitungsnetzen oder aus einer geschlossenen Metallfläche bestehen. Das widerspricht der Tradition des IC Designs. Nach dieser wurden bisher intern sternförmige Versorgungsnetze verwendet, die eine hohe Längsinduktivität besitzen. Die Verbindung der Versorgungsinseln erfolgte erst auf dem Board. Auf Grund dieser Tatsache waren die ICs unzureichend störfest. Für den Anwender entstanden zusätzlicher Entwicklungsaufwand und zusätzliche Kosten zur Entstörung der Elektronikbaugruppen. Aus Tradition hat man den Weg der inneren sternförmigen Leitungsführung nicht verlassen.

Als auf Bordebene Mitte der neunziger Jahre die Umstellung von Stern- auf Vermaschte- oder Flächen-Massesysteme begann, stieß dieses Vorhaben auf erhebliche Widerstände unter den Fachleuten, man glaubte aus Tradition an die sternförmigen Massesysteme. Der Erfolg nach der Umstellung überzeugte schließlich. Dennoch dauerte die Umstellung in den Firmen meist mehrere Jahre und ist noch nicht komplett abgeschlossen.

Bei den ICs ist erst jetzt die Zeit reif, mit einer derartigen Umstellung zu beginnen.

Aus der Methode der pingranularen Störfestigkeitsuntersuchungen an ICs lassen sich eine Reihe von Erkenntnissen gewinnen, die in der Zukunft zu robusteren ICs führen werden, trotz der fortschreitenden Erhöhung der Integrationsdichte und der damit verbundenen höheren Störempfindlichkeit. Hier die Erkenntnisse:

1. steilflankige Störströme fliesen über Schutzdioden in das Vdd / Vss- Netz

2. es kommt zu Spannungseinbrüchen im Vdd / Vss System

3. in Abhängigkeit von internen Induktivitäten und realisierbaren Kapazitäten kann es zu Einschwingvorgängen im Vdd / Vss System kommen

4. es kommt zu induktivitätsbedingten Längsspannungsabfällen im Vdd / Vss System, zu Spannungsdifferenzen zwischen entkoppelten Bereichen

5. interne Kapazitäten geeigneter Größe helfen, diese Vorgänge zu minimieren

6. zielführend ist eine Vermaschung der Versorgungssysteme auf IC-Ebene

Autoren:

Dipl. Ing. Gunter Langer, Geschäftsführer der Langer EMV-Technik GmbH

Dipl.-Ing. Gunter Grießbach, Gruppenleiter Siemens AG in Chemnitz

- ICs als EMV-Schwachstellen: Probleme beseitigen

- Den inneren Aufbau des ICs mit einbeziehen

- Moderne ICs leiden unter schnellen Störimpulsen

- Lösung der Beeinflussungsprobleme