Medizin-Algorithmen

Ultraschnell, Ultraschall

Fortsetzung des Artikels von Teil 1

Vorteile adaptiver SoCs

Xilinx Versal-basierte adaptive SoCs sind die neueste Generation der Adaptive Compute Acceleration Platform (ACAP) mit eng gekoppelten Multiprozessoren, einem FPGA und der neuen 'intelligenten Engine' oder AI Engine (AIE) mit einer hochparallelen gekachelten SIMD-VLIW Architektur. SIMD steht für 'Single-Instruction-Multiple-Data' und VLIW für 'Very Long Instruction Word'. Die verschiedenen Blöcke sind über die NoC- oder 'Network-on-Chip'-Architektur eng miteinander verbunden, was einen schnellen Datenaustausch zwischen den verschiedenen Blöcken ermöglicht.

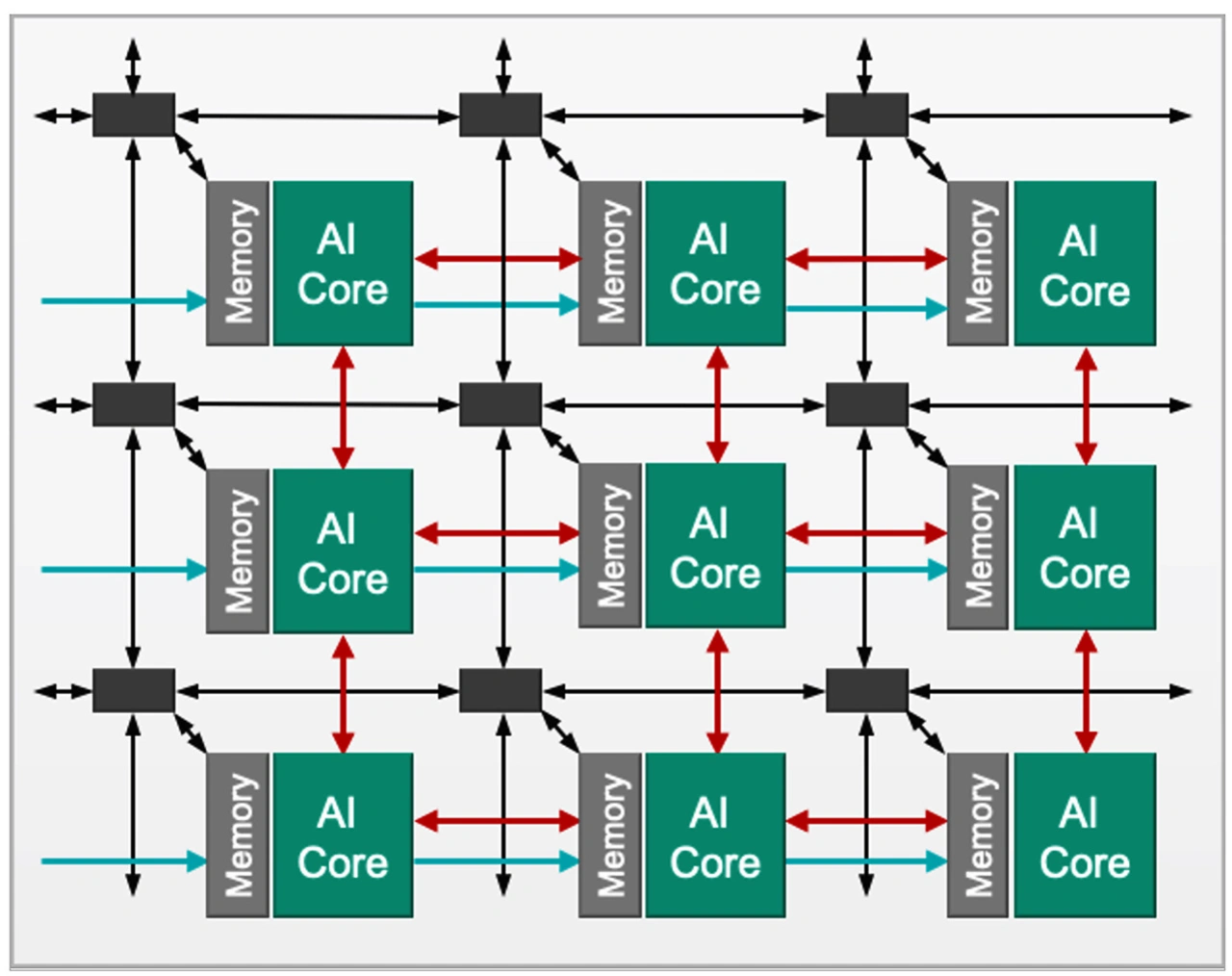

Die AIE ist die Hauptrecheneinheit für die ultraschnellen Algorithmen (wie Planar Wave und Synthetic Aperture). Es handelt sich um eine große Matrix von SIMD/VLIW-Prozessoren, die in einem Netz verbunden sind (siehe Bild 1). Jeder Prozessor hat seinen eigenen Befehls- und Datenspeicher und kann den Speicher mit seinen Nachbarn teilen. Alle Prozessoren sind über einen innovativen Interconnect mit einer enormen Bandbreite von mehreren TeraBytes pro Sekunde verbunden. Diese Struktur ermöglicht ein noch nie dagewesenes Maß an Parallelität, das für die Implementierung solcher Algorithmen erforderlich ist.

Diese neue adaptive Computing-Architektur mit dem AIE-System ermöglicht es den Herstellern medizinischer Geräte, Algorithmen mit sehr hoher Datenrate zu implementieren, z.B. in parallelen Software-Beamformern, die Echtzeit-Scans oder 3D/4D-Visualisierung, AI-ML für die Auswahl der Region-of-Interest, Unterstützung bei der Dateninferenz und Entlastung bei der Bildrekonstruktion in der Endoskopie, der Roboterchirurgie und in der Radiologie mit einem einzigen vollständig eingebetteten Baustein realisieren.

Mit Hilfe dieses neuen adaptiven SoCs hat AMD-Xilinx in Zusammenarbeit mit Dr. Joergen Jensen von der Technischen Universität Dänemark einen praxisgerechten UltraFast Beamformer entwickelt. Dr. Jensen half bei der Entwicklung der Algorithmen und AMD-Xilinx implementierte Partner diesen Beamformer in einem Referenz-Design zusammen mit Softwarebibliotheken für den adaptiven Versal-SoC.

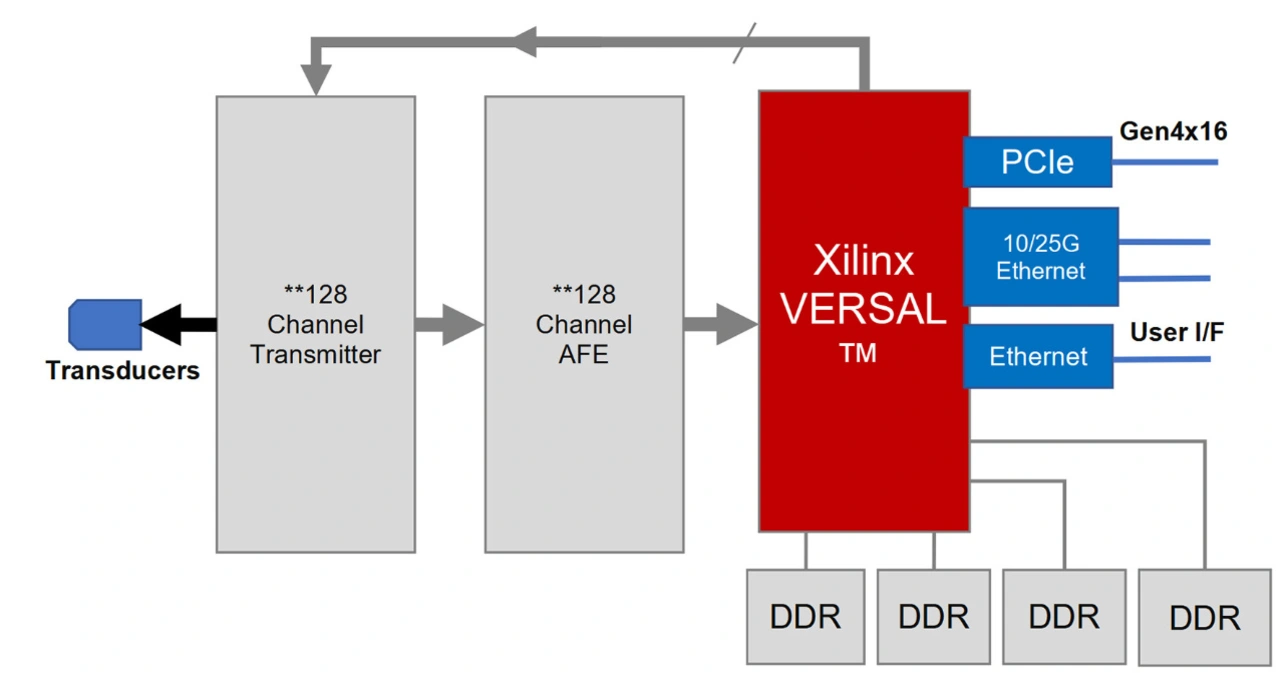

Das Blockdiagramm unten (Bild 2) ist eine High-Level-Darstellung eines UltraFast-Beamformers auf einem einzigen Versal adaptive SoC, der FPGA, CPU und Hardwarebeschleuniger für KI und digitale Signalverarbeitung kombiniert.

Der FPGA, der Teil des Bausteins ist, verwaltet die Wandler und erfasst die Echos, speichert die Daten in externen DDR4-Speichern und kann über einen PCIe-Anschluss mit dem Host-System kommunizieren oder über das Precision Time Protocol und 10/25-Gigabit-Ethernet-Kanäle mit einem anderen Modul erweitern und synchronisieren.

Die wichtigsten Leistungsmerkmale:

- Mit einem einzigen adaptiven Versal-SoC lässt sich ein UltraFast-basierter Beamformer betreiben und eine extrem hohe Leistung erzielen.

- Implementierung eines vollständigen Software-Beamformers mit der Xilinx Vitis Software-Entwicklungsumgebung mithilfe von Hochsprachen wie C/C++

- Aktivierung von Vitis-Beschleunigungsbibliotheken, die in einem medizinischen Gerätedesign verwendet werden können oder als Beispieldesigns, um die hauseigenen Algorithmen des Medizinprodukteherstellers zu implementieren.

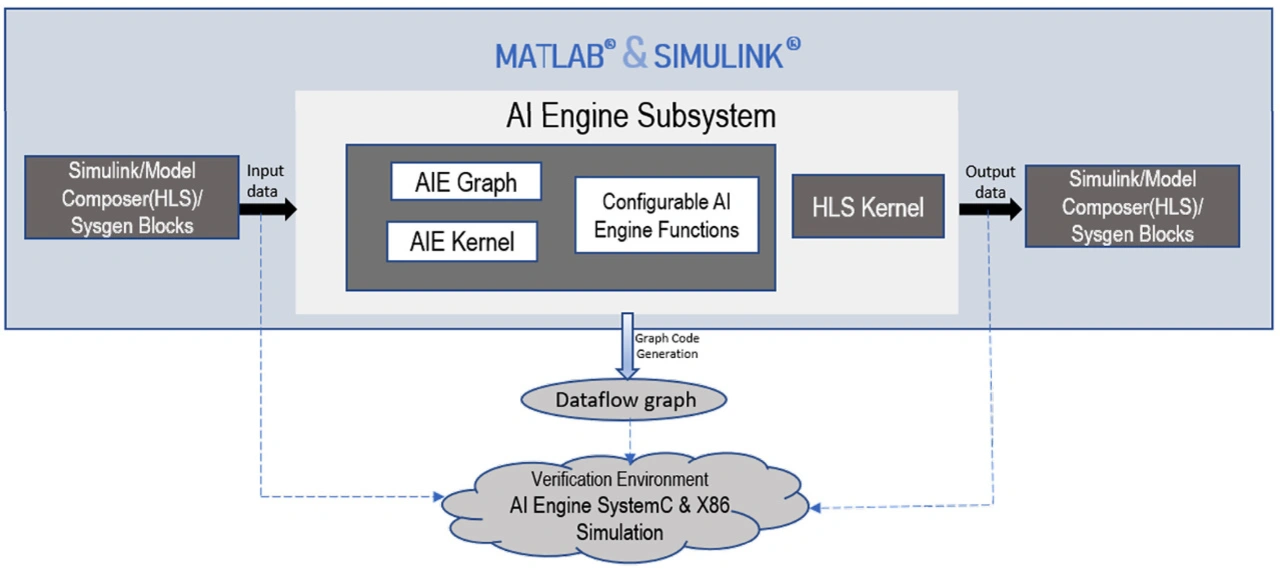

Matlab Support wird über den Model Composer angeboten, einem modellbasierten Design-Tool, das ein schnelles Design in der Matlab- und Simulink-Umgebung ermöglicht und den Weg zur Produktion von adaptiven Versal-SoC-Bauteilen durch automatische Codegenerierung beschleunigt. Dies wird durch eine Reihe von C++-Vorlagen verstärkt, die die grundlegende API der KI-Engines umhüllen (Bild 3).

- Ultraschnell, Ultraschall

- Vorteile adaptiver SoCs

- Demonstration unter Real-Bedingungen