Starter-Kit

SoCrates "wirbelt Probleme weg"

Fortsetzung des Artikels von Teil 5

Software-Entwicklung und -Debugging

Ein unstrittiger Vorteil eines SoC-FPGA wie Cyclone V ist die Tatsache, dass Applikationen, für die bislang Mehrchip-Lösungen wie z.B. Freescales i.MX für Linux auf einem Applikationsprozessor in Verbindung mit einem Kine-tis-Mikrocontroller notwendig waren, sich dank der Flexibilität der FPGA-Logik in einem Chip integrieren lassen. Damit braucht man nicht mehr verschiedene Tool Flows; der Aufwand für Wartung und Pflege der Software sinkt.

Was allerdings von den FPGA-Herstellern gerne vergessen wird, zu erwähnen, ist die Tatsache, dass man für ein Cyclone V und andere FPGA-SoCs normalerweise ebenfalls zwei getrennte Tool Flows braucht (Bild 5) – einen für die FPGA-Logik und einen für das ARM-Prozessor-System. Was erschwerend hinzukommt und gerne ignoriert wird, ist die Tatsache, dass die Anzahl der FPGA-Entwickler speziell bei mittelständischen Unternehmen, die bislang mit MPUs und MCUs gearbeitet haben, sehr limitiert ist – VHDL ist leider nunmal grundsätzlich anders als C++.

Altera hat als Nachfolger des SOPC Builder eine Software namens QSys herausgebracht, welche dieses Problem löst. IP-Peripherie-Blöcke, die in die FPGA-Logik integriert werden sollen, können dabei einfach mittels einer grafischen Benutzeroberfläche eingebunden werden – ganz ohne VHDL-Kenntnisse. Qsys besitzt einen komplett neu entworfenen sogenannten „switching fabric generator“. Der Generator des SOPC Builder ist ein festes, unflexibles und teils veraltetes Perl Script. Der Qsys-Generator ist modularer und mit besseren Algorithmen ausgestattet. Vor allem erhofft man sich mit dem neuen Generator die Erzeugung von deutlich schnelleren und performanteren Designs.

Anschließend kann der sogenannte Hardware/Software Handoff vorgenommen und mit den bekannten Tools wie dem ARM-Entwicklungssystem weitergemacht werden. Und damit wartet schon die zweite Herausforderung, nämlich das parallele Debugging von FPGA-Logik und Prozessor.

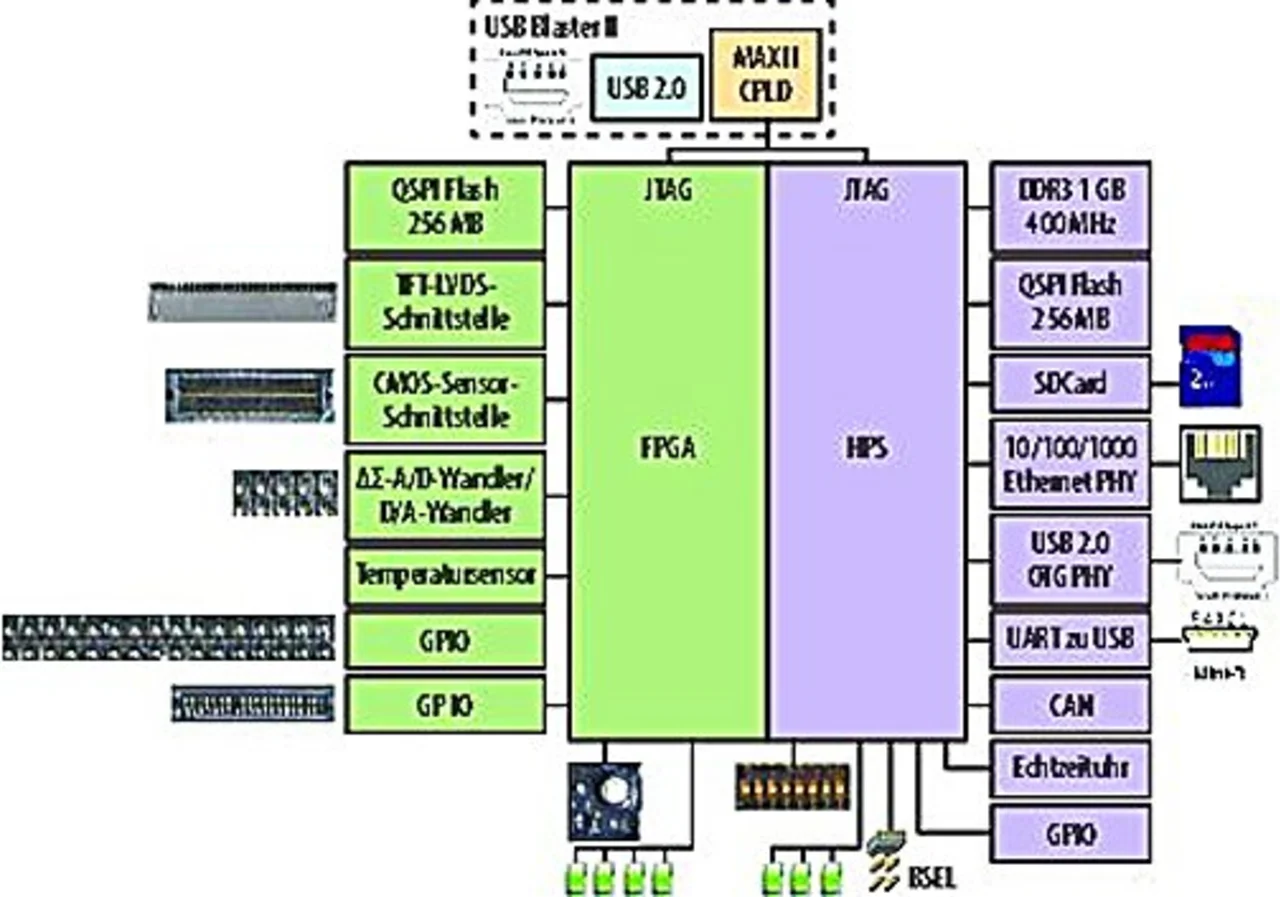

Ein herkömmlicher Ansatz wäre, jeweils über eine dedizierte JTAG-Schnittstelle mit ARMs DS-5 Toolkit sowie Alteras Software Quartus II zu debuggen. Ersteres visualisiert und steuert das CPU-Subsystem, zweiteres die FPGA-Logik. Das Problem ist, einen zeitlichen Zusammenhang zwischen Aktivitäten beider Domänen herzustellen.

Als Lösung dieses Problems hat Altera exklusiv mit ARM eine ARM Development Studio 5 (DS-5) Altera Edition Toolkit genannte Lösung entwickelt, die über eine Logikzellen-Debugging-Erweiterung des Standard-Kit die Debugging-Barriere zwischen CPUs und FPGA-Logik beseitigt – und die Alteras Konkurrent Xilinx dank eines Exklusivitätsabkommens nicht zur Verfügung steht. Über den USB-Blaster kann ein Co-Debugging über beide Domänen (HW/SW) vorgenommen werden, z.B. indem ein Trigger aus dem SignalTap-II-Logikanalysator (enthalten im Quartus-II-Entwicklungspaket) gesetzt wird und anschließend Zeitstempel-korrelierte Ereignisse in HW und SW analysiert werden können. Der Logikanalysator ermöglicht also Unterbrechungen auch in der Software.

Jobangebote+ passend zum Thema

- SoCrates "wirbelt Probleme weg"

- Leistungsmerkmale des Cortex-A9

- Entlastung für den Hauptbus

- Hoher Umrechnungsfaktor für DSP-Blöcke

- Zwei Transceiver-Arten

- Software-Entwicklung und -Debugging

- SoCrates verbindet Cyclone mit der Umwelt