Starter-Kit

SoCrates "wirbelt Probleme weg"

Fortsetzung des Artikels von Teil 3

Hoher Umrechnungsfaktor für DSP-Blöcke

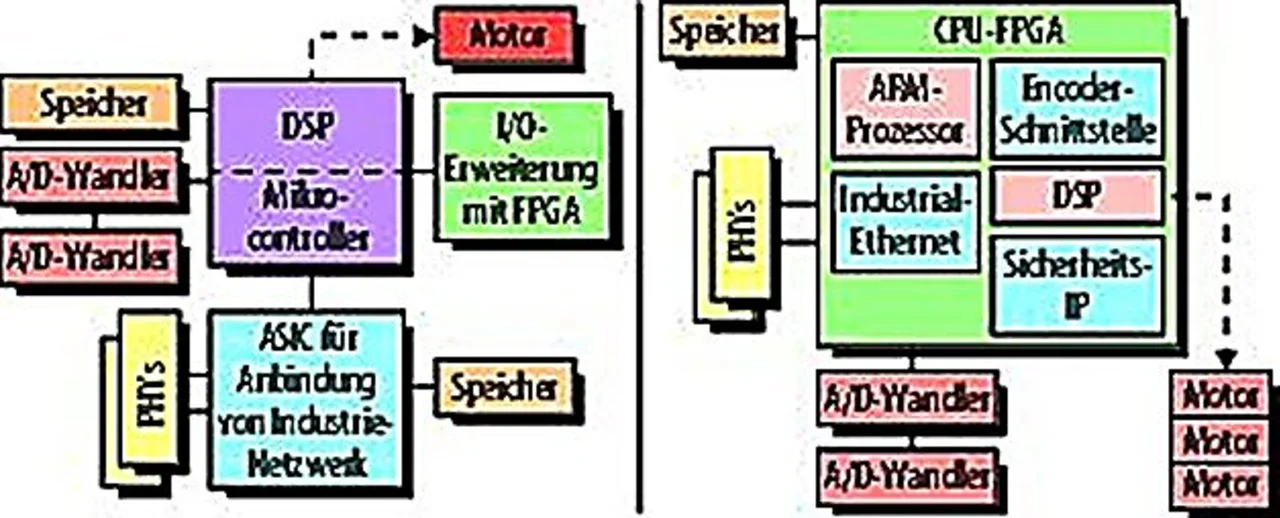

Besonders interessant erscheint in Alteras Formel der hohe Umrechnungsfaktor für DSP-Blöcke. Zum einen sorgen die Hardware-Multiplizierer dafür, dass sie vom Kunden nicht in vergleichsweise langsamen Logikelementen implementiert werden müssen, zum anderen sind sie so leistungsfähig, dass FPGAs in vielen High-End-Systemen sogar DSP-Farmen ersetzen können. In Bild 4 ist ein Anwendungsbeispiel aus dem Bereich Motorsteuerung zu sehen.

Alteras SoCs beinhalten bis zu 112 DSP-Blöcke pro Chip. Bei jedem Block handelt es sich um eine Funktionseinheit, die mit unterschiedlicher Präzision rechnen kann – entweder als 27×27-bit-Multiplizierer, mit zwei 18×19-bit-Multiplizierern oder drei 9×9-bit-Multiplizierern. Ein 64-bit-Akkumulator sorgt für eine höhere Genauigkeit vor dem Runden oder Abschneiden von Nachkommastellen. Für Gleitkommaoperationen nutzt Altera die 27×27-bit-Multiplizierer. Beim Abschätzen der ASIC-Gatter zählt Altera jeweils zwei 18×19-bit-Multiplizierer pro DSP-Block unter der Annahme, dass man in einem ASIC 5000 Gatter für die Implementierung vergleichbarer Logik benötigen würde. Wenn natürlich ein Design nicht alle Multiplizierer ausnutzt, reduziert sich die Anzahl der ASIC-Gatter entsprechend. Realistisch dürfte in Summe ein Bereich von 300.000 bis 1,4 Mio. für Cyclon-V-Chips sein.

Ähnliche Überlegungen muss man hinsichtlich der Rechenleistung der DSP-Blöcke anstellen. Um die Gesamtleistung in GMACs/s zu berechnen, nutzt Altera die 18×19-bit-Multiplizierer bei der Ausführung einer FIR-Filterfunktion. Bei Nutzung der 27×27-bit-Multiplizierer halbiert sich dieser Wert, für die Ermittlung von „GMAC-Rohwerten“ kann man sie ungefähr verdoppeln. Um die Cortex-A9-Cores mit Neon-Erweiterungen, FPU und zugehöriger Peripherie in einem ASIC abzubilden, müsste man schätzungsweise nochmal mindestens 1 Mio. Gatter investieren.

Die grundsätzlichen Aussagen, dass FPGAs mit DSP-Blöcken eine wesentliche höhere Rechenleistung im Bereich digitaler Signalverarbeitung als DSPs bieten, ist ebenso wenig neu wie die Erkenntnis, dass die Programmierung noch komplexer ist. Schon seit Jahren werden DSPs und ASICs durch FPGAs ersetzt, wie die Wachstumsraten der FPGA-Industrie beweisen. Was allerdings neu ist, ist die hohe Integrationsdichte einer im Feld umprogrammierbaren Ein-Chip-Lösung.

Jobangebote+ passend zum Thema

- SoCrates "wirbelt Probleme weg"

- Leistungsmerkmale des Cortex-A9

- Entlastung für den Hauptbus

- Hoher Umrechnungsfaktor für DSP-Blöcke

- Zwei Transceiver-Arten

- Software-Entwicklung und -Debugging

- SoCrates verbindet Cyclone mit der Umwelt