Starter-Kit

SoCrates "wirbelt Probleme weg"

Fortsetzung des Artikels von Teil 2

Entlastung für den Hauptbus

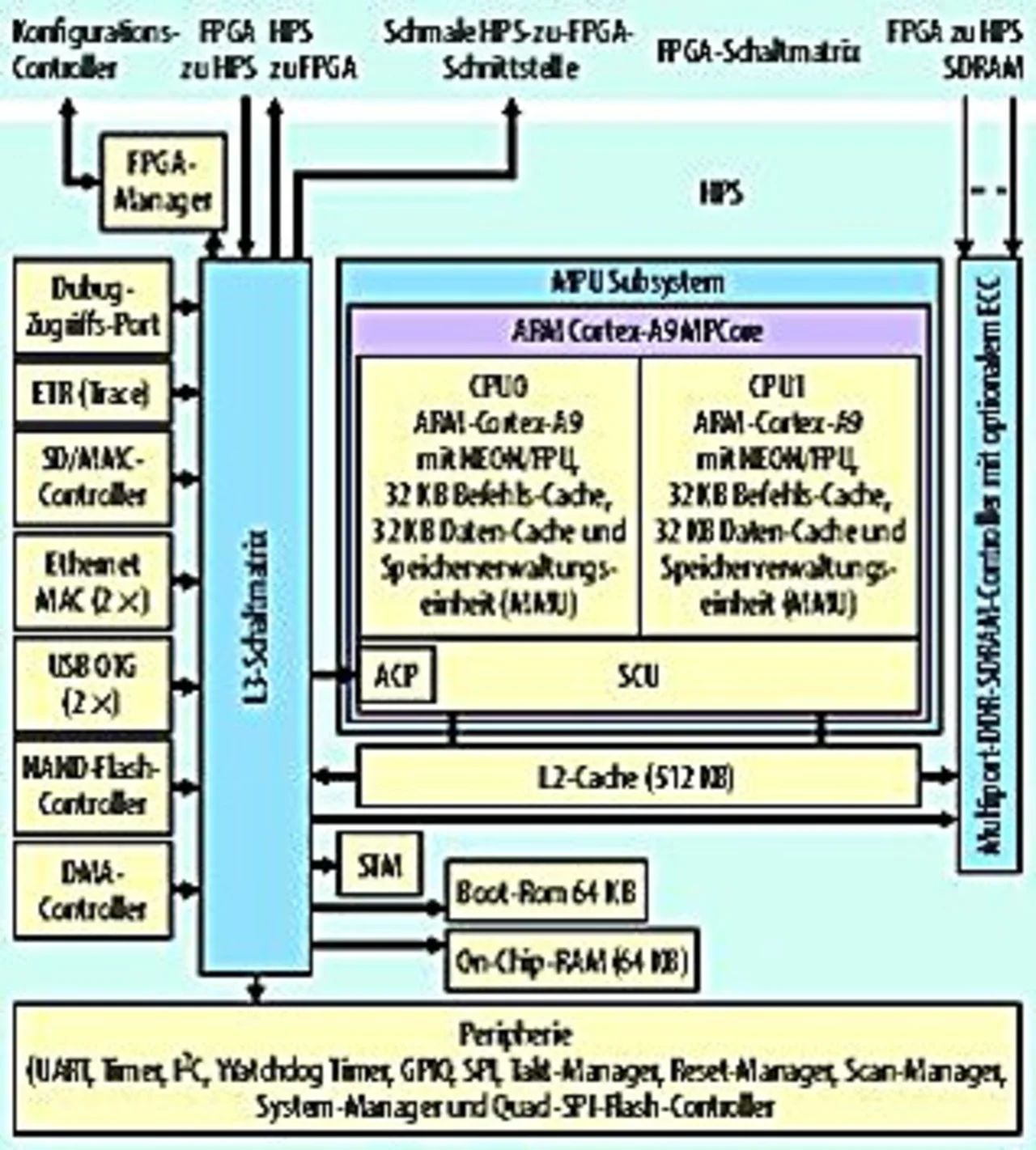

Der 32 bit-AXI-Bus soll den 128 bit-Hauptbus bei zeitunkritischen Transfers entlasten, um potenzielle Datenkollisionen auf diesem zu verringern. Wenn ein Design weniger Bandbreite zwischen CPUs und Logik benötigt, kann man durch eine entsprechende Konfiguration als 32- oder 64 bit-Bus etwas Energie einsparen. Bild 3 zeigt die Schnittstellen zwischen HPS und FPGA-Logik.

Genug Gatter für große Designs

Neben der Leistungsaufnahme ist natürlich die Anzahl der Logikelemente das wichtigste Kriterium für ein CPU-FPGA, da sie ja festlegt, ob ein bestimmtes Design in den Chip passt oder nicht. Alteras Cyclone-V-SoCs bieten einen weiten Bereich von 25.000 bis 110.000 „Logikelementen“, Alteras Bezeichnung für die programmierbaren Lookup-Tabellen (LUTs) und die zugehörigen Schaltkreise. Entwickler, die Designs mit separatem Prozessor und FPGA ersetzen wollen, kennen diese Nomenklatur natürlich; diejenigen, die ein ASIC ersetzen wollen, müssen ASIC-Gatter in Logikelemente umrechnen – eine undankbare Aufgabe. Viel hängt nämlich von der Art des Designs, dem Synthese-Compiler und den Place-and-Route Tools ab. Altera selbst rechnet für ASIC-Gatter 12 × die Anzahl der LUTs plus 5000 × die Anzahl der 18×19-bit-Multiplizierer, von denen pro DSP-Block jeweils zwei vorhanden sind. Daraus ergibt sich für die Cyclone-V-Derivate eine Kapazität von 660.000 bis 2,6 Mio. ASIC-Gattern.

Allerdings kann auch hier wie bei herkömmlichen FPGAs kein reales Design alle LUTs ausnutzen.

Jobangebote+ passend zum Thema

- SoCrates "wirbelt Probleme weg"

- Leistungsmerkmale des Cortex-A9

- Entlastung für den Hauptbus

- Hoher Umrechnungsfaktor für DSP-Blöcke

- Zwei Transceiver-Arten

- Software-Entwicklung und -Debugging

- SoCrates verbindet Cyclone mit der Umwelt