Starter-Kit

SoCrates "wirbelt Probleme weg"

Fortsetzung des Artikels von Teil 1

Leistungsmerkmale des Cortex-A9

Eine weitere Eigenschaft, welche die Rechenleistung erhöht, ist die dynamische Sprungvorhersage, die u.a. mittels einer 512 Byte großen Sprunghistorientabelle realisiert wird. Damit lässt sich in vielen Fällen verhindern, dass Befehle unnötig geladen und dekodiert sowie die Instruktions-Pipeline unnötig gefüllt wird und gelöscht werden muss, wenn ein Verzweigungsbefehl abgearbeitet werden muss und die Codeausführung an einer ganz anderen Adresse fortgesetzt wird.

Die Cortex-A9-Cores kommen zusammen mit Neon und FPU und werden mit 800 MHz getaktet – damit bewegen sich die Chips auf einem Leistungsniveau, das mit vielen der schnellsten ASICs und ASSPs mithalten kann.

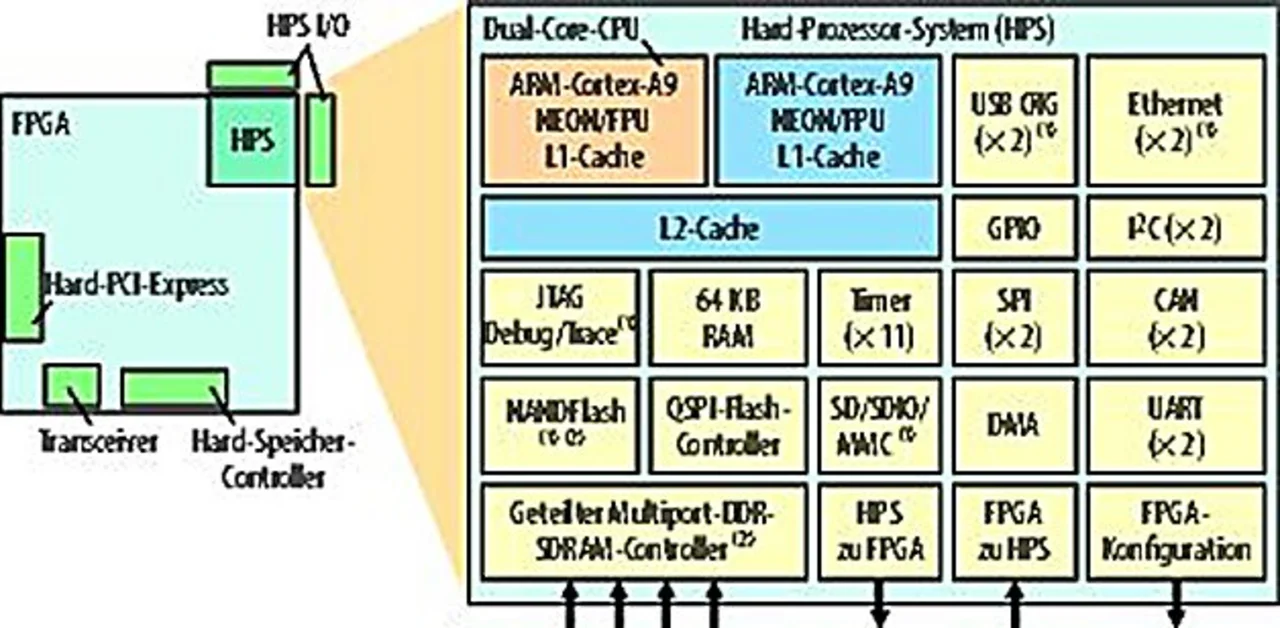

Zusätzlich zu jeweils 32 KB L1-Cache für Daten und Instruktionen pro Core gibt es noch 512 KB zwischen den Cores geteilten L2-Cache, 64 KB SRAM, 64 KB Boot-ROM und einen Speichercontroller für externen Speicher, der neben Low-Power-DRAM natürlich auch konventionellen DDR2- und DDR3-Speicher unterstützt. Der von Altera selbst entwickelte Controller taucht in den SoCs in seiner vierten Generation auf und ist derart konfigurierbar, dass 8-, 16- und 32 bit-Schnittstellen zum Hauptspeicher unterstützt werden. Alle Caches, Speicher und Puffer unterstützen entweder Paritätsbits oder ECC, um gegen Soft Errors gewappnet zu sein.

Bild 2 zeigt das sogenannte Hard Processor System (HPS) mit seinen I/O-Schnittstellen. Einen riesigen Unterschied zu den – diplomatisch formuliert – optimierungsfähigen Bussen zwischen CPU und Logikzellen der früheren CPU-FPGAs stellen die zwei mit jeweils 400 MHz getakteten AMBA-3-AXI-Busse dar. Einer ist auf eine Breite von 32, 64 oder 128 bit konfigurierbar und der zweite arbeitet fix mit 32 bit. Zusammen werden damit bei den Cyclone-V-Derivaten Übertragungsraten von mindestens 100 Gbit/s erreicht. Diese Zahlen variieren hinsichtlich der erzielten Taktfrequenz der FPGA-Logik, die ihrerseits von der Design-Komplexität abhängt – größere Designs laufen in der Regel langsamer. Laut Altera basieren die Angaben auf der Standard-Ausgabe ihres Design-Tools Quartus II, nicht auf einer handoptimierten Logik für die Erreichung maximaler Geschwindigkeit.

Jobangebote+ passend zum Thema

- SoCrates "wirbelt Probleme weg"

- Leistungsmerkmale des Cortex-A9

- Entlastung für den Hauptbus

- Hoher Umrechnungsfaktor für DSP-Blöcke

- Zwei Transceiver-Arten

- Software-Entwicklung und -Debugging

- SoCrates verbindet Cyclone mit der Umwelt