Kleiner und billiger

Entwurf einer FPGA-HD-SDI-Image-Engine

Fortsetzung des Artikels von Teil 1

Einsatz der Evaluierungsplattform

Nachdem die Software und die IP festgelegt waren, kümmerten sich die Entwickler um die ausgewählte FPGA-Technologie. Es musste festgestellt werden, ob die Lattice-ECP3-Bausteine den Erwartungen entsprachen. Um dies zu testen, wurde eine Evaluierungsplattform eingesetzt. Zwei Optionen standen zur Wahl: Das Lattice-I/O-Prototyping-Board mit ECP3-150, das eine DDR3-Schnittstelle, keine Video-Schnittstellen, aber zugängliche SERDES-Schnittstellen beinhaltet, oder die eVision-Video-Processing-Platform VSP150 mit ECP3-150, die vergleichbare Video-Schnittstellen (verschiedene Standards) und eine DDR2-Schnittstelle beinhaltet.

Da die Leiterplatte von Lattice die gewünschte DDR3-Konfiguration in vollem Umfang unterstützt und die DDR3-Schnittstelle ein wesentliche Verbesserung im Vergleich zum ersten Prototypen darstellt, war einen Entscheidung für die Lattice-IO-Proto-typing-Plattform schnell getroffen.

Jobangebote+ passend zum Thema

Funktionstest und Inbetriebnahme

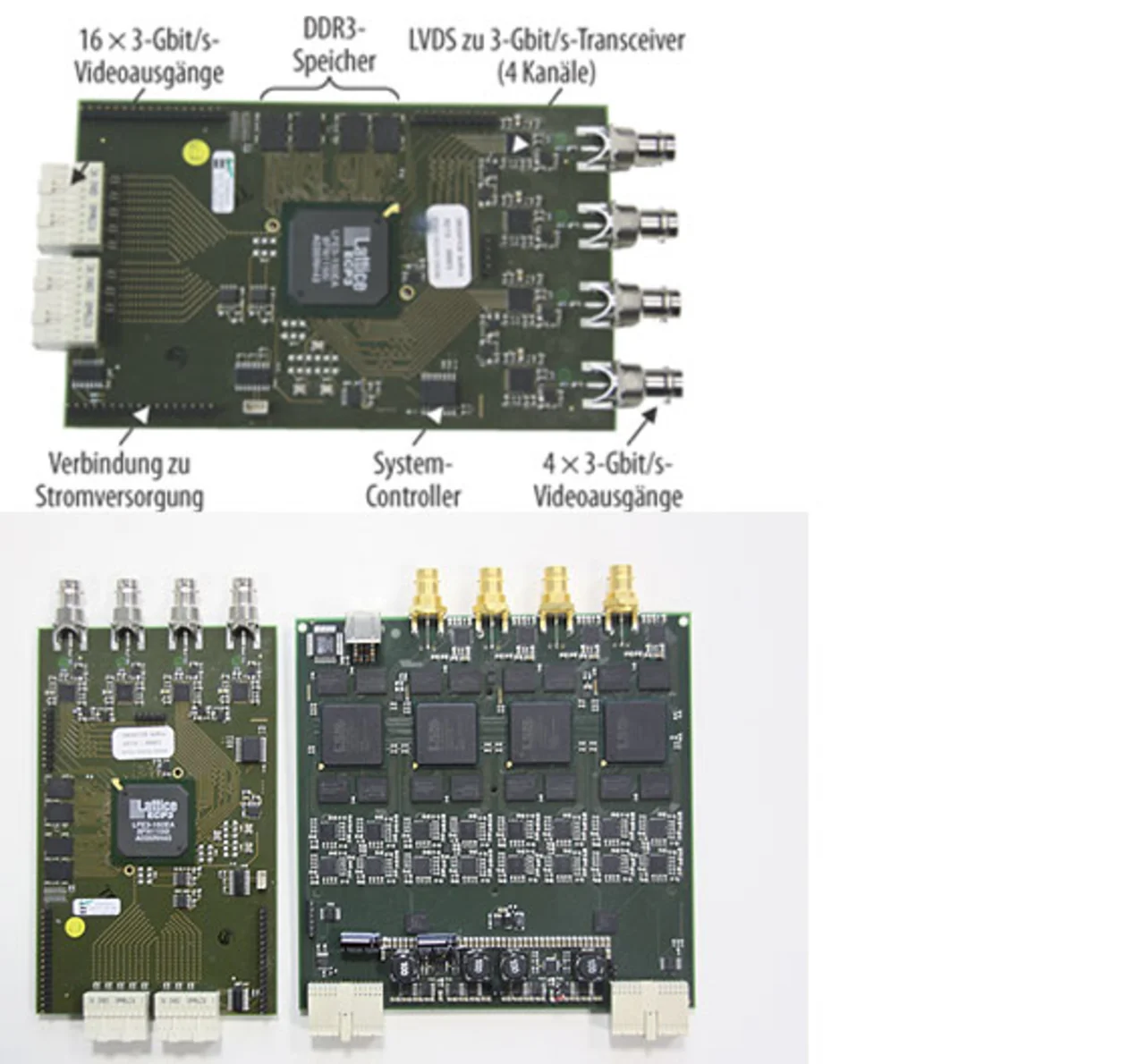

Die Stromaufnahme der Leiterkarte (Bild 6) lag im erwarteten Bereich. In der Zwischenzeit hatte Lattice eine neue Version des DDR3-IPs mit erweitertem Funktionsumfang veröffentlicht, der Umstieg auf die neue Version konnte problemlos vollzogen werden. Der DDR3-IP wurde in IPexpress neu erstellt und im VHDL-Projekt instanziiert.

Der fertige Funktionsprototyp konnte somit nach nur zweimonatiger Entwicklungszeit auf der Messe MEDICA in Düsseldorf ausgestellt werden. Als größte Vorteile des Lattice ECP3-150-FPGAs sind festzuhalten:

- Ausreichende Logikkomplexität mit der Option auf Erweiterung des Funktionsumfangs.

- 16 SERDES-Kanäle mit jeweils 3 Gbit/s.

- Unterstützung von schnellen LVDS-Schnittstellen (20 Paare mit je 600 Mbit/s).

- Funktionierender DDR3-IP-Core (64 bit, 800 Mbit/s) mit einem Datendurchsatz von 6,4 GB/s).

- Ausreichende Anzahl an Multiplizierern für die geplanten Skalierfunktionen.

- Interne Block-RAMs für Synchronisationszwecke und andere Systemfunktionen.

- Verfügbarkeit von PLLs.

In Bild 6 (unten) sind der alte und neue Prototyp der Image-Engine dargestellt. Die Materialliste (BOM) sowie die benötigte Leiterplattenfläche sind deutlich reduziert werden.

Die Autoren:

| Dipl.-Phys. Markus Imm |

|---|

| hat 1999 die Firma Imm & Bühler mitbegründet. Seit über 15 Jahren beschäftigt er sich mit Videoanwendungen. Er ist vornehmlich für Entwurf und Programmierung von FPGAs verantwortlich. Seinen Abschluss in Physik hat er 1994 an der Universität Karlsruhe erworben. |

m.imm@i-b-gmbh.de

| Friedlieb Bühler |

|---|

| ist Gründer und Geschäftsführer bei Imm & Bühler. Seit 1995 beschäftigt er sich mit C/C++. Er zeichnet im dargestellten Projekt Image Engine verantwortlich für die Benutzeroberfläche und die Gerätesteuerung. Ferner koordiniert er die Hardware-Fertigung. |

f.buehler@i-b-gmbh.de

| Dipl.-Ing. (FH) Lothar Brodbeck |

|---|

| arbeitet als FAE beim Distributor Arrow. Seit 1995 beschäftigt er sich mit programmierbarer Logik, zunächst als Entwickler bei Alcatel mit Altera, dann als FAE in der Distribution für Xilinx, Lattice und Altera. Seinen Abschluss in der Fachrichtung Nachrichtentechnik hat er 1991 an der FHT Esslingen erworben. |

lbrodbeck@arroweurope.com

- Entwurf einer FPGA-HD-SDI-Image-Engine

- Einsatz der Evaluierungsplattform