GaN-Treiber / Universität Reutlingen

Drei Stufen geben GaN-Transistoren Sicherheit

Fortsetzung des Artikels von Teil 2

Implementierung des Treibers

Das Gate-Treiber-IC wurde in einer Hochspannungs-BiCMOS-Technologie mit 0,18 μm hergestellt. Zu Messzwecken wurde der Kondensator CGS,add hinzugefügt, der die Gate-Kapazität künstlich erhöht (Bild 3, rechts). Als maximale Gate-Ladung Qmax stehen 11,6 nC zur Verfügung, die maximalen Gate-Treiberströme liegen bei 1,5 A (IGsource,max) bzw. 1,3 A (IGsink,max).

Der vorgestellte dreistufige Treiber unterstützt auch Gate-Injection-Transistoren (GIT). GITs sind GaN-Transistoren mit einer Diodencharakteristik am Gate (Bild 3, unten). Ein LDO liefert für das Gate einen Gleichstrom im Milliamperebereich, wenn der Treiber eingeschaltet ist. Bei Nicht-GIT-Bauelementen dient der LDO als Spannungsregler für VDRV. Lösungen wie ieee.org/document/7512256" href="http://ieeexplore.ieee.org/document/7512256">[2] erfordern dagegen einen zusätzlichen verlustbehafteten Widerstand parallel zu CGS. Der Doppelpulstest (Bild 4) bestätigt schnelle Transienten von über 80 V/3 ns für einen GIT im dreistufigen Betrieb bei einer Schaltspannung V+ von 100 V und einem Laststrom IL von 10 A.

Jobangebote+ passend zum Thema

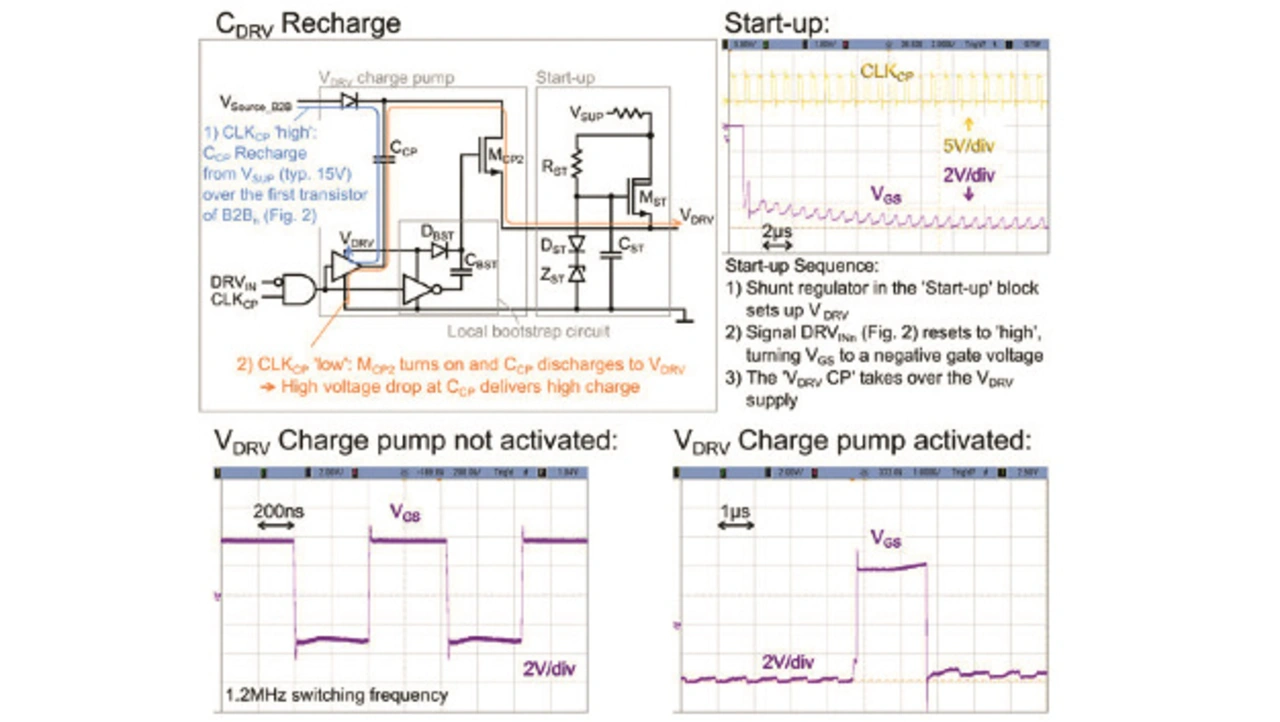

Der Gate-Treiber und die CHV-Ladungspumpe (Bild 2) liefern die Ladung für jeden Treiber-Schaltzyklus. In einigen Anwendungsfällen ist bei langen Phasen, wenn der Treiber ausgeschaltet bleibt, oder beim Starten der Applikation eine negative Gate-Spannung zuzuführen. Um VDRV zu erzeugen, lässt sich eine zusätzliche Ladungspumpe (VDRV Charge Pump) aktivieren (Bild 5), die nur den über VDRV entnommenen statischen Strom liefern muss. Der untere Teil von Bild 5 zeigt die Auswirkung der VDRV CP, die lange Ausphasen des Treibers unterstützt. Dies ist anders als bei deaktivierter VDRV CP (Bild 5, unten links). Hier versorgt sich der Treiber in einer Low-Side-Konfiguration während des eingeschalteten Zustandes des Treibers aus der CHV-Ladungspumpe und zusätzlich über VSUP. Bild 5 (oben rechts) zeigt, wie der Treiber startet.

| Parameter | Nagai [3] | Song [6] | Ke [7] | Bortis [2] | Seidel [5] | Seidel [4] |

|---|---|---|---|---|---|---|

| Prozesstechnologie | GaN auf Saphir | 0,35 µm BCD | 0,35 µm BCD | diskret | 180 nm BCD | 180 nm BCD |

| Idrv,max | 30 mA | N. R. | N. R. | N. R. | 1,3 A | 1,5 A |

| Bipolare Gate-Spannung | ja | nein | nein | ja | nein | ja |

| Dreistufige Gate-Spannung | nein | nein | nein | nein | nein | ja |

| Unterstützung für GIT-Transistoren | ja | nein | nein | ja | ja | ja |

| Pufferkondensatoren | 0 | N. R. | N. R. | 10 nF, zweiter Kond. N. R. | 1,7 nF, 0,6 nF | 3,6 nF, 2 × 0,6 nF |

| QG,max | N. R. | 133 pC (2) | 133 pC (2) | N. R. | 11 nC | 11,6 nC |

| Fläche der Pufferkondensatoren | 0 | 0,15 mm² (2) | 0,718 mm² (2) | N. R. | 1,4 mm² | 2,9 mm² |

| QG zu Fläche der Pufferkondensatoren | N. R. | 0,9 nC/mm² | 0,19 nC/mm² | N. R. | 7,6 nC/mm² | 4 nC/mm² |

| Flankensteilheit (max.) | N. R. | 20 V/1 ns | 40 V/1,5 ns, 40 V/1,2 ns | 400 V/2 ns (3) | N. R. | 80 V/3 ns, 80 V/2,8 ns |

Tabelle 1: Gegenüberstellung verschiedener Gate-Treiber für GaN-Transistoren (N. R. = Not Reported; (1) = aus Mikroskopaufnahme des Chips extrahiert, (2) = aus Datenblatt ECP8002, (3) = aus Diagramm extrahiert).

Die Gegenüberstellung zum Stand der Technik zeigt Tabelle 1. Der vorgestellte Treiber ist der einzige vollintegrierte Gate-Treiber, der eine dreistufige Gate-Treiberspannung (positiv/0 V/negativ) liefert. Ohne externe Kondensatoren liefert er bis zu 11,6 nC Gate-Ladung mit bis zu 1,5 A. Der Treiber unterstützt auch einen begrenzten Gate-Strom im eingeschalteten Zustand, um GaN-basierte Gate-Injection-Transistoren (GIT) anzusteuern.

Dieser Artikel basiert auf einem Papier aus dem Tagungsband der ISSCC 2018.

Referenzen

[1] Z. L. Zhang, et al., Three-Level Gate Drivers for eGaN HEMTs in Resonant Converters, IEEE Trans. Power Electronics, pp. 5527–5538, July 2017.

[2] D. Bortis, et al., Comprehensive Evaluation of GaN GIT in Low- and High-Frequency Bridge Leg Applications, IPEMC-ECCE Asia, pp. 21–30, May 2016.

[3] S. Nagai, et al., A DC-Isolated Gate Drive IC with Drive-by-Microwave Technology for Power Switching Devices, ISSCC, pp. 404–406, Feb. 2012.

[4] A. Seidel, et al., A Fully Integrated Three-Level 11.6nC Gate Driver Supporting GaN Gate Injection Transistors, ISSCC, pp. 384–386, Feb. 2018.

[5] A. Seidel, et al., A 1.3A Gate Driver for GaN with Fully Integrated Gate Charge Buffer Capacitor Delivering 11nC Enabled by High-Voltage Energy Storing, ISSCC, pp. 432–433, Feb. 2017.

[6] M. K. Song, et al., A 20V 8.4W 20 MHz Four-Phase GaN DC-DC Converter with Fully On-Chip Dual-SR Bootstrapped GaN FET Driver Achieving 4ns Constant Propagation Delay and 1ns Switching Rise Time, ISSCC, pp. 302-303, Feb. 2015.

[7] X. Ke, et al., A 3-to-40V 10-to-30 MHz Automotive-Use GaN Driver with Active BST Balancing and VSW Dual-Edge Dead-Time Modulation Achieving 8.3% Efficiency Improvement and 3.4ns Constant Propagation Delay, ISSCC, pp. 302-304, Feb. 2016.

- Drei Stufen geben GaN-Transistoren Sicherheit

- Aufbau der Treiberschaltung

- Implementierung des Treibers