GaN-Treiber / Universität Reutlingen

Drei Stufen geben GaN-Transistoren Sicherheit

Fortsetzung des Artikels von Teil 1

Aufbau der Treiberschaltung

Diese Arbeit ieee.org/document/8310345" href="https://ieeexplore.ieee.org/document/8310345">[4] stellt einen Gate-Treiber mit einer Vollbrückenarchitektur vor (Bild 1, unten rechts), der eine bipolare dreistufige Gate-Treiberspannung liefert. Da GaN-Transistoren in einem typischen Bereich für die Gate-Source-Spannung VGS von ±5 V arbeiten, lassen sich die vier Schalter der Treiber-Endstufe mit Niederspannungskomponenten realisieren. Abhängig von der Polarität der Brücke wird am GaN-Bauelement eine positive, eine negative oder 0 V als Gate-Source-Spannung angelegt.

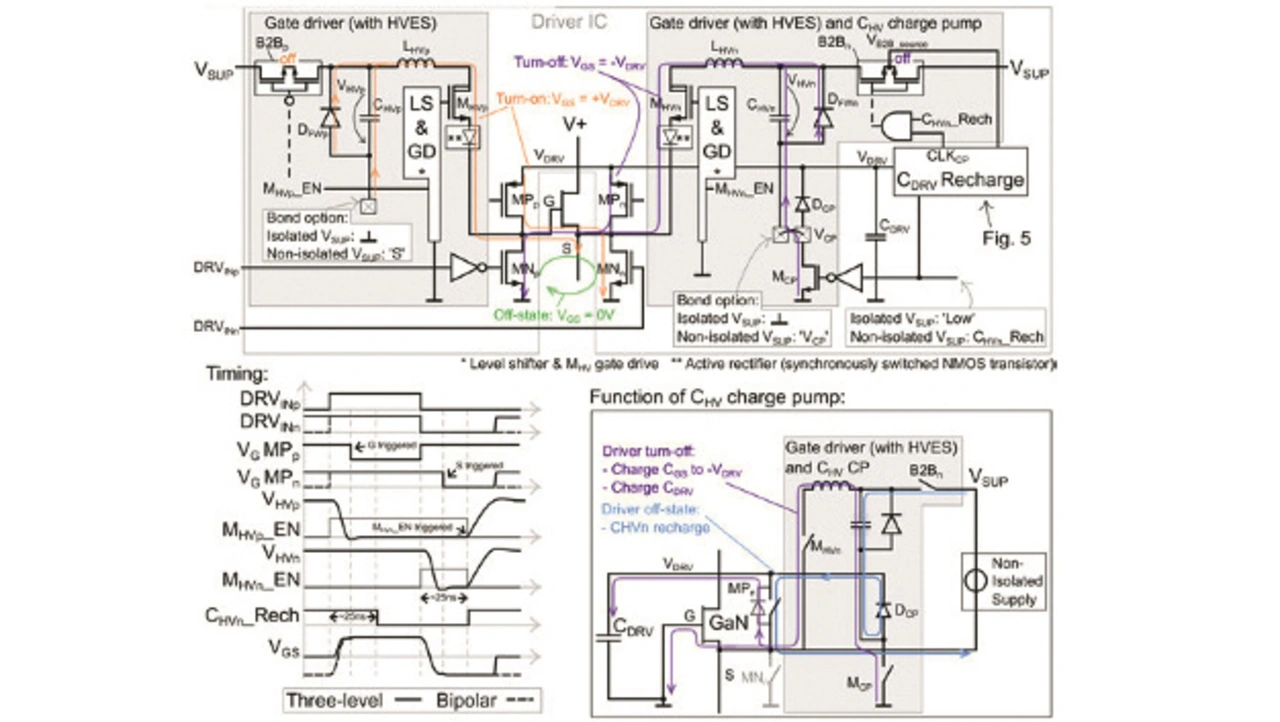

Um die Nachteile eines externen CDRV zu vermeiden, wird das Konzept der Hochspannungs-Energiespeicherung (High-Voltage Energy Storing, HVES) mit integriertem Pufferkondensator [5] sowohl am Gate- als auch am Source-Anschluss verwendet. Die integrierte Schaltung kann hohe Stromimpulse liefern, die auf einer resonanten Entladung eines Hochspannungskondensators über eine Induktivität zum Gate basieren. Da die Energie im Kondensator zum Quadrat seiner Spannung proportional ist (z. B. 15 V), kann die Schaltung eine hohe Menge an Ladung liefern und benötigt dabei eine sehr kleine Chipfläche. Eine sourceseitige Kondensator-Ladungspumpe (CHV CP) kann den Hochspannungspufferkondensator CHVn im abgeschalteten Zustand des Treibers aus einer nichtisolierten Treiberversorgung aufladen. Durch die Integration aller Kondensatoren reduziert diese Arbeit die Anzahl der Anschlüsse nach außen sowie die der Bonddrähte in der Gate-Schleife und bietet mehr Flexibilität für das Leiterplatten- und Systemdesign.

Jobangebote+ passend zum Thema

Bild 2, oben, zeigt den Aufbau des implementierten dreistufigen Gate-Treibers. Um den GaN-Schalter einzuschalten, schaltet sich MNp durch das Treiber-Steuersignal DRVINp aus. Bei einem bipolaren Treiberbetrieb geht DRVINn auf high, schaltet MPn aus und MNn ein, um die Source S zu entladen. MHVp schaltet ein und löst den Gate-Treiber (mit HVES) [5] aus, um das Gate G des GaN-Transistors über den Hochspannungskondensator CHVp (0,6 nF), die integrierte Induktivität LHVp (14 nH) und einen aktiven Gleichrichter resonant aufzuladen. Durch die ansteigende Spannung am Gate des GaN-Transistors schaltet sich MPp ein und hält dieses Gate über eine niederohmige und niederinduktive Verbindung konstant auf VDRV.

Um den GaN-Transistor wieder zu sperren, geht das Treibersignal DRVINp auf low, wodurch MPp aus- und MNp einschalten und sich das Gate entlädt. Gleichzeitig löst, getriggert durch DRVINn, der Hochspannungstransistor MHVn einen resonanten Stromimpuls über CHVn und LHVn aus und lädt den Source-Anschluss S. Der Strompfad schließt sich über MNp und den Niederspannungstransistor MCP der Ladungspumpe, der beim Abschalten des Treibers eingeschaltet ist. Durch die steigende Source-Spannung wird MPn leitend und verbindet die Source mit VDRV. Im dreistufigen Modus schaltet DRVINn vor dem nächsten Einschalten des Treibers auf high, schaltet MPn aus und entlädt die Source über MNn.

Bei einer galvanisch getrennten Treiberversorgung (Versorgungsmasse bezieht sich auf Chipmasse) lassen sich CHVp und CHVn problemlos über die Chipmasse laden. Um CHVp und CHVn aus der Treiberversorgung VSUP (typ. 15 V) aufzuladen, schalten sich die Back-to-Back-Schalter B2Bp und B2Bn ein, und der Strompfad schließt sich über die Kondensatoren und die Chipmasse.

Bei einer nicht galvanisch getrennten Versorgung (Bezugsmasse liegt auf der Source S) wird der Source-Knoten im ausgeschalteten Zustand des Treibers (negativer Gate-Pegel) mit VDRV verbunden. Da die negativen Elektroden von CHVp und CHVn mit der Chipmasse verbunden sind, würde der Ladestrom durch CDRV und MPn nach S fließen und damit CDRV (3,6 nF) entladen. Um dies zu vermeiden, lässt sich die negative Elektrode von CHVp mit dem Source-Knoten S des GaN-Transistors verbinden. Dies ist beim CHVn jedoch nicht möglich, da er beim Abschalten des Treibers eine Verbindung zur Chipmasse benötigt. Aus diesem Grund nutzt die hier eingesetzte CHV-Ladungspumpe (CHV CP), bestehend aus MCP und DCP, den Kondensator CHVn auch als Ladungspumpen-Kondensator. Bild 2, unten rechts, zeigt seine Funktion. Beim Abschalten des Treibers wird der Gate-Knoten G mit der Chipmasse kurzgeschlossen, während MCP aktiv ist, um den Source-Knoten S zu laden. Die Resonanzcharakteristik des Gate-Treibers mit HVES führt dazu, dass beim Ausschalten des Treibers die Spannung am Knoten S auf einen höheren Wert schwingt als VDRV, sodass sich CDRV über die Body-Diode von MPn auflädt.

Das gleiche CDRV-Ladeschema gilt auf der Gate-Seite beim Einschalten des Treibers. Nach dem Abschalten des Treibers schaltet sich MCP aus und CHVn wird über DCP und MPn direkt über die Source geladen. Wird der Treiber als Low-Side-Treiber verwendet, schaltet er also beispielsweise in einer Halbbrücke den unteren GaN-Transistor, kann dieser auch im eingeschalteten Zustand zur Verfügung stehen. Da die Chipmasse über MNn mit dem Knoten S verbunden ist, lassen sich dann mit dem gewählten Konzept alle auf Source bezogenen Kondensatoren aufladen.

- Drei Stufen geben GaN-Transistoren Sicherheit

- Aufbau der Treiberschaltung

- Implementierung des Treibers