Zukunft der Bauelemente

Chips 2020 – von der Nano- zur Femtoelektronik

Fortsetzung des Artikels von Teil 3

Die dritte Dimension

Es ist phänomenal, dass die Chips fast 50 Jahre zweidimensionale, planare integrierte Anordnungen von Transistoren im Sinne des Patents von Robert Noyce waren. In [1] wurde 2000 ein Schwerpunkt auf die dritte Dimension gelegt, und in der Branche wurde der Druck auf die Speicherdichte hin zu Solid-State Drives (SSD) mit mehr als 8 GB/Gehäuse so groß, dass 2005 die ersten Flash-Speicher mit internen Chip-Stapeln erschienen, deren elektrische Verbindungen durch TSVs (Through-Silicon Vias) hergestellt waren.

Für die Chip-zu-Chip-Verbindung hat die neuerdings massive Entwicklung dreidimensionaler Techniken wesentliche Fortschritte in Bezug auf neue Funktionen und Produkte, insbesondere auch für die Energieeffizienz der Systeme gebracht. Aus den Darstellungen in [10] und [11] gehen die neuen, diversifizierten Produktionsgemeinschaften für die heterogenen Prozesse hervor, die für die Zukunft immer mehr an Bedeutung gewinnen werden.

3D-Chip-Stapel brauchen neue Allianzen und Netzwerke für Wertschöpfung und Produktinnovation und leiten ein neues Ökosystem für die Nanoelektronik ein.

Neuromorphe Chips

Die erreichbaren Transistordichten und die 3D-Integration ermöglichen die ökonomische Realisierung hochparalleler und hierarchischer Schaltungsarchitekturen mit verteilter Intelligenz und Lernfähigkeit.

Jobangebote+ passend zum Thema

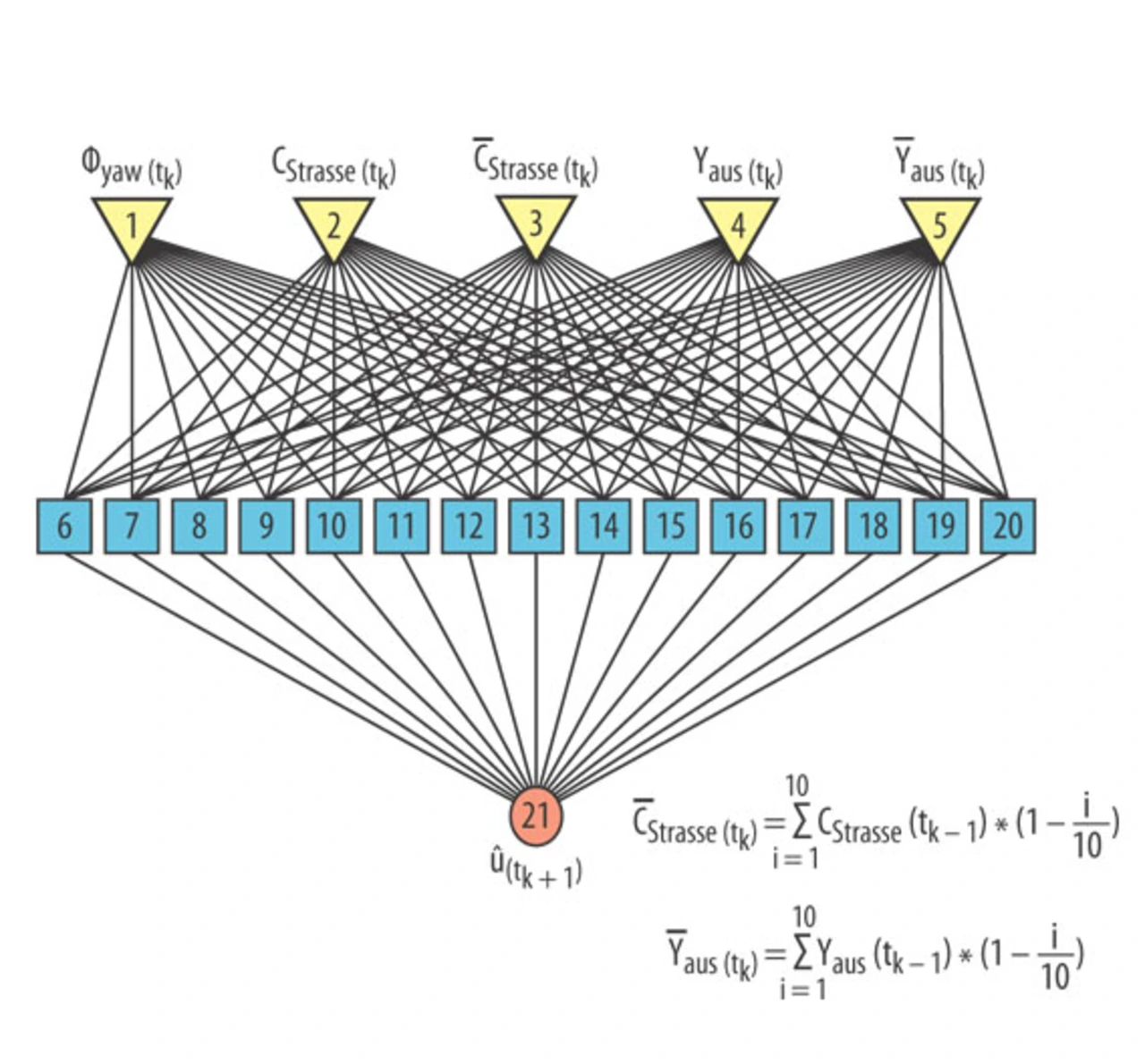

Hier hat eine Renaissance der in der Zeit 1987 bis 2000 recht intensiven Forschungsarbeiten eingesetzt. Ein Beispiel war der Lenkassistent [12] (Bild 9), der, betrieben mit zwei Transputer-Computer-Boards, 1993 ein Mercedes-Automobil selbstständig auf beliebigen Straßen steuerte. Er wäre heute ein System on Chip (SOC), und dieses Funktionspotenzial ist die Basis für Forschungsprojekte wie SYNAPSE [13].

Leistungsstand und Potenzial von Nanochips

Der leistungsfähigste Supercomputer erreichte 1015 Multiplikationen/s mit einer Leistung von 500 kW. Die magischen 1015 haben den Vergleich mit den 1014 Synapsen des menschlichen Gehirns angeregt, die diese Zahl von Operationen/s durchführen, wenn sie alle zehnmal pro s ein Aktionspotenzial auslösen, wobei sie allerdings nur 10 W dazu benötigen. Die Leistungseffizienz ist also die große Aufgabe, um mit den Chips der Zukunft dem Niveau der Natur näherzukommen.

Tabelle 2 zeigt, wieviel Potenzial die Nanochips bis 2020 haben, wenn die in diesem Artikel vorgestellten Innovationen realisiert werden.

| Typ | Anzahl Multiplizierer | Taktfrequenz je Multiplizierer | Leistung |

|---|---|---|---|

| Gehirn |

1014 Synapsen |

10 Hz |

10 W |

| Supercomputer 2011 1) | 5×105 | 2 GHz | 500 kW |

| DARPA UHPC 2018 | 5×105 | 2 GHz | 20 kW |

| INTEL 2012, 1 V 2) | 7×105 | 1,4 GHz | 4,5 kW |

| INTEL 2012, 0,3 V 2) | 4×107 | 25 MHz | 0,8 kW |

| CHIPS 2020 16 × 16 bit 3) | 1,6×106 | 600 MHz | 1 W |

| CHIPS 2020 54 × 54 bit 4) | 1,6×106 | 200 MHz | 4 W |

Tabelle 2. Stand und Potenzial für Nanochips, die 1 Peta-Multiplikationen/s durchführen. 1) 54 × 54 bit, Die Nr.1 der Supercomputer 2011. – 2) ISSCC 2012, Paper 10.3 [3]: 24 bit × 24 bit (6 bit Präzision), 32 nm. – 3) HIPERLOGIC DIGILOG aus [5], Fig. 3.31, 6 bit Präzision, 20 nm, Voraussage. – 4) HIPERLOGIC DIGILOG 10 bit Präzision, 20 nm, Voraussage.

Mit konsequenter Entwicklung der Femtoelektronik werden die 10 W der Natur erreicht und unterboten werden. Wie auch im Gehirn werden selten 1015 Operationen/s benötigt. 109 bis 1011 Operationen/s sind z.B. für Vision-Aufgaben erforderlich. Diese können in Zukunft mit 1 µW bis 100 µW erledigt werden, was autonome, d.h. von Batterien unabhängige Chips ermöglichen wird; denn µW bis einige mW werden mit Energie-Ernten (Energy Harvesting) aus dem Chip oder seinen Betriebsbedingungen gewonnen werden können [14].

Diese Femto-Elektronik wird weitreichende Neuerungen in den nächsten Jahrzehnten ermöglichen, wenn nachhaltig und anforderungsgetrieben geforscht und entwickelt wird [15].

- Chips 2020 – von der Nano- zur Femtoelektronik

- Von Nanometer zu Femtojoule

- Speicher-Chips

- Die dritte Dimension

- Literatur und Autor