Zukunft der Bauelemente

Chips 2020 – von der Nano- zur Femtoelektronik

Fortsetzung des Artikels von Teil 2

Speicher-Chips

Die Dichte digitaler Speicher-Chips ist weiterhin die populäre Messlatte der Nanoelektronik. Aber hier soll besonders nach der Energie für Schreiben und Lesen und auf die Geschwindigkeit geschaut werden. Grundsätzlich muss man mit der Energie CU² rechnen und zur Veranschaulichung soll die Energie neben J = Ws auch in eV (Elektronenvolt) ausgedrückt werden, um zu sehen, wieviele Elektronen jeweils involviert sind: 1 eV = 1,6 × 10-19 Ws = 0,16 aJ.

Der statische CMOS-Speicher SRAM (Static Random-Access Memory) zeigt sich in Bild 6 schon 2010 mit beachtlichen 200 eV und wird 2020 nur 7 eV erreichen können. Der Grund für diese niedrige Schaltenergie ist seine Speicherzelle, das 4T-gekoppelte Inverter-Paar: Spannungsversorgung je Zelle, maximaler Störabstand, Speicherung des Werts und seines Komplements, und die sichere, schnelle differenzielle Auslesung über zwei Zugriffs-Transistoren ermöglichen, dass er in Transistorgröße und Versorgungsspannung agressiv verkleinert werden kann. Ein Optimierungsproblem ist dabei der Ruhe-Reststrom, der z.T. durch eine weiter reduzierte Standby-Spannung abgesenkt werden kann. Der Bedarf von 6 Transistoren pro Bit ist der oft als hoch bewertete Preis.

Wie bereits dargestellt, wird generell im Nanobereich differenzielle Schaltungstechnik und damit als allgemeines verstärkendes Grundelement das 4-Transistor-Inverterpaar gebraucht. Dessen technologisch-elektronische Optimierung ist deshalb ohnehin von großer Bedeutung, vielleicht sogar getrieben von den SRAMs.

Natürlich spricht dies für die dreidimensionale Anordnung der Transistoren. Japanische SRAMs haben schon Ende der 80er Jahre steuerbare Polyisilizium-PMOS-Transistoren über den NMOS-Transistoren gehabt, waren damals aber nicht unabdingbar nötig, weil die laterale, zweidimensinale Verkleinerung rasch voranschritt. Nahe dem Ende der lateralen Verkleinerung wächst nun aber der Nutzen, Transistoren zu stapeln.

Jobangebote+ passend zum Thema

![Querschnitt und Transistordiagramm einer 6-Transistor-SRAM-Zelle mit drei Transistorebenen, hergestellt mit selektiver Epitaxie und lateraler Überwachsung [7]. Querschnitt und Transistordiagramm einer 6-Transistor-SRAM-Zelle mit drei Transistorebenen, hergestellt mit selektiver Epitaxie und lateraler Überwachsung [7].](https://cdn.elektroniknet.de/thumbs/media_uploads/images/1340710802-39-chips-2020-bild-7.jpg.1280x0.webp)

Als konsequenteste Erkundung einer 3D-CMOS-Technologie kann noch immer die Doktorarbeit von Gerhard Roos [7] gelten, aktuell bewertet in [8].

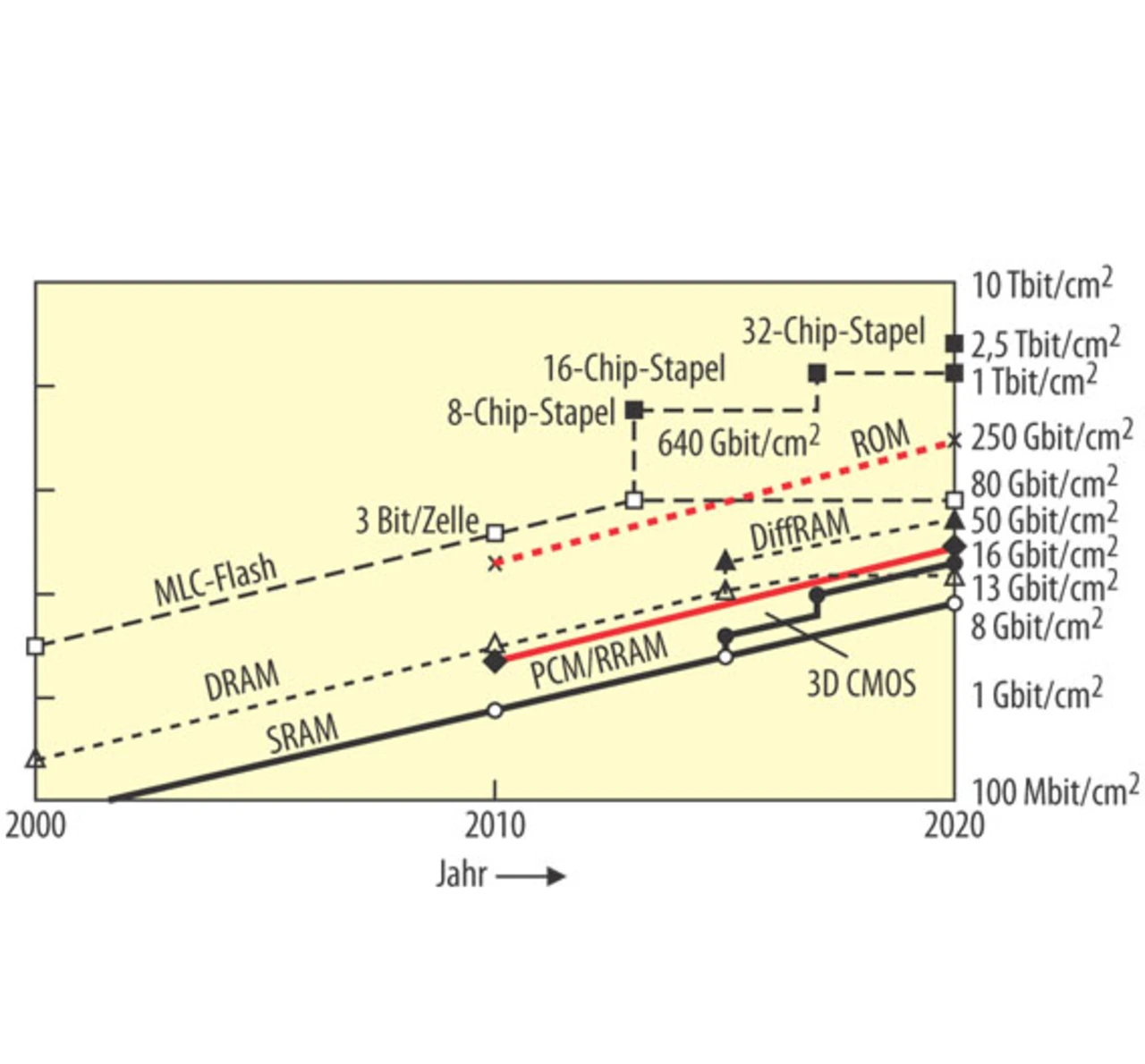

Bild 7 zeigt ein Faksimile der 3D-SRAM-Zelle mit drei Transistorebenen übereinander (wobei der PMOS-Transistor sogar ein Dual-Gate-Transistor ist) mit einer Grundfläche von zwei Transistoren. 3D-SRAM-Speicherzellen werden in dieser Richtung 2020 eine Dichte von 8 Gbit/cm² erreichen können (Bild 8), nicht weit entfernt von DRAMs mit 13 Gbit/cm².

Arbeitsspeicher mit der größten Dichte sind DRAMs (Dynamic Random-Access Memories), deren Speicherzelle aus einem Speicherkondensator von etwa 30 fF und einem Zugriffstransistor besteht. Diese Speicherzelle kann inzwischen nicht mehr wesentlich verkleinert und ihre Betriebsspannung nicht weiter abgesenkt werden, weil die Lesespannung am Ende der Wortleitung nur ein Teil der Spannung am Speicherkondensator ist und diese wiederum infolge der Ladungsverluste über den Transistor abhängig von der Frequenz der Auffrischung nur noch ein Bruchteil der Betriebsspannung ist. So ist die Schreib- und Leseenergie bei 10 fJ angelangt, und die Dichte wird 2020 etwa 13 Gbit/cm² erreichen (Bild 7).

Der Dichtevorteil zum SRAM wird also verschwinden, und auch dessen um Größenordnungen kleinerer Energiebedarf sowie die höhere Geschwindigkeit werden das SRAM attraktiver machen.

Das in [8] vorgeschlagene differenzielle DRAM wird eine Dichte von 50 Gbit/cm² erreichen und in seinem differenziellen Leseverstärker wiederum von dem 4-Transistor-Inverter-Paar profitieren.

Nicht-flüchtige Speicher sind wegen des grenzenlosen Bedarfs der Datenspeicherung und als letztendlicher Ersatz der Plattenspeicher sowie der CDs und DVDs ein Entwicklungsgebiet mit großer Eigendynamik.

Diese Domäne wird beherrscht von NAND-Flash-Speichern. Die Bits werden in diesen auf einer Speicherelektrode gespeichert, die frei zwischen Steuer-Gate und Transistorkanal liegt. Zwei Quantensprünge haben diesen Speichern zu ihrer heutigen Bedeutung verholfen:

- Die Speicherung mehrerer Bits auf jeder Speicherelektrode 1995 mit vier Ladungs-Niveaus = 2 Bit/Transistor.

- Die Stapelung von Flash-Chips mit Durchkontaktierung (TSV = Through-Silicon Vias) großtechnisch seit 2005.

- Was 1995 mit dem Schreiben und Lesen von Elektronenpaketen von 5.000 Elektronen je Niveau begann, ist inzwischen bei 500 Elektronen je Niveau, 2 bis 4 Bit je Transistor und Speicherdichten von 80 Gbit/cm² je Chip in 22-nm-Technologie mit bis zu 3 Bit je Transistor angelangt. Die weitere Verkleinerung der Transistoren wird bei 16 nm enden, weil die Beständigkeit und Varianz der Ladungen keinen Fortschritt bringt. Andererseits wird massiv in das Stapeln der Chips (Stacking) investiert, so dass bis 2020 Stacks mit 32 Chips in Produktion gehen und Speicherdichten von 2,5 Terabit/cm², d.h. mit mehr als 512 GB/Gehäuse erscheinen werden.

- Bei diesen Multi-Level-Flash-Speichern ist die Lesegeschwindigkeit auf weniger als 100 Mbit/s je Transistorreihe beschränkt. Diese Begrenzung und der eingeschränkte Temperaturbereich der Flash-Speicher begründen die massiven Investitionen in alternative, schnelle und zuverlässige nicht-flüchtige, MOS-kompatible Speicher. Dabei handelt es sich um ein großes Gebiet mit vielen spekulativen Entwicklungen. Kriterien sind:

Speicherdichte (4 F² je Zelle, wobei F die minimale Strukturgröße ist)

Geschwindigkeit

Schreib- und Leseenergie/Bit

Beständigkeit

Prozesskompatibilität mit CMOS-Technologie

Temperaturbereich

Mit Blick auf diese Kriterien und die Produktionsreife sind PCM (Phasenwechselspeicher) bei 45 nm und Zellgröße 19 F², RRM (Resistive RAM) bei 130 nm und Zellgröße 10 F² am weitesten fortgeschritten. Auf der ISSCC 2012 wurden schon 8 Gbit große PCM-Chips bei 20 nm vorgestellt. Programmierenergien von 10 pJ/bit bis 100 nJ/bit und Haltezeiten von 15 Monaten bei 85 °C zeigen, dass PCM- und die verwandten RRAM-Speicher auf bestimmte Anwendungen beschränkt sein werden.

Ein Lesespeicher, der alle obigen Kriterien konkurrenzlos erfüllt, ist das MOS-ROM, in dem jede Transistorposition permanent durch Kanaldotierung leitend oder nicht-leitend eingestellt wird. Gewöhnlich wird dies mit der spezifischen Programmierung der Gate-Maske eingestellt. Diese spezifische Maske für jeden Chip ist teuer, und deshalb ist dieses Vorgehen teuer. Beim maskenlosen Direktschreiben auf dem Chip entfallen die prohibitiven Maskenkosten. Aber das normale Elektronenstrahlschreiben ist langsam, und deshalb ist auch dieses Vorgehen selten. In der Nanolithographie haben zwei Techniken höchste Priorität [9]: Extreme-Ultraviolet-Lithografie (EUV) mit Masken bei 13-nm-Strahlung und Massive-Parallel-Electron-Beam-Maskless-Direct-Write-Lithografie (MEB).

Die MEB-Lithografie wird je Produktionseinheit mit 130.000 parallelen Elektronenstrahlen und 100 Tera-Blitzen je Sekunde einhundert 300-mm-Siliziumscheiben je Stunde belichten. Diese Anlage kann mit einem Blitz/Transistor vorgeben, dass dessen Kanal leitend oder nicht-leitend dotiert wird. So kann 1 Tbit permanentes, individuelles ROM je Chip in 10 ms geschrieben werden, um Größenordnungen schneller als 1-bit-Flash-Speicher.

Daten und Programmspeicher für höchste Sicherheit, Zuverlässigkeit und Permanenz können so individuell je Chip produziert werden. Es wäre der ultimative Speicher für Dokumente und Medienträger wie Filme und Spiele und dies mit

- agressiver Skalierbarkeit,

- höchster Dichte: 4 F² entsprechend 250 Gbit/cm² je Chip-Ebene,

- höchster Lesegeschwindigkeit: Gbit/s,

- niedrigster Leseenergie: 6 eV/bit = 1 aJ/bit.

- Chips 2020 – von der Nano- zur Femtoelektronik

- Von Nanometer zu Femtojoule

- Speicher-Chips

- Die dritte Dimension

- Literatur und Autor