Audio-Clocks bei I²S-Lösungen

Warum den Systemtakt integrieren?

Fortsetzung des Artikels von Teil 1

Verwendungsmöglichkeiten für I²S

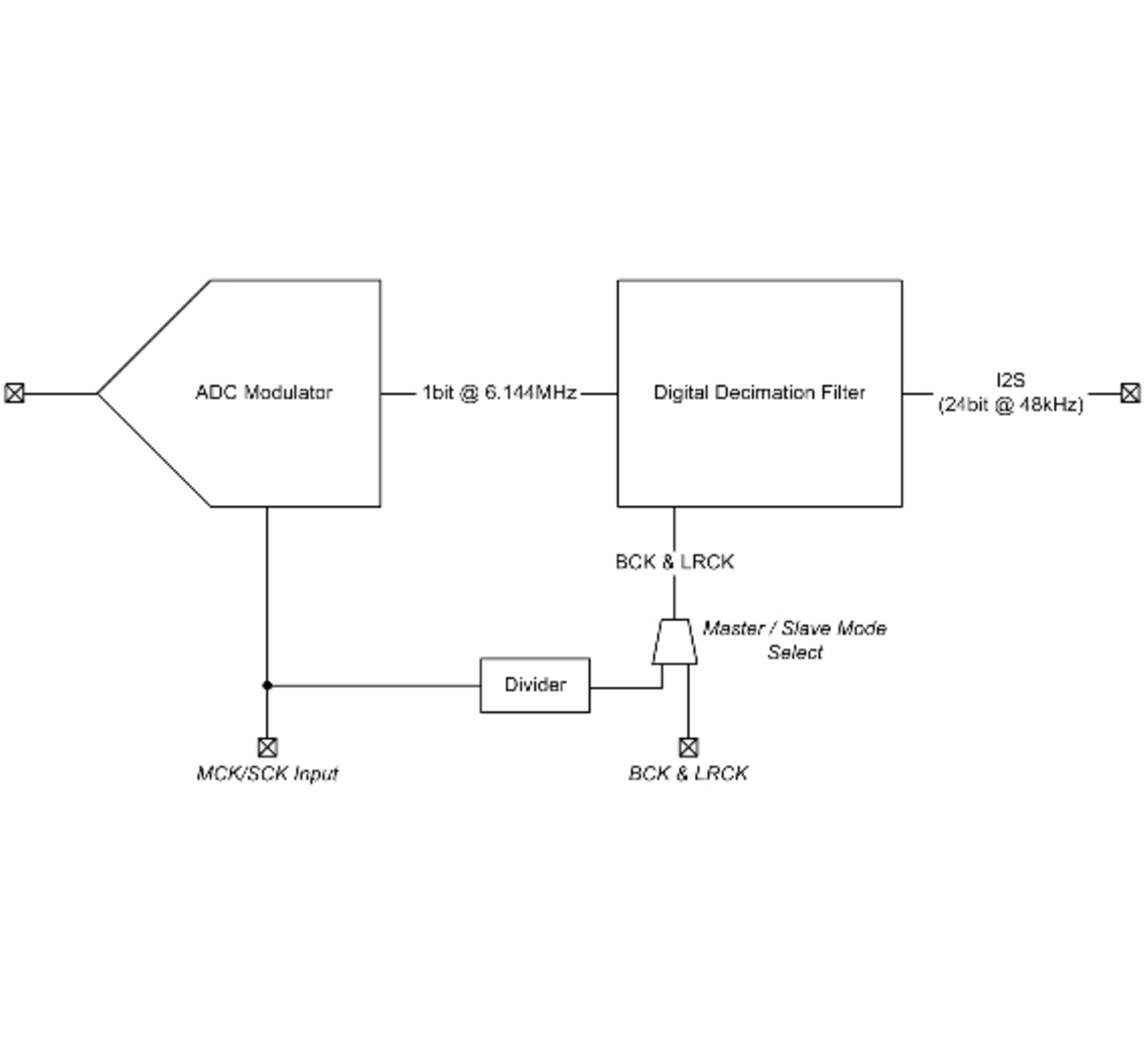

Wie in Bild 1 dargestellt, nutzt ein ADC als Treiber des Oversampling-Modulators einen Hochgeschwindigkeits-Haupttakt (z. B. mit 24,576 MHz). Anschließend teilt der Oversampling-Modulator die Daten vom Oversampling-Modulator auf die vom LRCK vorgegebene Abtastrate herunter oder dezimiert sie.

Jobangebote+ passend zum Thema

Arbeitet ein ADC im Master-Modus (zur Generierung des BCK und LRCK als Ausgängen), dient der Datenwandler lediglich der MCK/SCK-Teilung, um die LRCK- und BCK-Signale zu generieren. Voilà! LRCK/BCK und Haupttaktgeber sind synchronisiert – und höchstwahrscheinlich sogar phasengleich – sofern es sich nicht um einen ungewöhnlichen Treiber handelt.

Kommt ein ADC als Slave mit einem nicht synchronisierten Haupttakt zum Einsatz, erzeugt er entweder zu viele oder zu wenige Daten, sodass der digitale Dezimierer nicht ordnungsgemäß in die Ausgabewörter passt. Bei vielen ADCs ist unter solchen Bedingungen kein Datenstreaming möglich.

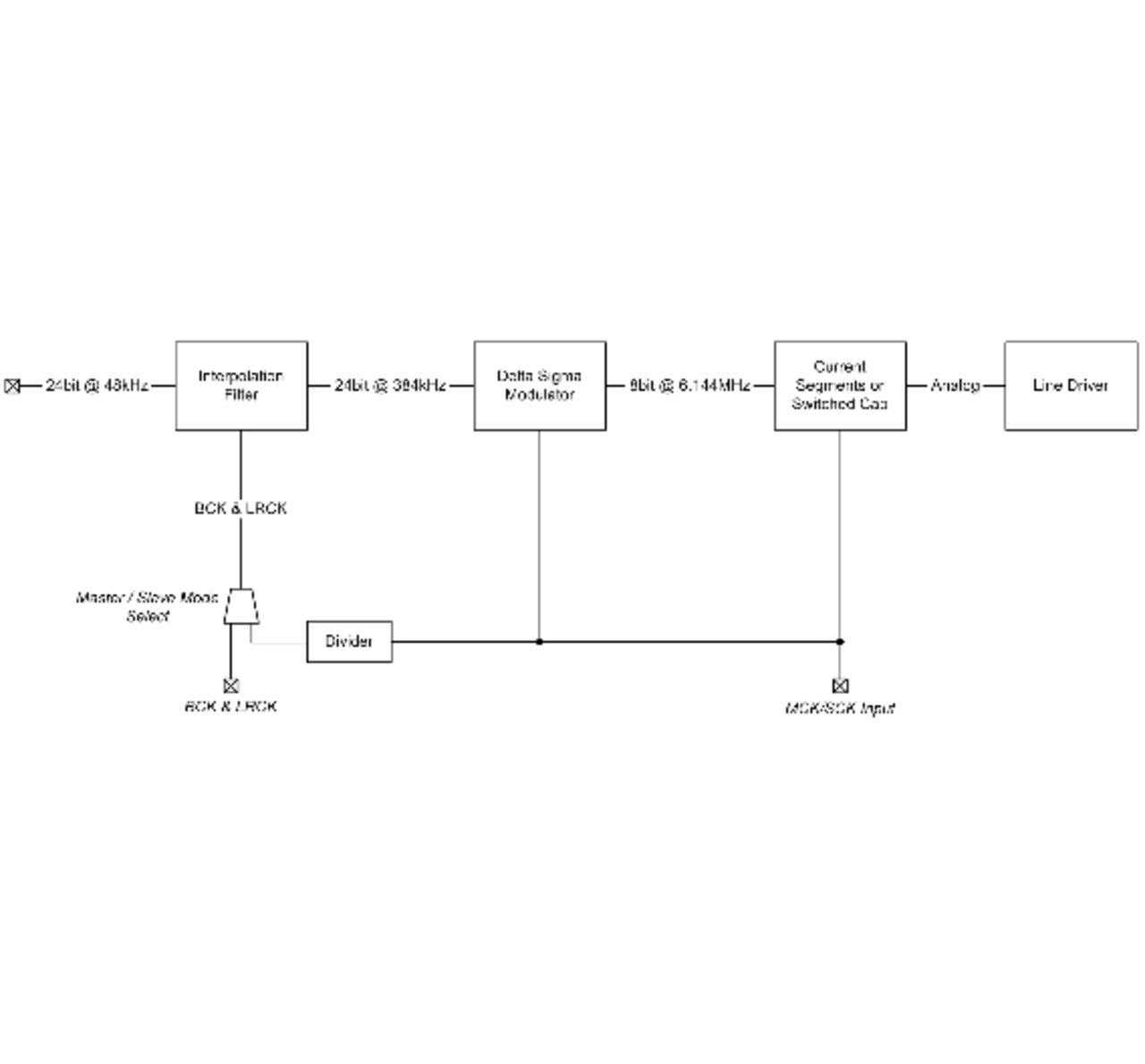

Dasselbe gilt für DACs. Bild 2 zeigt ein detailliertes DAC-Diagramm. Hier muss der Interpolierter über den MCK/SCK ausgeführt werden, der zudem als Treiber für den Delta-Sigma-Modulator dient. Ist der MCK/SCK kein ganzzahliges Vielfaches der Abtastrate (64/128/256/512), sind die Daten am Ausgang des Delta-Sigma-Modulators fehlerhaft.

Wo und wie den MCK/SCK generieren?

Die Industrie bevorzugt häufig CMOS-Oszillatoren, dicht gefolgt von Quarzoszillatoren. Beide Technologien bieten eine sehr gute Genauigkeit und einen geringen Jitter. Gelegentlich kommen auch spannungsgesteuerte Oszillatoren (VCOs) zum Einsatz, ihre Ausgabe kann jedoch unter den Auswirkungen von Jitter leiden.

In zahlreiche moderne Audiowandler wird nun ein PLL integriert, um den MCK aus einem langsameren BCK zu generieren. Dieser Lösungsansatz ist recht hilfreich. Sie sollten jedoch beachten, dass bei Verwendung eines PLL immer ein gewisses Jitter-Risiko besteht, was die Audioleistung verschlechtern kann.

Ferner rate ich dazu, den ADC über eine quarzgenerierte Quelle zu treiben, sofern Sie zwischen einer Quarzquelle als Treiber für den ADC oder einen DAC wählen können. Nach einer schlechten Erfassung des Eingangssignals haben Sie keine Möglichkeit mehr, einen guten Ton zu erzeugen! (Aus einer Krähe wird kein Singvogel!)

Daher empfehle ich die Einhaltung der folgenden Regeln:

- Wenn es sich bei dem Wandler um einen I²S-Slave handelt, sind alle I²S-Takte (MCK, BCK und LRCK) über dieselbe Quelle bereitzustellen. Alternativ können Sie auf eine interne PLL zurückgreifen, sofern der Wandler eine solche beinhaltet.

- Ist der Wandler ein I²S-Master, stellen Sie unbedingt eine zuverlässige, jitterfreie MCK-Quelle bereit. Lassen Sie dann eine Taktaufteilung durch den Wandler zu. Führen Sie den ADC möglichst über eine vertrauenswürdige MCK-Quelle mit geringem Jitter und im Master-Modus aus. Dadurch bleiben die Effekte durch Jitter möglichst klein, Verzerrungen im Hochfrequenzbereich werden minimiert.

- Warum den Systemtakt integrieren?

- Verwendungsmöglichkeiten für I²S