e2v technologies

Ultraschnelle A/D-Wandler für die Wissenschaft

Fortsetzung des Artikels von Teil 4

Erweiterung des Dynamikbereichs der A/D-Wandler

Der dynamische Bereich des A/D-Wandlers wurde von RFEL durch Verwendung einer gestapelten ADC-Architektur erweitert [4]. Dieser Ansatz bietet einen deutlich größeren dynamischen Bereich, indem parallele Datenerfassungspfade mit versetzten Abschwächungseinstellungen zum Einsatz kommen. Die Abstimmung der Frequenz-, Phasen- und Amplitudenkenndaten in diesen parallelen Pfaden ist für eine erfolgreiche Umsetzung von grundlegender Bedeutung. Daher lag das besondere Augenmerk auf der Architektur des analogen Designs, um potenzielle Nichtübereinstimmungen der Bauteilkenndaten zu vermeiden.

Jobangebote+ passend zum Thema

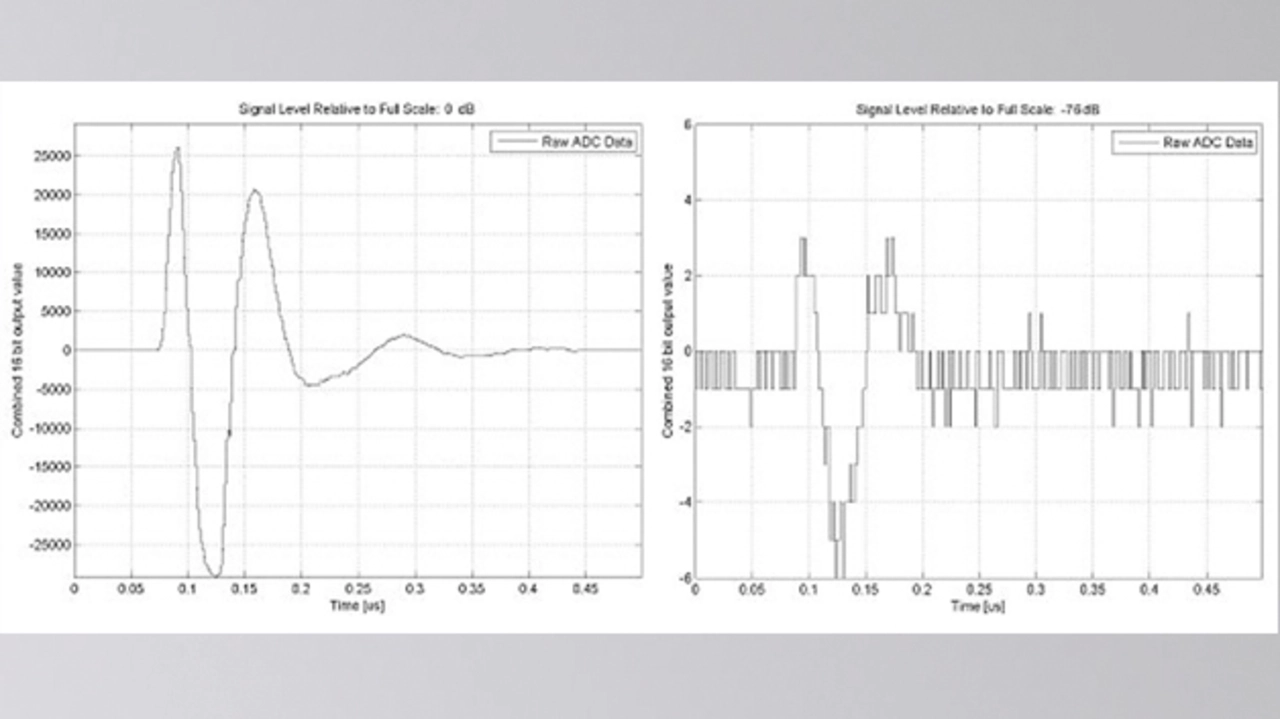

Nachdem das empfangene Signal in die digitale Domäne umgewandelt wurde, beträgt die Eingangsdatenrate für jeden Kanal 29 GBit/s. Die Vorverarbeitung des Signals reduziert die Datenrate, während in der Zeitdomäne die volle Genauigkeit vollständig erhalten bleibt (Bild 8). Anschließend werden weitere Messungen in der Zeit- und Frequenzdomäne durchgeführt, bevor der Prozessor die Ergebnisse erhält. Die Software nimmt die abschließenden Anpassungen der Daten vor und verwaltet die Benutzerschnittstelle.

Das analoge und digitale Mehrkanaldesign verwendet sechs Quad-Speed-ADCs vom Typ »EV8AQ160«, zwei 1,6-GHz-PLLs, vier Hochgeschwindigkeits-FPGAs und einen Prozessor. Das abschließende System erreicht eine Abtastrate von 800 MSample/s.

- Ultraschnelle A/D-Wandler für die Wissenschaft

- Schnelle A/D-Wandler in der Teilchenphysik

- Schnelle A/D-Wandler in der Massenspektrometrie und der Radioastronomie

- Einsatz bei LiDAR, Ultraschall und optischer Mammografie

- Erweiterung des Dynamikbereichs der A/D-Wandler