Heterogene SoCs homogen entwickeln

RTOS und Hypervisor für Prozessoren mit MMU und MPU

Fortsetzung des Artikels von Teil 1

Zwei Welten – in einem SoC

In der bisherigen RTOS und Echtzeit-Hypervisor-Landschaft gab es für das Management solcher heterogenen SoCs mit MMU- und MPU-basierten Prozessoren bislang keine wirklich homogenen Lösungen. Die meisten OS-Anbieter haben für Prozessoren mit MPU kleinere RTOS entwickelt, die komplett andere APIs als die RTOS für Prozessoren mit MMU haben. Dies spielte bislang auch keine große Rolle, da diese Prozessoren meist diskret implementiert wurden. Infolge wurden RTOS für die MPU-basierten Prozessoren vor allem auch auf einen minimalen Arbeitsspeichergebrauch getrimmt, was ein Grund für diese Inkompatibilitäten ist.

Wie wichtig das war, zeigt sich auch an der Tatsache, dass diese diskreten Prozessoren mit MPU oft sogar »Bare Metal« programmiert wurden, wenn kein Multithreading erforderlich war, um wenig Ressourcen zu beanspruchen, mit den damit einhergehenden Vorteilen wie Einsparung von Lizenzen, geringeren Kosten für Bauteile und einfacherer Zertifizierbarkeit. Mit homogenen OS für die Entwicklung von MMU- und MPU-basierten SoCs und ganzheitlich integrierten Entwicklungsumgebungen lässt sich jedoch die Programmierung von heterogenen SoCs deutlich komfortabler gestalten.

Jobangebote+ passend zum Thema

Heterogene OS-Installationen überwinden

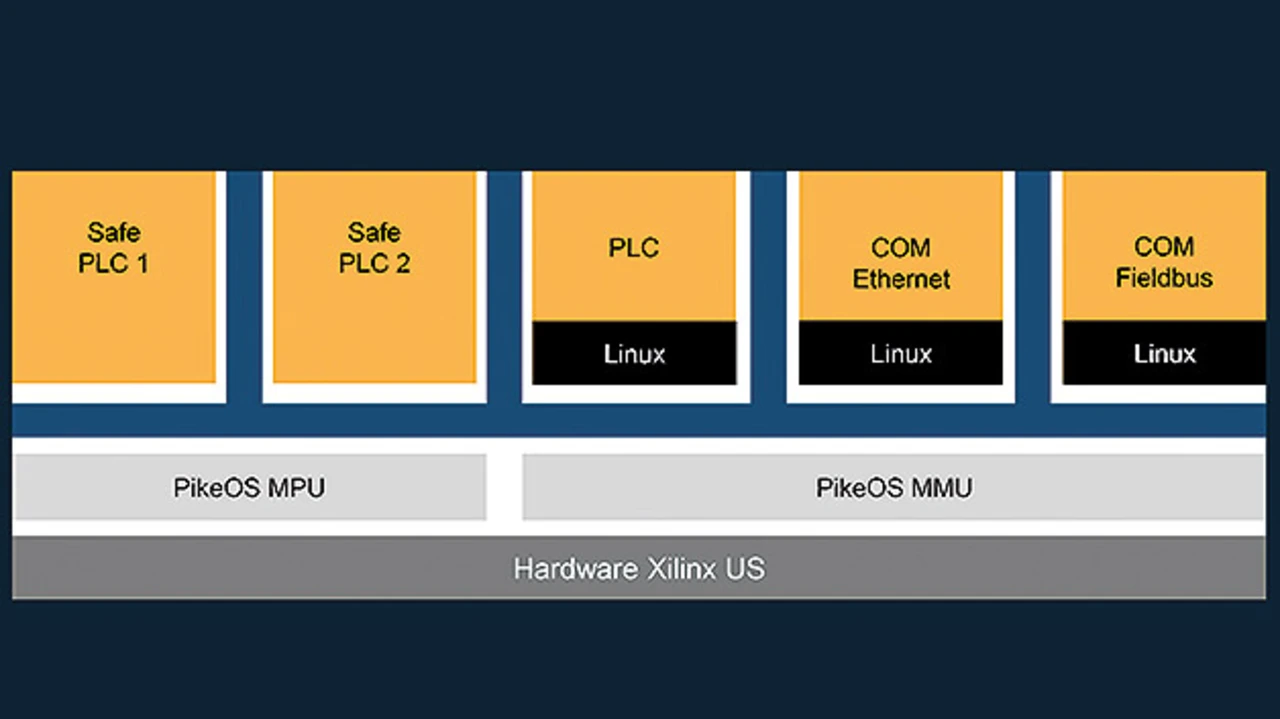

Mit der Vorstellung von PikeOS, Betriebssystem und Hypervisor für MPU (Bild 6), im September 2021 hat Sysgo erstmals eine Grundlage geschaffen, um heterogenen SoCs ein homogenes System mit RTOS und Echtzeit-Hypervisor zu bieten, was das Programmieren und das Ausbalancieren der Rechenlast deutlich vereinfacht. PikeOS for MPU wurde hierzu codeseitig auf Basis des klassischen PikeOS-Betriebssystems für MMU-basierte Prozessoren entwickelt. Die APIs zur Programmierung von Applikationen für Prozessoren mit MMU oder MPU sind deshalb quasi identisch. Im Wesentlichen wurde schließlich nur das Memory-Management-API entsprechend angepasst.

Der Wechsel einer Applikation von einem MMU- zu einem MPU-basierten Prozessorkern ist jedoch trotz unterschiedlicher Speicherhandhabung mit wenigen Klicks binnen weniger Minuten zu handhaben. Noch wichtiger ist zudem der Vorteil, dass Code für beide Prozessorkernvarianten – MMU und MPU – in ähnlicher Weise zertifizierbar ist. Die Zertifizierung von PikeOS-for-MPU-basierter Anwendungen kann also auf den SIL-4-, DAL-A- und ASIL-D-Zertifizierungen des PikeOS for MMU aufbauen.

Homogenes OS für MMU und MPU

Dadurch, dass rund 80 % des Quellcodes beider OS-Varianten identisch ist, konnten auch wichtige Kernfunktionen des klassischen PikeOS wie der Separation-Kernel oder die Time- und Space-Partitionierungsmechanismen funktionsidentisch beibehalten werden. Durch die strikte Trennung von Partitionen ermöglicht der Separation-Kernel den parallelen Betrieb mehrerer Anwendungen – von einfachen, aber hochkritischen Steuerungsaufgaben bis hin zu komplexen Benutzerprogrammen mit vielen Funktionen.

Außerdem eliminiert der Separation-Kernel das Risiko, dass sich Anwendungsfehler auf andere Partitionen und Anwendungen auswirken. Die Verwendung der gleichen Time- und Space-Partitionierungsmechanismen bringt PikeOS für MPU auch sehr nahe an die ARINC-653-Spezifikation, für die PikeOS für MMUs ursprünglich entwickelt wurde. Damit eignet sich PikeOS für MPU selbst für kritische Anwendungen in der Raumfahrt und Avionik.

Eine besonders interessante Eigenschaft für die effiziente Entwicklung auf der Basis heterogener Systeme ist die ICCOM-Funktion (Inter-Core Communication) der beiden PikeOS-Derivate: Diese Funktion erlaubt es PikeOS-Instanzen, die auf verschiedenen Cortex-A- und -R-Prozessorkernen laufen, über nachrichtenbasierte Kommunikationskanäle miteinander zu kommunizieren. Dies unabhängig davon, ob auf den Kernen unterschiedliche oder gleiche Betriebssysteme laufen. ICCOM basiert auf einer symmetrischen Vollduplex-Datentransportschicht, die die Zustellung von Nachrichten garantiert.

Eine IDE für alle Prozessorkerne

Ab Version 7.2 der Eclipse-basierten IDE CODEO können beide PikeOS-Varianten in einer integrierten Entwicklungsumgebung genutzt werden. Sie kann innerhalb eines einzigen Arbeitsbereiches den gesamten Software-Stack eines heterogenen SoCs und seiner Inter-Core Communication verwalten, was den Softwareentwicklungsprozess für solche komplexen Zielsysteme deutlich vereinfacht (Bild 7).

Unterstützt wird der gesamte Entwicklungszyklus von der frühen QEMU-basierten (QEMU, Quick Emulator) Systememulation und Applikationssimulation bis hin zu Remote-Debugging und Mechanismen zur Softwareaktualisierung für Systeme im laufenden Betrieb.

Auch die Debug-Umgebung TRACE32 von Lauterbach unterstützt das kombinierte Debuggen von MMU- und MPU-basierten Zielsystemen. Das bedeutet auch, dass ein TRACE32-Hardwareaufbau ausreicht, um die gesamte Palette von Zynq Ultrascale+ MPSoCs mit heterogenem OS zu debuggen (Bild 8)

Allerdings sollten Entwickler beim Tandemeinsatz beider PikeOS nicht mehr von einem heterogenen OS sprechen. Es handelt sich vielmehr um ein homogenes OS für heterogene SoCs, das zudem noch in beiden Varianten auch einen Type-1-Echtzeit-Hypervisor integriert hat, sodass multiple zeit- und speicherisolierte, funktional sichere Applikationen dieser oder auch weiterer OS in entsprechend gekapselten Virtuellen Maschinen ausgeführt werden können.

Durch den Start eines individuellen GUI für solche OS-Partitionen können Softwareentwickler auch beide PikeOS-Varianten gleichzeitig debuggen – inklusive synchronisierter Start-and-Stop-Events. Dies ist besonders bei der Suche nach Fehlern in der Kommunikation zwischen den einzelnen Subsystemen nützlich. Darüber hinaus kann TRACE32 das gesamte System tracen und grafische Diagramme der Anwendungs- und Funktionslaufzeiten anzeigen. Das Timing ist synchronisiert, was die Beobachtung des Timing-Verhaltens von sowohl klassischem PikeOS als auch PikeOS for MPU und die Messung von Latenzen zwischen beiden Systemen ermöglicht und so das Ausbalancieren der Leistung erleichtert.

Prozessor-Roadmap

Die Applikationsentwicklung für heterogene SoCs wird durch das neue PikeOS mit RTOS- und Hypervisor-Varianten für MMU- und MPU-basierte Prozessoren auf einem Chip deutlich homogener. Anwendungen sind dabei nicht auf den Zynq Ultrascale+ MPSoC beschränkt. Die Unterstützung ist vielmehr auf Cortex-A53- und -R5-Prozessoren ausgelegt und damit portierbar. Mittelfristig ist zudem geplant, alle weiteren Varianten der Cortex-A-, -R- und -M-Prozessoren von ARM zu unterstützen und die Unterstützung auch auf RISC-V-, MPC57xx- und TriCore-Aurix-Prozessoren auszuweiten – schlussendlich also auf alle MPU-basierten diskreten Prozessoren und auf heterogene MMU/MPU-SoCs. Halbleiterhersteller können die PikeOS-Unterstützung auch für ihre proprietären Prozessoren und SoCs erhalten.

Funktionale Sicherheit im Fokus

Zertifizierungskits für PikeOS für MMU gibt es beispielsweise für Avionik (DO-178C), Automotive (ISO 26262), Schienenverkehr (EN 50128/EN 50657), industrielle Automatisierung (IEC 61508) und Medizintechnik (ICE 62304). Zusätzliche Anwendungsbereiche finden sich bis hin zum hohen Evaluation Assurance Level (EAL) 3+ beziehungsweise bis zum Level SAL 4 nach dem Avionics Airbus Security Certification Standard SAR, was im Zusammenhang zunehmender Bedrohungen von Cyberattacken immer mehr an Bedeutung gewinnt. Darüber hinaus ist PikeOS der einzige Separation Kernel (4.2.4) weltweit, der ein aktuelles und gültiges Common-Criteria-Zertifikat (EAL3+) hat. PikeOS eignet sich damit auch als Basis für alle über TSN-synchronisierte OPC/UA-Protokolle, die via 5G autonome Fahrzeuge und kollaborative Robotik von einem Cloud-native Edge-Server aus steuern.

Funktionserprobt in herausforderndem Umfeld

Das RTOS PikeOS for MPU wird bereits in Raumfahrtanwendungen eingesetzt. Die hier zum Einsatz kommende Schaltung beruht auf einem proprietären, diskreten, Cortex-R5-basierten IC, der strahlungsgehärtet ist, um strahlungsbedingte Single Event Upsets (SEU) abschwächen zu können. Der Schutz vor SEUs ist auch für das autonome Fahren und kollaborative Robotik auf der Erde durchaus interessant. SEUs tauchen hier zwar deutlich seltener auf. Aber es wird zukünftig viel mehr solcher Systeme geben, weshalb SEU-gehärtete Prozessoren an Bedeutung gewinnen.

Der Autor

Dr. Oliver Kühlert

ist seit 2019 wieder bei Sysgo als Technical Product Marketing Manager tätig. Er hat einen starken Hintergrund in der Softwareentwicklung und war verantwortlich für die erste Version der PikeOS-Systemsoftware. Bevor er zu Sysgo zurückkehrte, war er Leiter der Gerätesoftwareentwicklung bei AESKU.Systems in Wendelsheim. Dr. Kühlert studierte an der Philipps-Universität in Marburg und am MPI-K in Heidelberg und promovierte in Physik.

oliver.kuehlert@sysgo.com

- RTOS und Hypervisor für Prozessoren mit MMU und MPU

- Zwei Welten – in einem SoC