Design for Testability

Keine Kompromisse, dank Paket-basierten Testdaten

Fortsetzung des Artikels von Teil 1

Scan-Testdaten paketweise übertragen

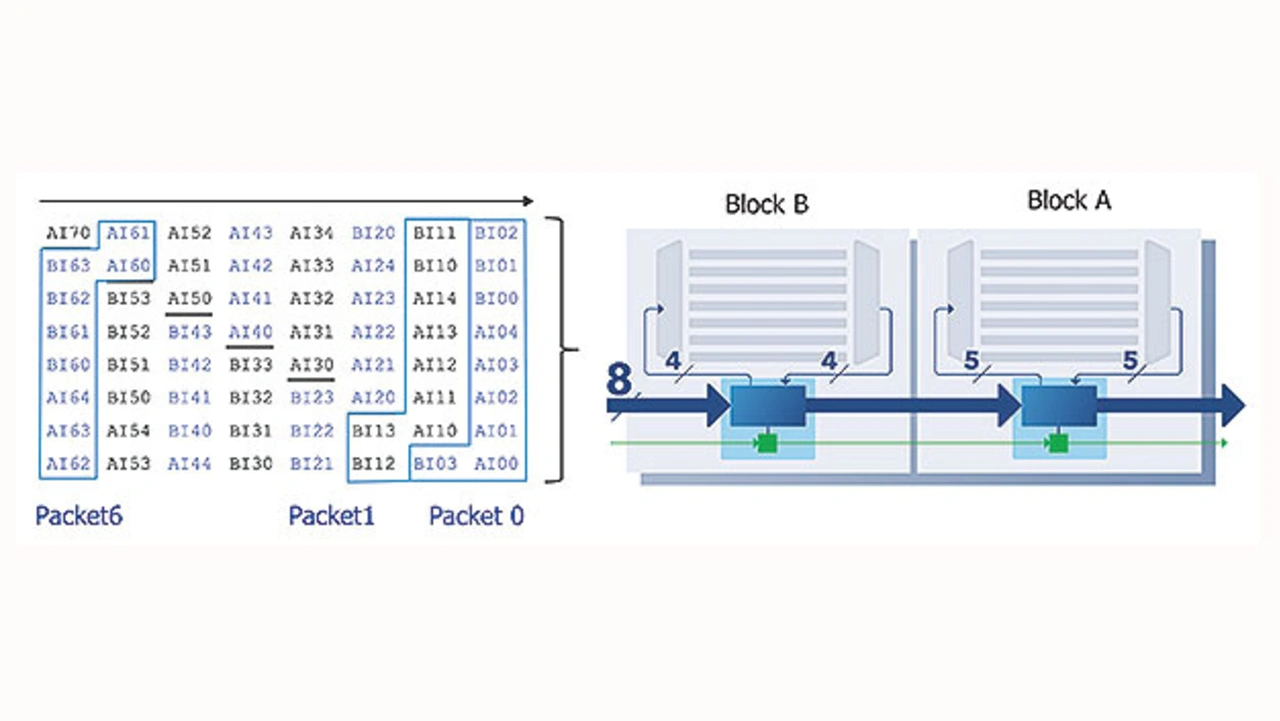

Um die Funktionsweise der paketweisen Testdatenübertragung zu verdeutlichen dient ein SoC als Beispiel, bei dem zwei Blöcke gleichzeitig mit SSN getestet werden sollen (Bild 3).

Jobangebote+ passend zum Thema

Block A hat fünf Scan-Kanäle, Block B hat vier Scan-Kanäle. Ein Paket ist die Gesamtmenge an Daten, die benötigt werden, um einen Scan-Shift-Zyklus über beide Blöcke hinweg durchzuführen. Die Paketgröße in diesem Beispiel beträgt 9 bit. Für den Scan-Test stehen jedoch 16 Pins zur Verfügung – acht Eingänge, acht Ausgänge. Der SSN-Bus ist folglich 8 bit breit.

Die Tabelle auf der linken Seite von Bild 3 zeigt, wie die Daten durch den synchronen SSN-Bus zu den Blöcken übertragen werden. Es dauert zwei SSN-Buszyklen, um alle Daten zu übertragen, die für die Durchführung eines Scan-Shift-Zyklus in beiden Blöcken erforderlich sind. Zu beachten ist, dass sich die Bitposition der Daten, die einem Block entsprechen, für jedes Paket ändert. Die Host-Knoten wissen, wo sich die zu diesem Block gehörenden Daten im Bus befinden und wann lokale Testsignale erzeugt werden müssen, einschließlich der Erzeugung des Taktpulses für den Scan-Shift-Zyklus.

Kürzere Testzeit und weniger Testdatenvolumen

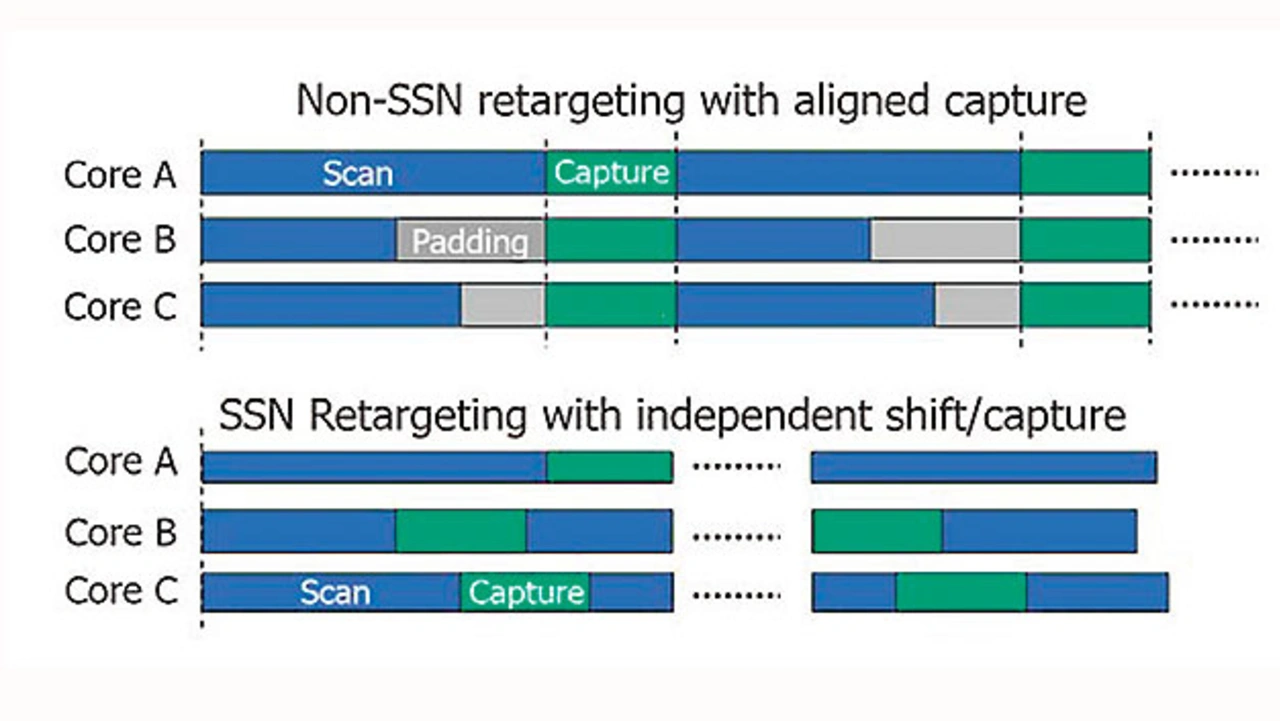

Um die Testzeit und das Testdatenvolumen zu reduzieren, bietet SSN den SoC-Entwicklern mehrere Möglichkeiten. Eine davon ist die unabhängige Übergang von Shift nach Capture. In vielen Retargeting-Ansätzen müssen die Capture-Zyklen aller betroffenen Blöcke aufeinander abgestimmt werden. Wenn mehrere Blöcke mit unterschiedlicher Scan-Kettenlänge gleichzeitig getestet werden (Bild 4), müssen einige Blöcke mit kürzeren Ketten aufgefüllt werden, um das Capture für alle Blöcke gleichzeitig durchzuführen.

Mit SSN werden die Host-Knoten so programmiert, dass alle Blöcke unabhängig voneinander schieben können und selbstständig in den Capture-Modus schalten, sobald sie das Laden/Entladen der Scan-Ketten abgeschlossen haben.

Mit SSN lässt sich die maximale Datenübertragungsrate optimal ausnutzen. Anstatt so viele Bits zur Verfügung zu stellen, wie Scan-Kanäle auf Blockebene pro Paket vorhanden sind, kann SSN einem Block, der insgesamt weniger Daten benötigt, auch weniger Bits zuweisen. Einem Block mit weniger Testmustern oder kürzeren Scan-Ketten werden weniger Daten pro Paket zugewiesen, was die Daten besser auf die Blöcke verteilt und letztendlich die Testzeit verkürzt.

SSN ist eine skalierbare Methode zum Testen beliebig vieler identischer Blöcke mit einer konstanten Menge an Testdaten und Testzeit. Bei identischen Blöcken ist ein Komparator in jedem Host-Knoten enthalten. Daten, die an identische Blöcke geliefert werden, sind Scan-Eingang, Expected-Ausgang und Maskierungsdaten. Dies ermöglicht SSN den Vergleich innerhalb jedes Blocks durchzuführen. Der akkumulierte Status über alle identischen Blöcke wird dann auf den SSN-Bus ausgegeben. Zusätzlich wird im Host ein Pass-/Fail-Bit pro Block erfasst und durch IJTAG ausgelesen.

Das Konzept des Streaming Scan Network (SSN) wurde in Zusammenarbeit mit mehreren führenden Halbleiterunternehmen entwickelt. Auf der International Test Conference (ITC) 2020 hat Siemens EDA gemeinsam mit Intel die Technik in einem Vortrag erläutert und wichtige Ergebnisse der Validierung von SSN durch Intel gezeigt [1]. Im Vergleich zum Pin-Mux-Ansatz konnten mit SSN das Testdatenvolumen um 43 % und die Testzyklen um 43 % reduziert werden. Die Schritte im Design- und Retargeting-Entwurfsprozess waren mit SSN um einen Faktor zwischen zehn bis 20 schneller.

Literatur

[1] Côté, J.-F.; et al.: Streaming Scan

Network (SSN): An Efficient Packetized Data Network for Testing of Complex SoCs. IEEE International Test Conference (ITC), Konferenzband, 3.–5. November 2020, DOI: 10.1109/ITC44778.2020.9325233.

Der Autor

Geir Eide

ist Direktor des Produktmanagements für die Tessent Design-for-Test-

Produkte bei Siemens Digital Industries Software. Als Veteran der IC-DFT- und Testindustrie mit 20 Jahren Erfahrung hat Geir Eide mit führenden Halbleiterunternehmen zusammengearbeitet und weltweit technische Präsentationen und Seminare über DFT, Test und Ausbeute gehalten. Geir erwarb seinen Master-Abschluss in Elektro- und Computertechnik an der University of California in Santa Barbara und seinen Bachelor in Mikroelektronik an der University of South-Eastern Norway.

Geir_Eide@mentor.com

- Keine Kompromisse, dank Paket-basierten Testdaten

- Scan-Testdaten paketweise übertragen