Erweiterte Funktionen in NOR-Flash

Daten in Speicher-Chips besser schützen

Fortsetzung des Artikels von Teil 1

Funktion des Merkmals TB-Bit

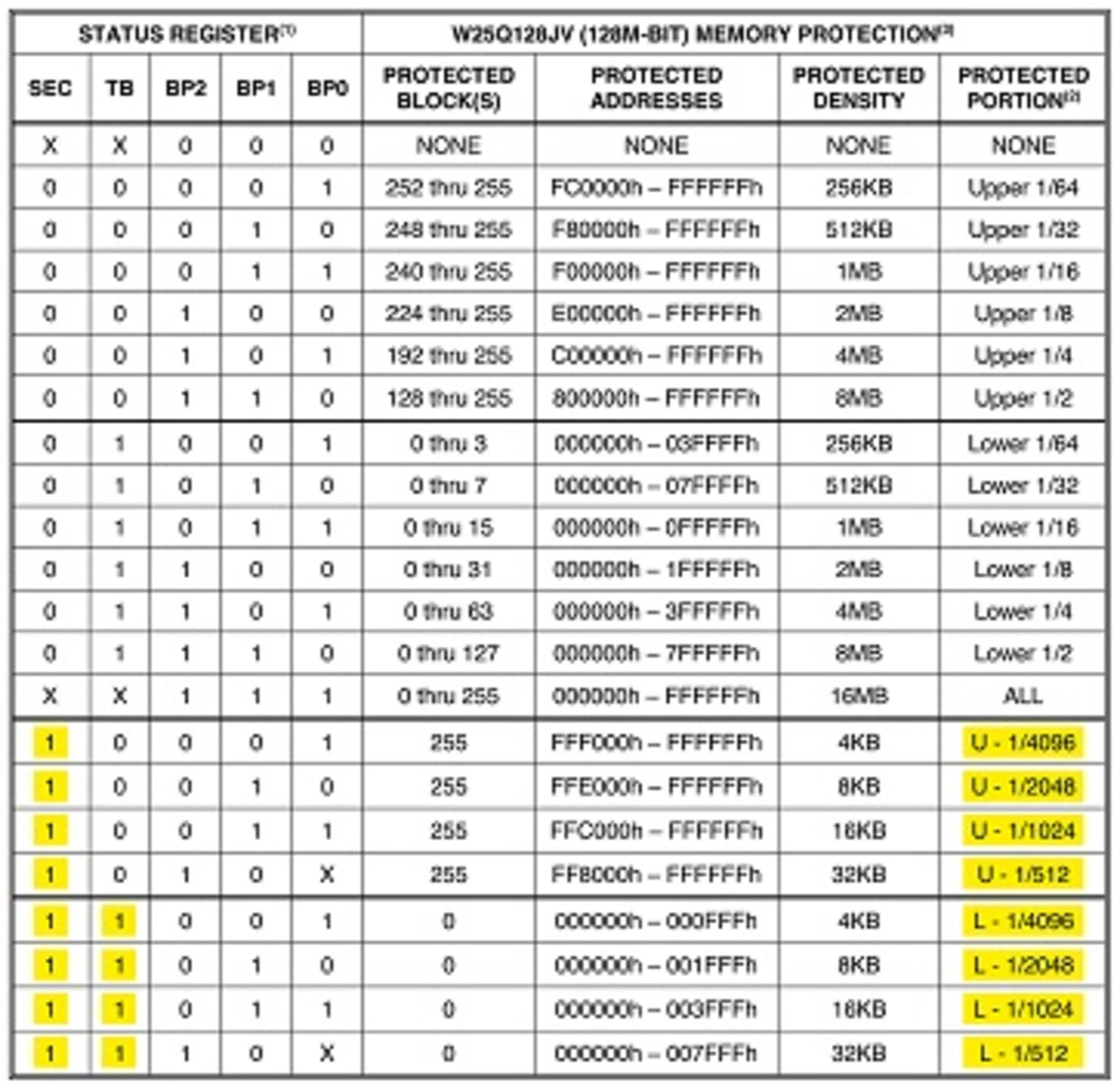

In Tabelle 2 ist ein weiteres von Winbond eingeführtes Merkmal zu sehen (gelb markiert): das TB-Registerbit (Top/Bottom). Standardmäßig (TB=0) beginnt die Zuweisung von Block- oder Sektorschutz am unteren Ende des Speicher-Arrays von Adressen. Dies liegt daran, dass die meisten CPUs vom unteren Ende des Arrays booten. Daher sollte der geschützte Bereich, der den Bootcode enthält, unten liegen, um die schnellste Ausführung und die effizienteste Nutzung des Hauptspeichers zu gewährleisten. Intel-CPUs booten jedoch von oben. Mit dem TB-Bit gibt das Unternehmen Nutzern von Intel-Chips die Möglichkeit, Speicheradressen am oberen Ende des Arrays für den Block- oder Sektorschutz zu vergeben, indem TB=1 im Statusregister konfiguriert wird.

Jobangebote+ passend zum Thema

Blockschutz auf fast komplettes Array anwenden

In Standard-NOR-Flash-Speicher-ICs beginnt die Option, Blöcke für den Schreib-/Löschschutz zu konfigurieren, mit der kleinsten Abstufung (1/64) und ermöglicht einen Schutz bis zur Hälfte des Arrays, wie in Tabelle 2 dargestellt ist. In einigen Anwendungen ist die Anforderung zum Speichern von Benutzerdaten jedoch null oder fast null, sodass fast das gesamte Speicher-Array mit Boot- und Anwendungscode belegt ist. Ein Beispiel für eine solche Anwendung ist eine TV-Fernbedienung: Hier ist nur wenig ungeschützter Speicherplatz für seltene Konfigurationseinstellungen seitens des Endbenutzers nötig (etwa um die Fernbedienung mit einem neuen Mediengerät zu koppeln). Fast der gesamte Speicherplatz wird durch Anwendungscode belegt, der sich nicht ändert und somit vom Schreib-/Löschschutz profitiert.

Ein von Winbond bereitgestelltes Statusregister-Bit erfüllt diese Anwendungsanforderung. Es ist das Complement-Bit (CMP): Damit wird die Schutzeinstellung der BP- und SEC-Bits umgekehrt. Wenn die BP-Bits so konfiguriert sind, dass sie 1/64 des Speicherarrays mit der Standardeinstellung CMP=0 schützen, kann man CMP=1 für den Schutz von 63/64 des Arrays nutzen, sodass nur 1/64 ungeschützt bleibt.

Verstärkter Schutz durch Hardware-Sperre

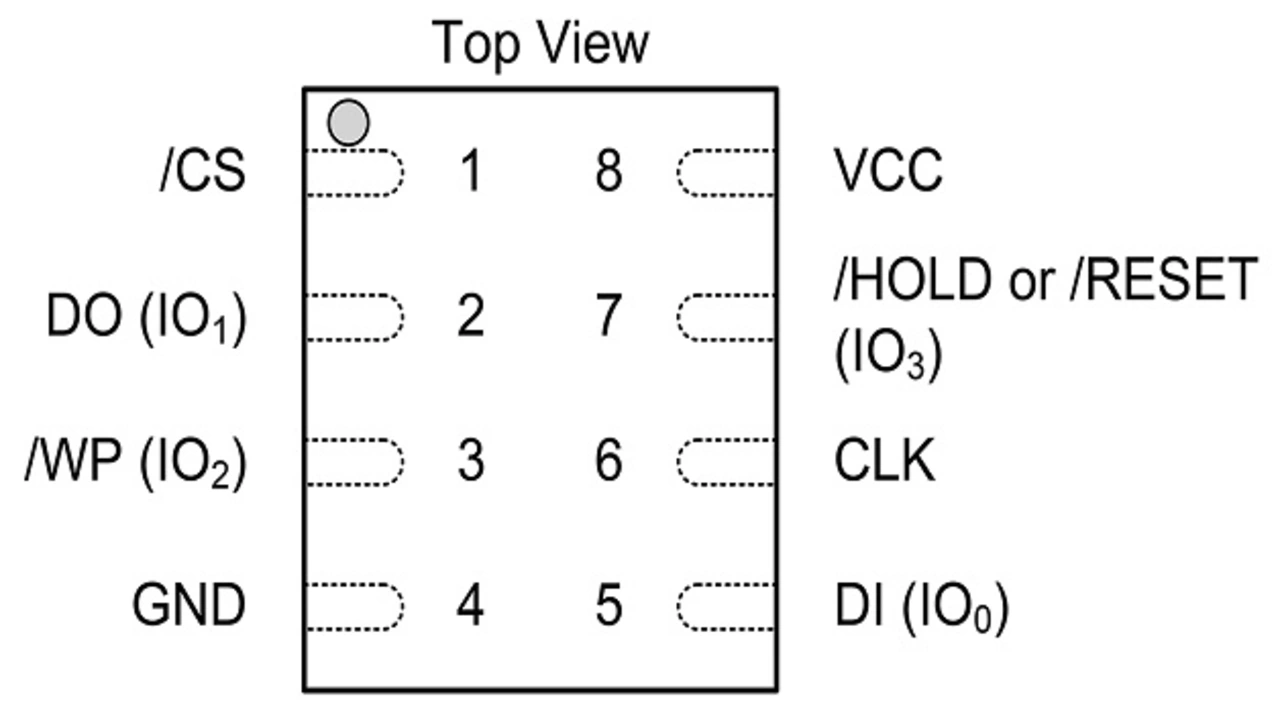

Ein NOR-Flash-Speicher-IC kann eine Hardware-Sperre für die Firmware-Einstellungen des Block-/Sektorschutzes (Register) verwenden, um zusätzliches Vertrauen in den Schutz kritischer Daten, zum Beispiel des Bootcodes, zu schaffen. Dies wird über den WP-Pin erreicht (Bild 1). Den Status des WP-Pins steuert man mit dem Registerbit SRP (Status Register Protect).

Manche Anwender sind vielleicht mit dem WP-Pin in parallelen Flash-Chips vertraut, der über eine einfache Schreibschutzfunktion verfügt. Die Funktion des WP-Pins bei seriellen NOR-Flash-Chips ist eine andere: Er schützt die Registereinstellungen, die den Schreib-/Löschschutz von Blöcken und Sektoren über die Registerbits BP und SEC konfigurieren. Sobald man die BP- und SEC-Einstellungen gemacht hat und der WP-Pin aktiviert ist (WP=Low), kann man keine Änderungen an den BP- und SEC-Einstellungen mehr vornehmen, ohne den WP-Pin auf High zu ziehen.

Kritische Daten gut geschützt

Anwender von seriellen NOR-Flash-Chips wie den SpiFlash-Produkten des taiwanischen Herstellers können gewährleisten, dass geschützte Bereiche nach der Auslieferung ab Werk niemals programmiert oder gelöscht werden. So werden geschützte Blöcke wirkungsvoll zu einem einmalig programmierbaren Speicherbereich (OTP). Erreichen lässt sich dies durch eine permanente Sperre der Registereinstellungen für den Block- und Sektorschutz. Diesen sogenannten Active Permanent Lock kann man mit dem Registerbit SRL (Status Register Lock) aktivieren. Dadurch sind die Daten in geschützten Blöcken dauerhaft und unwiderruflich gesperrt. Wird jedoch in Zukunft ein Fehler im geschützten Code gefunden oder soll ein wichtiges Sicherheitsupdate erfolgen, kann dies nicht geschehen, wenn der Active Permanent Lock implementiert wurde. Dies ist eine schwerwiegende Konsequenz. Daher macht Winbond es erforderlich, eine spezielle Befehlssequenz zur Implementierung des Active-Permanent-Lock einzuhalten. Sie ist nur auf Anfrage bei dem Unternehmen verfügbar; die Befehlssequenz ist nicht im Datenblatt aufgeführt.

Für die meisten Nutzer ist die Power-Supply-Lock-Down-Funktion die bessere Option: Sie hat die gleiche Wirkung auf das Sperren der Statusregistereinstellungen, wenn der Chip aktiv ist; jedoch wird die Statusregistersperre beim Ausschalten jedes Mal deaktiviert. Dadurch öffnet sich ein Fenster, in dem man bei jedem Einschalten die Registereinstellungen ändern kann, bevor die Power-Supply-Lock-Down-Funktion wieder aktiviert wird.

Mit den beschriebenen Schutzfunktionen für SpiFlash-NOR-Flash-Speicher können Entwickler das Risiko vermeiden, dass ihr System aufgrund von Bitfehlern, oder weil ein Host-SoC versehentlich kritische Daten überschreibt, funktionsunfähig wird. (kv)

- Daten in Speicher-Chips besser schützen

- Funktion des Merkmals TB-Bit