PCB-Design-Tools

Design-Werkzeuge um Komponenten in Leiterplatten einzubetten

Fortsetzung des Artikels von Teil 1

Design-Werkzeuge um Komponenten in Leiterplatten einzubetten

Arten eingebetteter Komponenten

Es gibt drei Hauptarten von in Leiterplatten integrierten passiven Komponenten: Widerstände, Kondensatoren und Induktivitäten, Bild 1 zeigt den Lagenaufbau einer FR-4-Leiterplatte mit mehreren eingebetteten passiven Komponenten.

Die folgenden Abschnitte beschreiben diese Komponenten im Detail und erläutern für jeden Typ die entsprechenden Anforderungen an das Designwerkzeug.

Eingebettete Widerstände

Ein eingebetteter Widerstand befindet sich auf einer einzelnen Lage. Dies kann jede Art von physikalischer Lage sein, selbst eine Versorgungslage. Ein Widerstand verfügt über zwei Kupferanschlüsse mit Widerstandsmaterial zwischen den Anschlussflächen. Die Form des Widerstandmaterials kann ein einfaches Rechteck sein oder ein Mäandergebilde wie in Bild 2.

In allen Fällen überlappt das Widerstandsmaterial die Kupferanschlüsse. Um Signal-Kurzschlüsse oder Unterbrechungen mit dem Widerstand zu vermeiden, ist eine lagenspezifische Abgrenzung der Leiterbahnen, Durchkontaktierungen, Bohrungen und Platzierungen rund um den Bereich des Widerstandsmaterials erforderlich. Die Herstellung eingebetteter Widerstände beinhaltet Ätz- oder Druckverfahren. Bild 3 zeigt schematisch die Prozessschritte für geätzte Widerstände.

Die Widerstandsschichten werden von Materiallieferanten wie Ohmega Technologies und Gould Electronics kombiniert mit einer Kupferfolie für die Leiterplattenfertigung angeboten. Sowohl Ätz- als auch Druckverfahren erzeugen Widerstände mit Toleranzen von 8 bis 16 %. Dies mag für einige Anwendungsfälle akzeptabel sein, damit sich diese Technik jedoch durchsetzt, müssen die Toleranzen auf eine von Widerstandsbauteilen übliche Größenordnung – bis auf 1 % – gesenkt werden.

Um präzisere Widerstandswerte zu erhalten, werden eingebettete Widerstände gemessen und auf den Sollwert getrimmt. Viele Entwickler verwerfen die Idee, Widerstände einzubetten, wenn sie die Kosten des Laser-Trimmens sehen. Doch hier sollte nicht Schluss sein, sondern genauer hinterfragt werden. Häufig wird vergessen, dass nicht die absolute Toleranz eines Widerstands entscheidend ist, sondern die Relation zwischen mehreren Widerständen in derselben Schaltung. Da alle eingebetteten Widerstände mit demselben Prozess gefertigt werden, ist ihre relative Genauigkeit viel besser als die 8 bis 16 % Toleranz, die typisch für die Technik genannt werden.

Eingebettete Induktivitäten

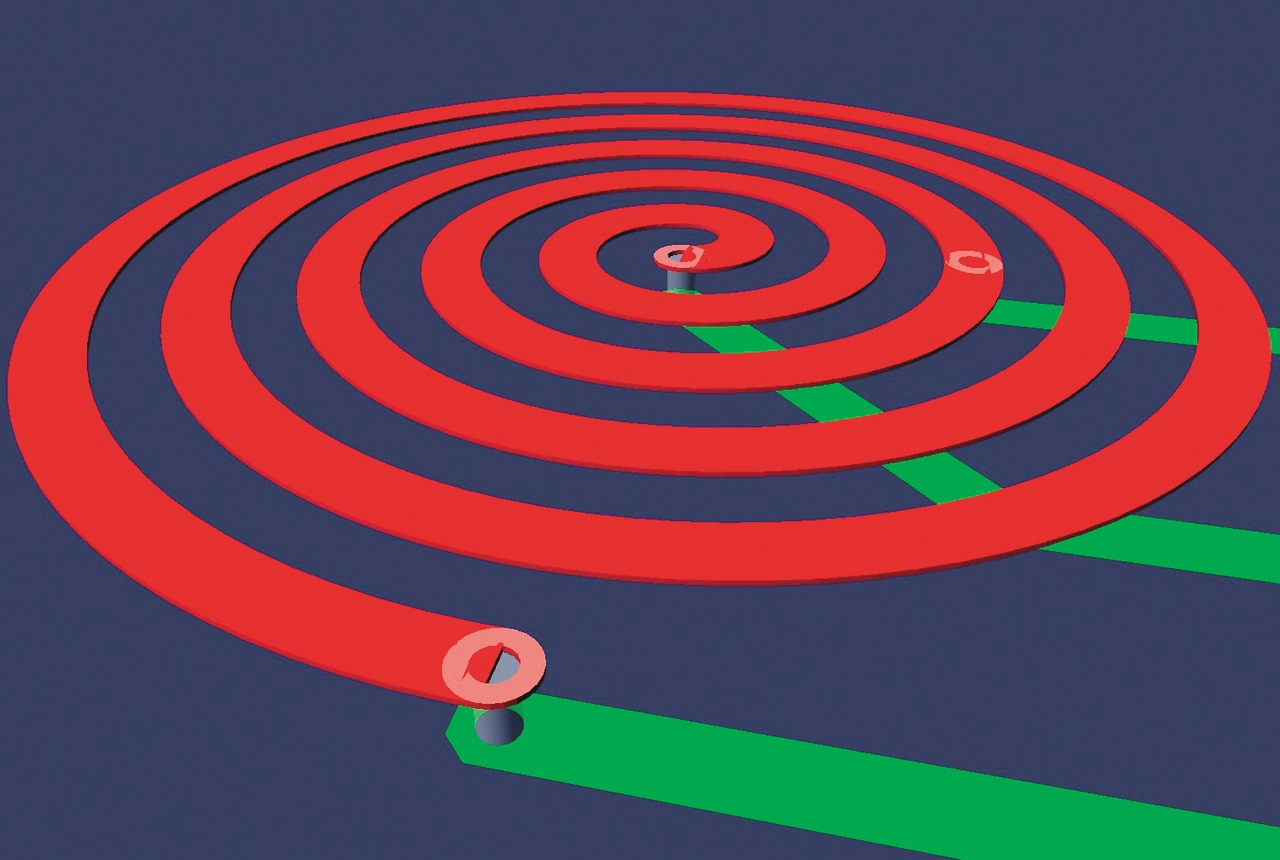

Induktivitäten eignen sich ebenfalls zur Integration in Leiterplatten. Im Unterschied zu eingebetteten Widerständen oder Kondensatoren benötigen sie aber keine speziellen Materialien oder Fertigungsverfahren. Sie bestehen aus Kupfer und verwenden dünne Leitungen sowie spiralenförmige Geometrien. Eine Kombination aus Leiterbahnbreite, Anzahl der Windungen, Form und Leitungslänge definiert die Induktivität. Bild 4 zeigt eine Kupferspirale, die mit Blind/Buried Vias an Leiterbahnen angeschlossen ist.

Die Nähe zu anderen Signal-Leitungen kann die Induktivität von eingebetteten Spulen verringern. Deshalb sollten die lagenspezifischen Abgrenzungen der Leiterbahnen, Durchkontaktierungen, Bohrungen und Platzierungen größer sein als die geometrischen Abmessungen der Spule. Aufgrund der feinen Leiterbahnen und Abmessungen eingebetteter Spulen ist bei der CAD-Ausgabe des Layouts und dem Filmbelichter/Fotoplotter eine hohe Auflösung erforderlich. Nur so lassen sich korrekte Abgrenzungen gewährleisten.

Aus der Leiterplattenperspektive befinden sich bei eingebetteten Induktivitäten ein Anschluss außerhalb der Spiralform und der andere in der Mitte. Die Leiterbahn zum mittleren Anschluss der Spule muss auf einer anderen Lage geführt werden, weshalb dies mit einer Durchkontaktierung oder per Blind oder Buried Via erfolgt. Die Geometrien von eingebetteten Induktivitäten können sich über mehr als eine Lage erstrecken. Auch hier können Blind oder Buried Vias die Verbindung zwischen den Spiral- Lagen herstellen. Eine Maskenbibliothek mit Formen und ein Modellier-Tool zur Generierung und Verifikation einer eingebetteten Induktivität wären nützliche Hilfsmittel, um Spulen in einer Leiterplatte einzubetten.

Aktive Komponenten einbetten

Wesentlich höhere Funktionsdichten sind auf einer Leiterplatte möglich, wenn aktive Komponenten wie integrierte Schaltungen ohne Gehäuse verwendet werden. Die Halbleiter-Dies können dann direkt in oder auf einer Leiterplatte platziert werden (Bild 5). Hohlräume zur Bauteilaufnahme, drahtgebondete Chips, Die-on-Board, Die-on-Die zusammen mit modifizierten Flip-Chip-Gehäusen lassen sich alle in eine Leiterplatte integrieren. Microvias unterstützen die Leiterbahnführung von und zu den Drahtbond- und BGA-Anschlussflächen (Fanout), die alle zu einer internen Lage führen können.

Jobangebote+ passend zum Thema

Leiterplatten- und Bauteil-Design in einem CAD-Programm

Einer der wichtigsten Punkte beim Leiterplattenlayout ist, dass die Verwendung von eingebetteten passiven Komponenten ein Herstellungs- und kein Montageverfahren ist. Wird dies in der Konstruktionsphase berücksichtigt, erhält der Leiterplattenentwickler die nötige Flexibilität, um die Herausforderungen der steigenden Bestückungsdichte zu meistern. Diese Flexibilität lässt sich natürlich nur realisieren, wenn das CAD-Werkzeug die eingebetteten Komponenten vollständig unterstützt. Die Aufgabe der Bauteilbibliothek ändert sich, wenn die Verwaltung von anbieterspezifischen Materialbibliotheken und der Lagenaufbau der Leiterplatten hinzukommen. Diese Bibliotheken können vom EDA-Anbieter oder Materiallieferanten zur Verfügung gestellt werden. Einige EDA-Anbieter behaupten, eingebettete Komponenten zu unterstützen, doch erfordert dies zuvor das Generieren der eingebetteten Bauteile für die Bibliothek – ein Eintrag pro physikalischer Form, Material, Toleranz, Lage etc. Die Verwaltung einer Bibliothek, die eingebettete passive Komponenten in allen denkbaren Formen und Größen sowie aus unterschiedlichen Materialien enthält, wird außerordentlich umfangreich, wenn die Verwaltung im typischen Schema einer Bauteilbibliothek geschieht. Um dieses Problem zu verringern, könnte die Bibliothek nur ein oder zwei eingebettete passive Komponenten pro Wert anbieten. Bedauerlich wäre dann aber, dass der Leiterplattenentwickler nur einen begrenzten, festgelegten Satz eingebetteter Komponenten auswählen kann und ihm so ein künstliches Limit gesetzt wird. Am besten wäre es, wenn die Bauteilbibliothek gar keine eingebetteten passiven Komponenten führt, sondern das Design-Programm die physikalische Form synthetisiert. Auf diese Weise wird die Bauteilbibliothek nicht mit eingebetteten Bauteilvariationen überfrachtet und der Leiterplattenentwickler erhält größtmögliche Flexibilität.

Synthese eingebetteter passiver Bauelemente

Der Schaltungsentwickler, der den Schaltplan für das Leiterplattenlayout vorgibt, arbeitet wie gewohnt. Denn die Werte und Toleranzen werden für eingebettete Bauelemente genau so spezifiziert wie für diskrete Komponenten. Zur Optimierung des Leiterplattenentwurfs muss der Leiterplattenentwickler den Aufbau der Materialschichten verstehen und die Flexibilität nutzen können, die sich durch Materialmodifikationen bietet. Um dies zu realisieren, muss die Design- Software während des Leiterplattenentwurfs Materialdarstellungen sowie Änderungen an Aufbau und Material unterstützen. Ein Werkzeug, das eingebettete passive Komponenten vollständig unterstützt, synthetisiert diese von anbieterspezifischen Materialien, elektrischen Anforderungen und physikalischen Parametern. Aus der Perspektive des Entwicklungsprozesses muss die Komponentensynthese in der Platzierungs- und Verbindungsphase des Leiterplattenentwurfs erfolgen. In dieser kritischen Konstruktionsphase hat der Leiterplattenentwickler optimale Einflussmöglichkeiten, um die Komponentengröße sowie die XY- und Lagen-Platzierung zu steuern. Diese parametrische Synthese leitet automatisch ein Bauelement mit dem erforderlichen Wert her. Wobei die im Schaltplan angegebenen Werte und Toleranzen sowie die Materialeigenschaften gemäß der Bibliothek und der CAD-Software des Herstellers ebenso berücksichtigt werden wie die gewünschte Form. Die Form kann auch vom Synthese-Tool vorgegeben sein – z.B., wenn enge Toleranzvorgaben einen Laserabgleich erfordern. Gegenüber der manuellen Erstellung gleichwertiger eingebetteter Bauelemente kann dieser automatische Arbeitsgang dem Leiterplattenentwickler tage- oder gar wochenlange Arbeit ersparen. Eine sinnvolle Synthese einbetteter Komponenten bietet dem Leiterplattenentwickler für jeden Komponenten- Referenzbezeichner mehrere physikalische Bauteiloptionen. Er hat dann die Möglichkeit, die zur jeweiligen lokalen Platzierung in der Leiterplatte am besten geeignete Form zu wählen. Somit können z.B. zwei eingebettete 10-kΩ-Widerstände unterschiedlich dargestellt werden.

Kompromiss-Analyse

Wenn der Leiterplattenentwurf fortschreitet, muss entschieden werden, welche passiven Komponenten eingebettet und welche als diskrete Bauelemente belassen werden. Hierbei ist abzuwägen, ob die Platz- und Leistungsfähigkeits- Vorteile, die sich durch das Einbetten der Komponenten ergeben, die höheren Fertigungskosten rechtfertigen. Die Herstellungskosten erhöhen sich immer dann, wenn für ein eingebettetes passives Bauelement ein neuer Werkstoff erforderlich ist, der einen zusätzlichen Produktionsschritt notwendig macht. Es gibt ein Tool, das dem Leiterplattenentwickler hilft, diese Abwägungen vorzunehmen und genau festzulegen, in welcher Form jedes einzelne Bauelement implementiert wird.

Unterschiedliche Anforderungen für verschiedene Bauteile und Einbett-Techniken

Interaktive und automatisierte Design-Werkzeuge erlauben es Entwicklern, die Formen und Werte eingebetteter Komponenten individuell oder als ausgewählte Gruppen zu synthetisieren, um Bauteildichte, Werte und Fertigungsregeln zu optimieren. Offline- und Online-Design-Rule-Checks (DRC) sorgen in der Konstruktionsphase dafür, dass die eingebetteten passiven Komponenten auf der für die Fertigung passenden Lage platziert sind und die entsprechenden Werte und Toleranzen einhalten. Eingebettete aktive Komponenten haben demgegenüber vielfältigere Anforderungen. Die Flip-Chip-Montage wird wegen der kleineren physikalischen Abmessungen für das Einbetten immer beliebter. Flip-Chip-Bauteile können in einer offenen Aussparung im Substrat platziert oder in die Substratschichten integriert werden. Im Vergleich zu eingebetteten passiven Komponenten sind sie wesentlich dicker – und zwar sowohl bezüglich ihrer physikalischen Abmesungen als auch wegen der Kontaktierung. Sie werden entweder mit Lotkugeln verlötet oder per Drahtbonden kontaktiert. In einer Aussparung platziert, können aktive Komponenten von weiteren Leiterplattenschichten vollständig bedeckt werden. Damit sind sie komplett in der Leiterplatte eingebettet und schaffen auf der Platinenoberfläche Platz für andere Komponenten. Falls die Anschlüsse per Drahtbonden hergestellt werden, können die integrierten diskreten aktiven Komponenten zwar in einem Hohlraum sitzen, sie sind aber für das Drahtbonden zu einer der Platinenoberflächen frei zugänglich. Das CAD-Programm muss flexibel genug sein, um Bonddrähte vom Chip zur Leiterplatte und zu speziellen Lagen der Leiterplatte zu generieren. Zudem muss das Software-Tool es dem Leiterplattenentwickler ermöglichen, die Drahtbond-Pads zu verschieben, um weitere Leiterbahnen und Durchkontaktierungen unterbringen zu können. Dabei dürfen die Bonddrähte untereinander aber keinen Kurzschluss erzeugen.

Generieren der Produktionsdaten

Der letzte Schritt im Leiterplattenentwurf ist das Erstellen der Fertigungsdaten, das Post-Processing. Um zu bestimmen, was die Ausgabedateien der einzelnen Lagen enthalten sollen, muss das Design-Programm Boolesche AND-, OR- und XOR-Filter zur Verfügung stellen, die die Materialien erfassen. Diese Ausgabedateien werden je nach Materialien und Fertigungsverfahren zur Herstellung geeigneter Filme, Masken oder Schablonen verwendet. Weitere Ausgabedateien müssen Laser-Trimmer, Baugruppentester, die XY- und Lagen-Positionierung, Lage der Pads, Bonddrähte sowie CNC-Fräs- und -Bohrmaschinen unterstützen. Alle diese Ausgabedaten werden pro Lage und Substratschicht benötigt.

|

Isaac verfügt über einen Abschluss als B.S. in Electrical Engineering des Rensselaer Polytechnic Institute und ist seit mehr als 30 Jahren in der EDA-Industrie im Bereich der Leiterplattenund IC-Technik tätig. Seine Laufbahn begann er bei IBM, wo er EDA-Systeme für das IBMinterne Design der Highend-ICs und Leiterplatten des Unternehmens entwickelte. Aktuell ist er Director of Market Development der Systems Design Division bei Mentor Graphics. john_isaac@mentor.com |

- Design-Werkzeuge um Komponenten in Leiterplatten einzubetten

- Design-Werkzeuge um Komponenten in Leiterplatten einzubetten