Signalintegrität in Embedded-Anwendungen

Simulieren lohnt sich

Wenn sich Entwickler von Embedded-Hardware an den »Design Guide« des Prozessorherstellers halten, dann funktioniert ihr Layout in den meisten Fällen, weil in diesen Leitfäden genügend Overhead eingeplant ist. Doch wie groß ist der Sicherheitsabstand tatsächlich? Genügt vielleicht sogar eine Multilayer-Platine mit weniger Lagen? Wo liegen die Schwachstellen in meinem Layout? Und wie vermeide ich ein Redesign? Bei diesen und ähnlichen Fragestellungen kann eine analoge Simulation helfen.

Meist halten sich die Entwickler von Embedded-Produkten (z.B. mit Intels »Atom«) brav an die »Design Guides« des Prozessorherstellers. Leider sind diese so ausgelegt, dass sie mehr oder weniger für alle möglichen Anwendungen passen. Somit lassen sich diese aber bei den speziellen Anforderungen, wie sie oft auf modernen Embedded-Boards zu finden sind, nie in allen Punkten einhalten. Um zu klären, wo der Entwickler den Design-Guide verletzen darf und was er deswegen an anderer Stelle gewinnt, ist eine Simulation unumgänglich.

Damit kann er die Signal- und Power-Integrität quantifizieren und so bestimmen, an welchen Stellen er »sparen« kann und wo er dies besser vermeidet. Bei der Komplexität heutiger Designs können selbst erfahrene Leute dies kaum mehr richtig abschätzen. Ein Redesign einzuplanen, nur um ein Problem zu beseitigen, das der Entwickler hätte vorab erkennen können, verbietet sich heutzutage nicht nur der Kosten wegen, sondern auch wegen den engen Vorgaben an die »Time to Market«.

Jobangebote+ passend zum Thema

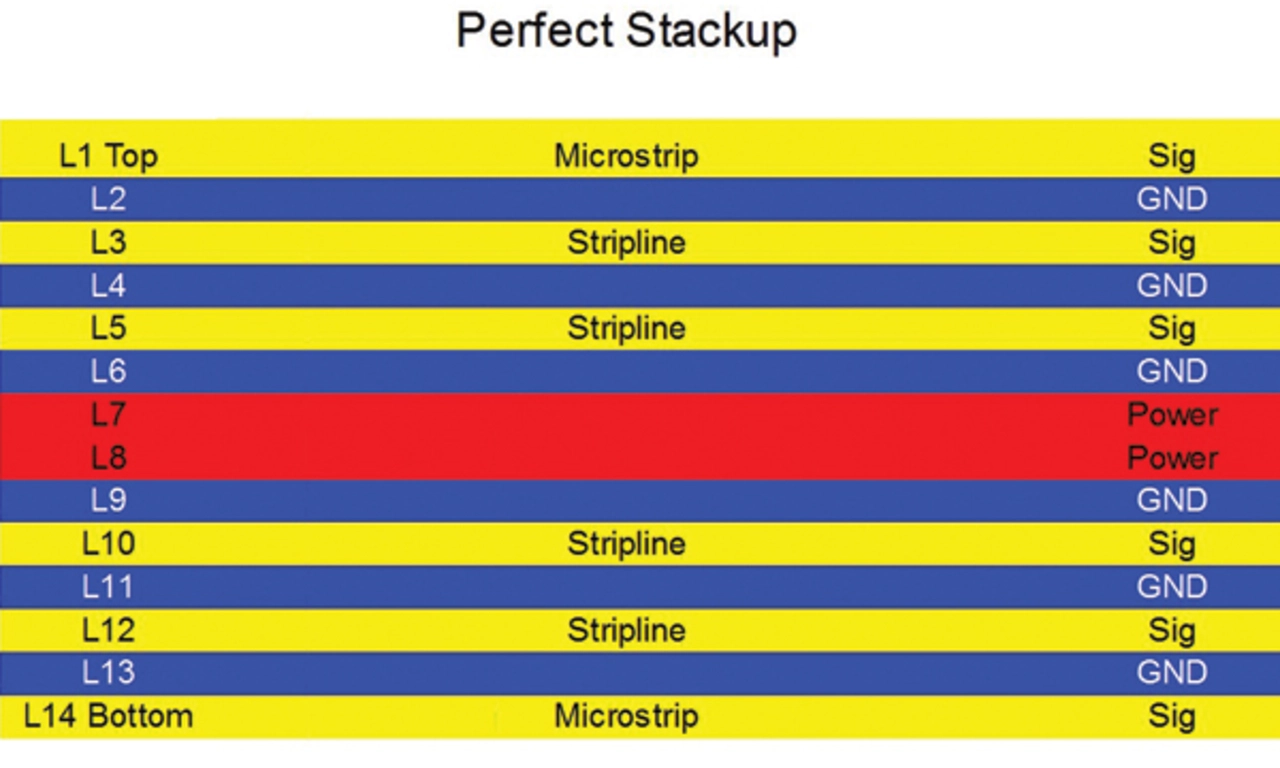

Eine der ersten Fragen die sich stellt, ist die nach dem Lagenaufbau (Stackup). Ein idealer 14-lagiger Stackup (Bild 1a) resultiert theoretisch in »perfekten« Stripline-Verdrahtungen auf den Innenlagen. Eine ideale Stripline (Streifenleitung) zeigt sehr wenig Nebensprechen (Crosstalk).

Speziell im Bereich des »Fan-outs« unter komplexen Chips (dem Bereich, in dem alle Signale eines Prozessors auf sehr engem Raum zusammengeführt werden müssen) ist dieses theoretisch »ideale« Routing aber nicht gegeben. Durch die große Anzahl der Vias (Durchkontaktierungen) in diesem Bereich liegt an dieser Stelle die Begrenzung in der Performance und nicht im Bereich des normalen Routings.

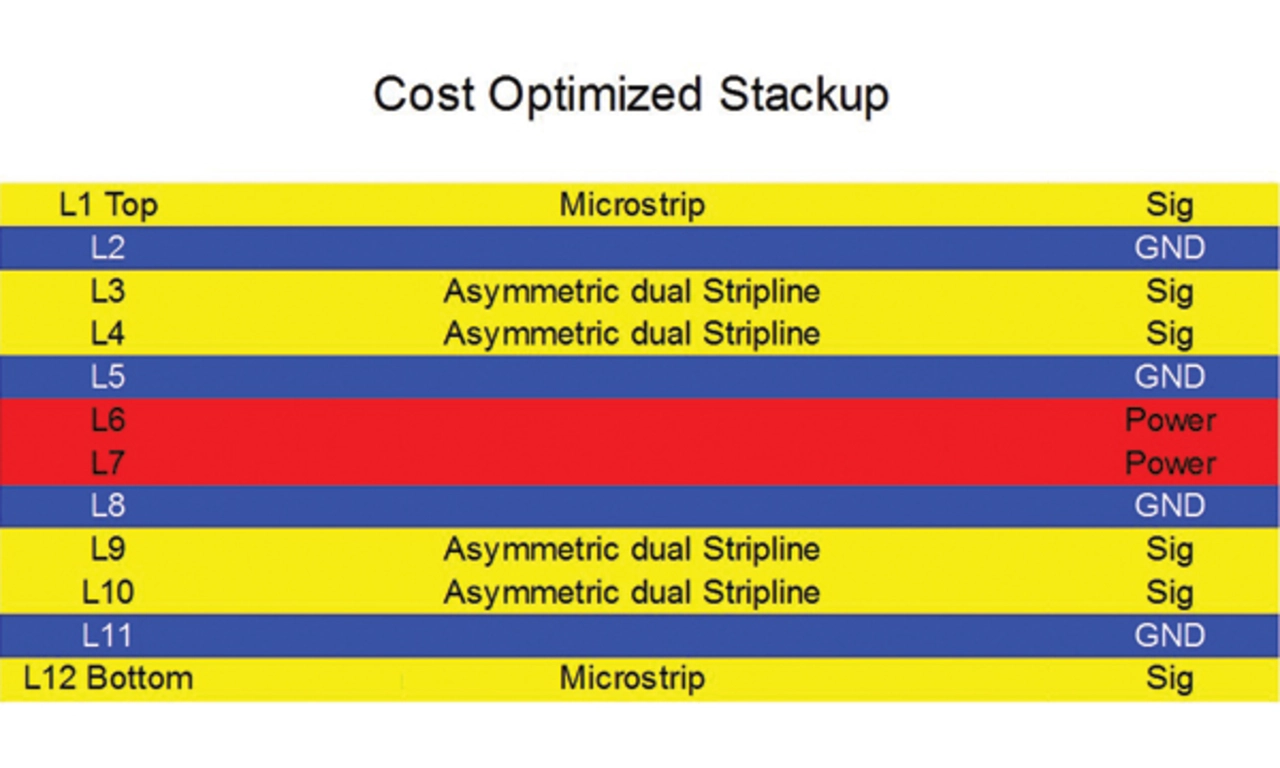

Damit ist ein kostengünstigerer 12-Lagen-Stackup mit asymmetrischen »Dual Striplines« (Bild 1b) nicht wirklich schlechter als die Variante mit 14 Lagen. Den Vorteil des geringen Nebensprechens hat auch diese Art der Leitungsführung.

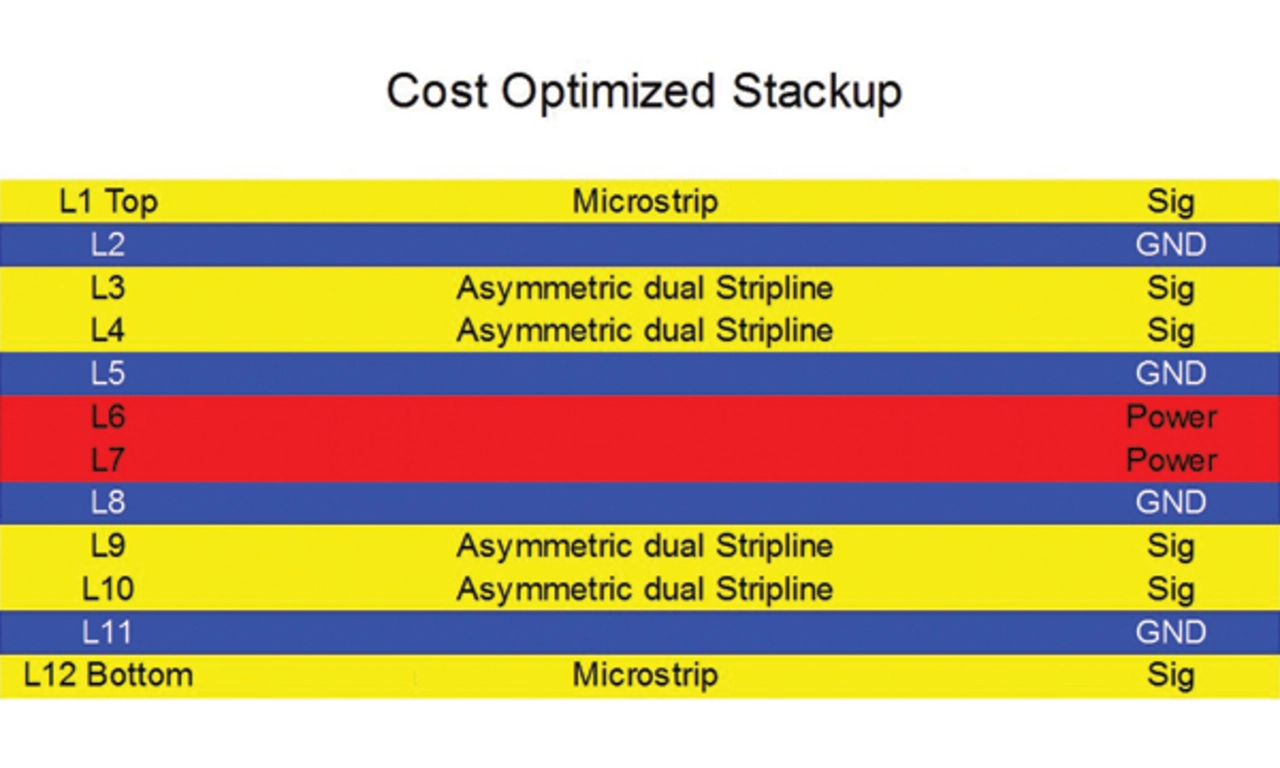

Eine zusätzliche Alternative für einen Aufbau mit 12 Lagen ergibt sich dadurch, dass manche Busse (z.B. die Kommandos und Adressen bei Commodity-DDRx-Speichern) gegen die Versorgungsspannung referenziert sind (Bild 1c).

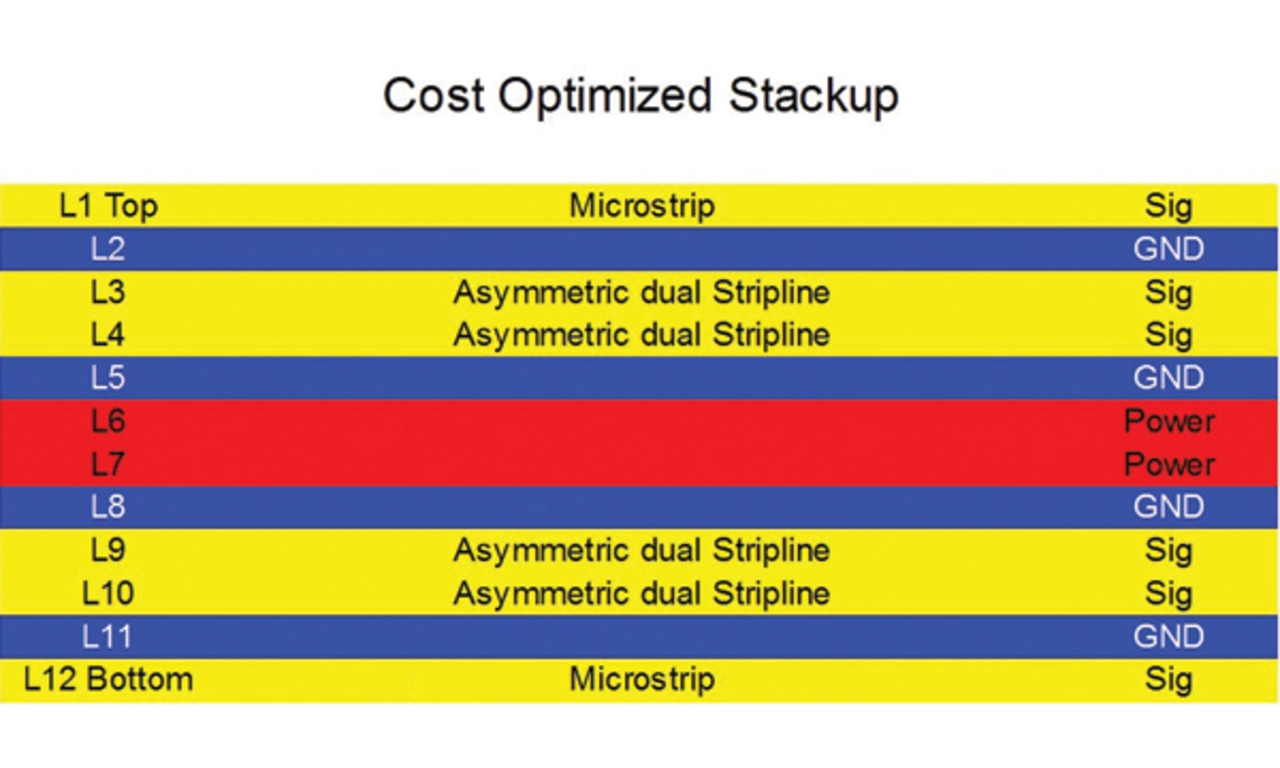

Eine Kombination der Ideen der Stackups 2 und 3 ergibt einen Aufbau mit 10 Lagen (Bild 1d) der immer noch sechs Routing-Lagen und jeweils zwei Power- und GND-Lagen hat. Sicherlich bringt dieser Stackup Einbußen in der Leistung mit sich, aber für viele Anwendungen wird er ausreichen. Allerdings ist ein Designer gut beraten, sich die Performance genau anzusehen, speziell die Power-Integrity (PI). Kopplungen von Versorgungslagen in Signale oder der Einsatz von Split-Planes wollen gut durchdacht und wohlüberlegt sein. Aber bei entsprechender Optimierung durch Simulationen kann ein 10-Lagen-Design besser sein als ein nicht simuliertes Design in 14 Lagen.

- Simulieren lohnt sich

- Vergleichssimulation und absolute Bewertung