Baugruppen-Entwurfstechnik

Flexibel und produzierbar

Fortsetzung des Artikels von Teil 1

Überlegungen zur Bauteilplatzierung

Die am Markt kommerziell verfügbaren CAD-Werkzeuge können Komponenten eigenständig richtig platzieren, selbst wenn sie über die Grenzen des Starrflex-Substrats hinweg verschoben werden. Diese Platzierfunktionen übernehmen sogar die bislang langwierige Aufgabe, Komponenten auf die richtigen Oberflächen-Layer zu verschieben. Aber sind diese Ergebnisse auch gut genug? In den meisten Fällen kommen in Flex-Zonen andere Bauteilgehäuse zum Einsatz als in starren Zonen. Zum Beispiel sind Padstacks für Flex-Zonen meist länger, um die Biegung des Materials zu unterstützen. Deshalb sollte das CAD-System das Gehäuse dem richtigen alternativen Symbol für die jeweilige Technologie-Zone zuordnen können.

Überlegungen, die Verbindungen betreffend

Das Routing zwischen „flex“ und „starr“ lässt sich auf ein Wort reduzieren: Bögen erstellen. Innerhalb einer Flex-Zone, ob nun am Baugruppenrand oder bei den Teardrops, müssen Bögen und aufgeweitete Übergänge vorgesehen werden. Geeignete CAD-Werkzeuge müssen ein Routing mit Gruppenfunktionen unterstützen, um zum Beispiel einen Bus über die Flex-Zone zu führen, und sie müssen gleichzeitig die Kontur der Baugruppe im Blick behalten. Übergänge von Linienbreiten sollten abgeschrägt werden und alle Pin/Via-Verbindungsstellen sollten Teardrops erhalten, um die Beanspruchung an den Lötstellen zu reduzieren.

Fortschritte bei der CAD-Werkzeugentwicklung haben im Laufe der letzten Jahre dafür gesorgt, dass Leiterbahnen während der Bearbeitung nach Bedarf verschoben werden können. Jedoch ist dies größtenteils immer noch eine Herausforderung bei bogenförmigen Leiterbahnen. Außerdem sollte sichergestellt sein, dass der Entwickler durch das Hinzufügen eines zusätzlichen Signals zu einer gerouteten Bus-Struktur nicht gezwungen wird, ein Teil des Routing nach einer Änderung des Gruppen-Routing wieder löschen zu müssen.

Jobangebote+ passend zum Thema

In-Design-Inter-Layer-Tests reduzieren Iterationszyklen

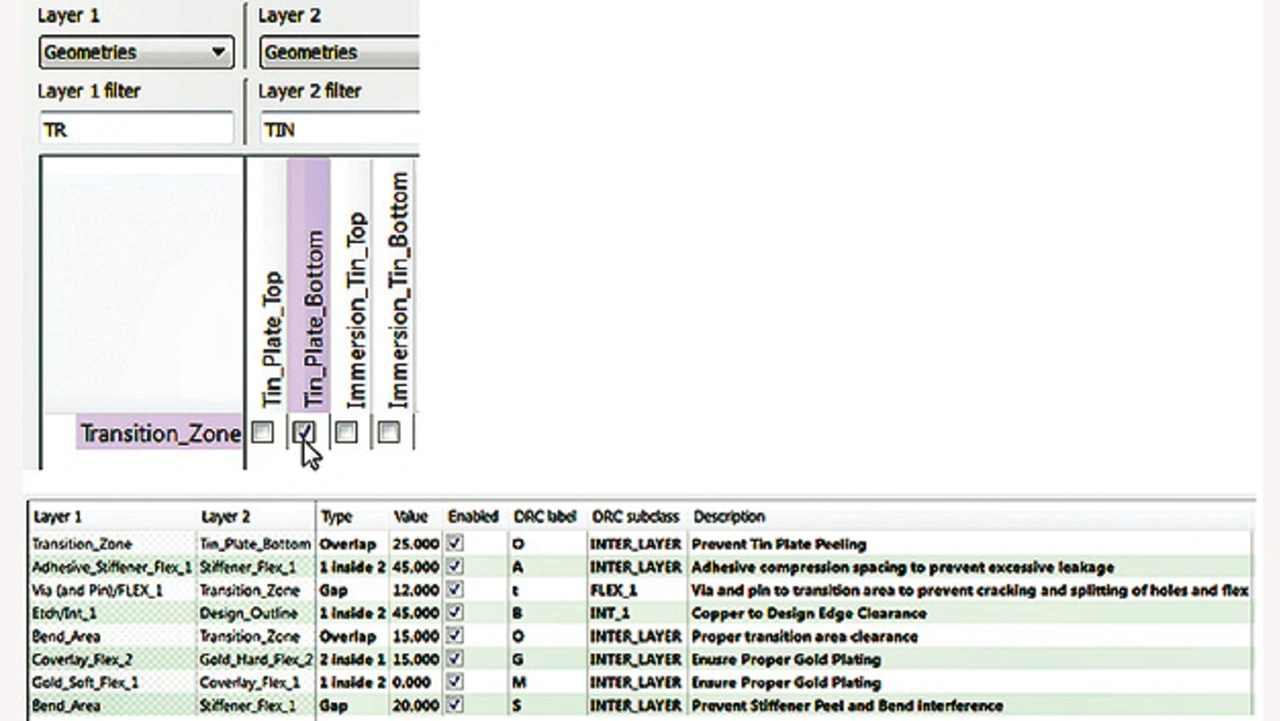

Da sich ein Leiterplatten-Entwickler mit vielen verschiedenen Materialien und verschiedenen Regeln befassen muss, sollte die Erstellung von Regeln für die Kombination von Lagen intuitiv und einfach durchführbar sein. Ein einfacher, schrittweiser Prozess (Bild 5) umfasst dabei folgende Schritte:

- Auswahl der Lage durch Anklicken des jeweiligen Kontrollkästchens in der Layer-Matrix

- Auswahl der Regel

- Einstellung des Werts

- Definition einer Kennzeichnung, die für den Entwickler aussagekräftig ist

- Einstellung des DRC-Display-Layer

- Hinzufügen einer Beschreibung für die Regel (sollten Regeln im Tool enthalten sein)

Die Anwender sollten Inter-Layer-Prüfungen online oder offline und im Stapelbetrieb ausführen können. Wenn die Prüfungen online erfolgen, gibt der Anwender einfach die Regeln ein. Nach dem DRC-Durchlauf sollte sich der Entwickler dann auch die DRC-Ergebnisse ansehen können.

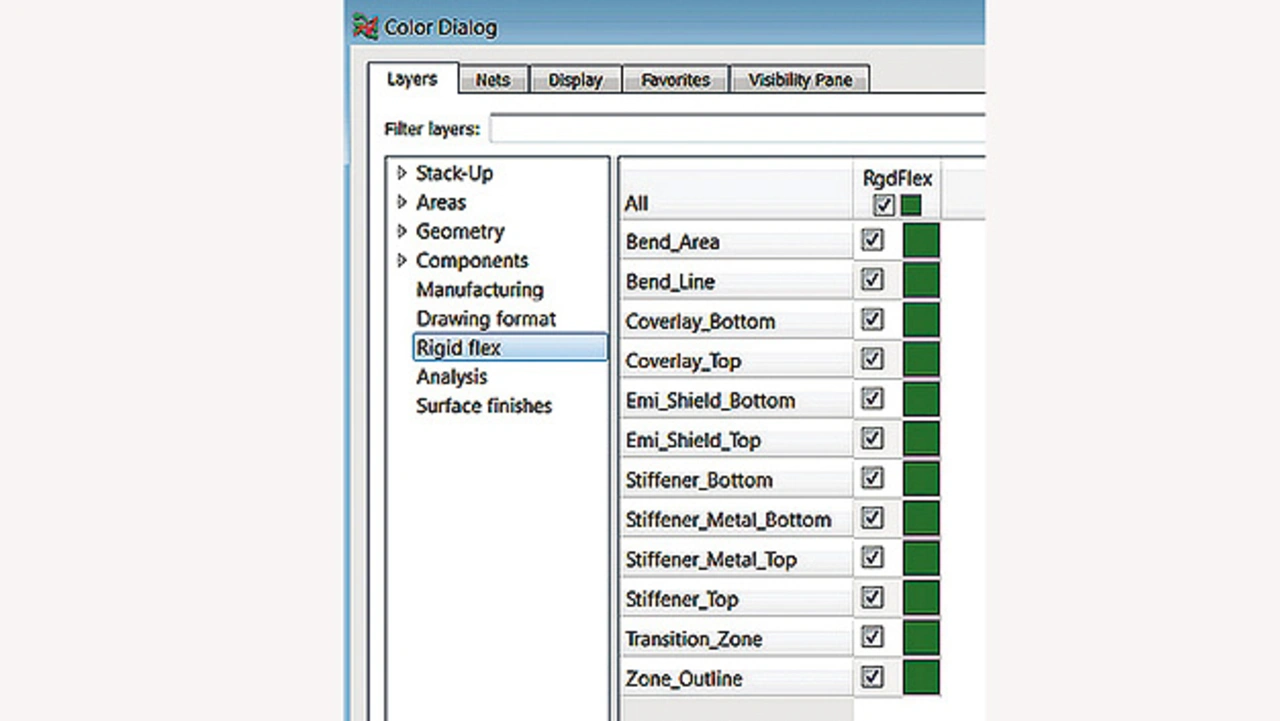

Die meisten EDA Tools unterstützen seit Langem Starr-Flex-Leiterplatten-Designs. Idealerweise unterstützen die neuen Versionen dieser Tools auch neue Herausforderungen wie mehrere Baugruppe-Lagen. Sie stellen meist eine große Bandbreite von In-Design-Prüfungen zur Verfügung, die mehr als 30 neue Flex- (Bild 6) und Oberflächen-Lagen abdecken. Die Anwender sollten auch eigene Lagen für die Überprüfung durch das Tool einfügen können, sodass sie nicht auf Tool Updates warten müssen.

Das Cadence-Allegro-17.2-PCB-Design-Portfolio zum Beispiel automatisiert Inter-Layer-In-Design-Prüfungen in Starr-Flex-Leiterplatten und stellt die hier besprochenen Fähigkeiten zur Verfügung. Da der Anwender auch DRCs für verschiedene nichtelektrische Lagen durchführen kann, hilft das Tool auch, Zeit zu sparen und Respins zu vermeiden. Das Tool unterstützt zudem ein paralleles Echtzeit-Design, sodass mehrere Leiterplatten-Entwickler an demselben Leiterplatten-Design arbeiten können.

Wie viel Zeit ein Leiterplatten-Entwickler durch die Verwendung der Starr-Flex-Design-Fähigkeiten gegenüber der Durchführung manueller DRCs (und dem Durchlaufen von Iterationen mit dem Hersteller) sparen kann, dürfte von der Komplexität des Designs abhängen. Darüber hinaus lassen sich Versäumnisse und andere Fehler verhindern, welche die Design-Qualität der Leiterplatte und die Gesamtkosten beeinflussen können. Schließlich sind Probleme, die erst vom Leiterplattenhersteller entdeckt werden, kostspieliger und zeitaufwändiger, da diese Nacharbeit und zusätzliche Iterationen zur Folge haben.

Datenübertragung an den PCB-Fertiger

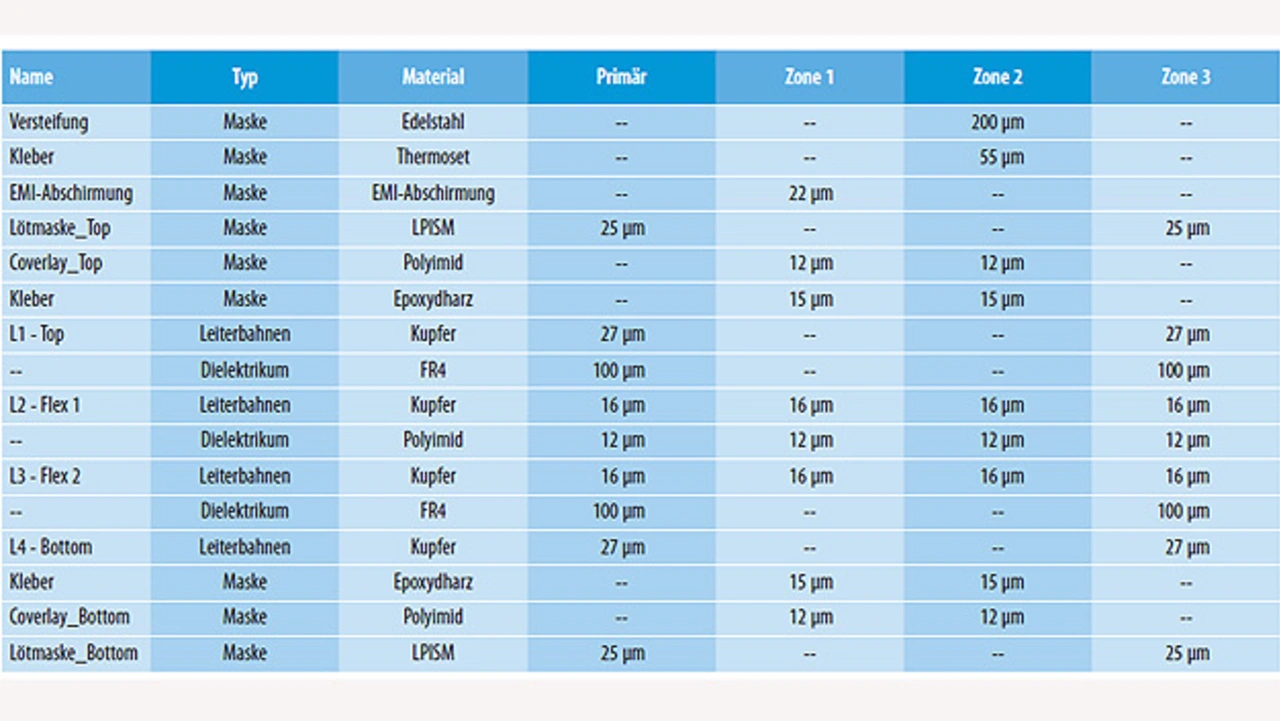

Starr-Flex-Designs sind einzigartig, wenn die Designdaten für den Herstellungsprozess übertragen werden. Die verschiedenen Materialkombinationen, aus denen das Endprodukt aufgebaut wird, müssen deshalb klar definiert werden. Die Identifizierung der verschiedenen Materialien und deren korrekte Reihenfolge, welche die Lagenstruktur festlegen, muss auch für jede Zone durch die richtige Dokumentation oder durch intelligente Produktionsdaten-Formate identifiziert werden (Tabelle).

Designhäuser und PCB-Hersteller müssen aufgrund der Designkomplexität künftig Entwurfsabläufe definieren, in denen auch Impedanz-Kontrollen sowie Flex-/Starr-Flex-Designs Berücksichtung finden. Normalerweise verwenden Designhäuser und ihre Herstellungspartner hierzu Tabellenkalkulationen, Präsentationen und andere Tools, mit denen sie sehr exakte Vorgaben an die PCB-Herstellung weiterleiten. Diese Methoden sind bis dato allerdings zeitraubend und fehleranfällig zugleich.

Fortschrittliche Leiterplatten-Entwickler verwenden deshalb IPC-2581 für einen elektronischen Austausch der Daten zum Lagenaufbau. IPC-2581 ist ein offenes, neutrales Designdaten-Austauschformat, das von mehr als 85 Leiterplatten-Design- und Lieferketten-Unternehmen weltweit unterstützt wird. IPC-2581 Revision B unterstützt zudem auch den bidirektionalen Austausch von Daten zum Lagenaufbau, sodass Probleme in späten Phasen des Designzyklus so selten wie möglich auftreten und die Designübergabe an die Fertigung nicht unnötig hinauszögern.

Der Autor

| Ed Hickey |

|---|

| ist als Product Engineering Director bei Cadence Design Systems in Chelmsford tätig und leitet dort ein Team, das den Allegro PCB Editor weiterentwickelt. Vor seinem Wechsel zu Cadence leitete er zwölf Jahre lang die PCB Design Group bei Data General und arbeitete zuvor noch bei Zuken-Redac als Produktmanager. Ed schloss sein BSEE-Studium erfolgreich am Merrimack College ab. |

ed.hickey@cadence.com

- Flexibel und produzierbar

- Überlegungen zur Bauteilplatzierung