Neue High-End-CPUs

Arm Cortex-A78 und -X1 – Schneller und energieeffizienter

Auf dem TechDay von Arm stellte sein Chefarchitekt den neuen Cortex-A78-Applikationsprozessor und ein erstes kundenspezifisches Design, den Cortex-X1, vor. Während beim A78 vor allen Dingen die Energieeffizienz gesteigert wurde, ist der X1 ein Performance-Monster. Wir erklären Ihnen beide CPUs.

Die Entwicklungszentren für Cortex-A befinden sich, wie schon mehrfach erwähnt, neben Austin in Texas in Arms Firmenzentrale in Cambridge sowie im wunderschönen Sophia-Antipolis in der Nähe von Nizza, dort wo vor zehn Jahren noch Texas Instruments seine OMAP-Prozessoren designte. Die Generationen Cortex-A73 und -75 stammten beide aus Frankreich, während die Energiespar-Varianten Cortex-A53 und -A55 aus Cambridge kamen. Der letzte Austin-Prozessor war der Cortex-A76, der sich sowohl in Smartphone-SoCs befindet, aber auch in der AE-Ausführung in Automotive-SoCs zum Einsatz kommt. Da sich der Chefarchitekt des A76, Mike Filippo nach dem Design von Arms erster Neoverse-CPU für Infrastruktur-Anwendungen in Richtung Apple verabschiedet hat, wurde das A78-Projekt unter dem Codenamen Hercules” wie schon beim A77 von seinem Kollegen Chris Abernathy (Bild 1) geleitet, der ebenfalls in Austin ansässig ist.

Nachdem schon der A77 auf dem A76, der nach vier Jahren Arbeit eine von Grund auf neu aufgebaute Mikroarchitektur implementiert hatte, aufgebaut hatte, gilt dies wenig überraschend auch für den A78: Schon 2018 hatte Filippo angekündigt, dass der A76 Basis für mindestens zwei weitere CPU-Generationen darstellen wird, der Cortex-A77 ist die Nummer 1 und der Cortex-A78 nun die Nummer 2. Sein Nachfolger im Jahr 2021 wird dagegen erstmals die neue Mikroarchitektur Armv9 implementieren und damit ein neues Diesign darstellen.

Der Cortex-A78 wurde auf Kundenwunsch im Gegensatz zum A77, dessen Fokus klar auf höherer Rechenleistung lag (der Cortex-A77 erreichte gegenüber dem A76 eine Steigerung der Integer-Rechenleistung um 23 % im selben 7-nm-Prozess bei gleicher Taktfrequenz, die somit ausschließlich über Verbesserungen an der Mikroarchitektur erreicht wurden) auf mehr Energieeffizienz und weniger Silizumflächenverbrauch getrimmt.

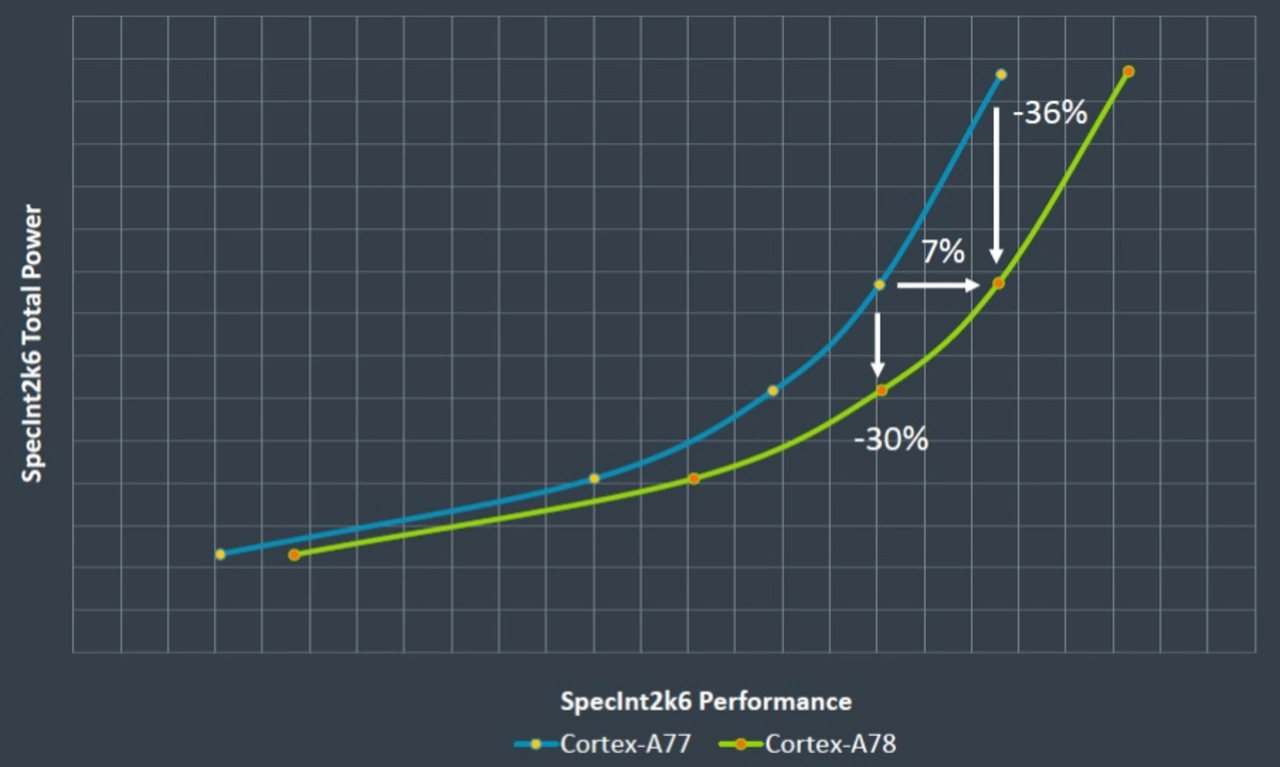

Im identischen Fertigungsprozess und identischer Taktfrequenz erzielt der A78 bei halbiertem L1-Cache von nur noch 32 KB beim Benchmark SPECint_base2006 eine somit “nur” noch um 7 % höhere Rechenleistung als sein Vorgänger, allerdings bei einer um 4 % reduzierten Leistungsaufnahme und bei 5 % weniger Flächenverbrauch auf dem Chip. Gleiches gilt für die Gleitkomma-Verarbeitung im SPECFP_2006. Anzunhemen ist, dass die Werte beim SPECFP_2017 geringer ausgefallen wären, hierzu wurden seitens Arm keine Zahlen veröffentlicht. Die Konfiguration bei diesen Messungen wurden in einem 7-nm-Prozess von TSMC, bei 512 KB L2-Cache und 4 MB L3-Cache vorgenommen.

Zur Erinnerung: Der Cortex-A77 nahm bei den Benchmarks 20 % mehr Leistung auf als der A76 und die Siliziumfläche wuchs um rund 17 %, hieran erkennt man, wie unetrschiedliche die Designziele von A77 und A78 waren.

Wie schon erwähnt, gibt es für die L1-Caches für Befehle und Daten numehr die Option, diese auf 32 KB zu begrenzen und der L2-Cache pro Core kann wahlweise auf 256 KB oder 512 KB konfiguriert werden, dazu kann ein geteilter bis 4 MB großer L3-Cache eindesignt werden. Zusammen mit einem “kleinen” Cortex-A55 kann der Cortex-A78 in einem DynamIQ-Custer betrieben werden.

Jobangebote+ passend zum Thema

Die Mikroarchitektur im Überblick

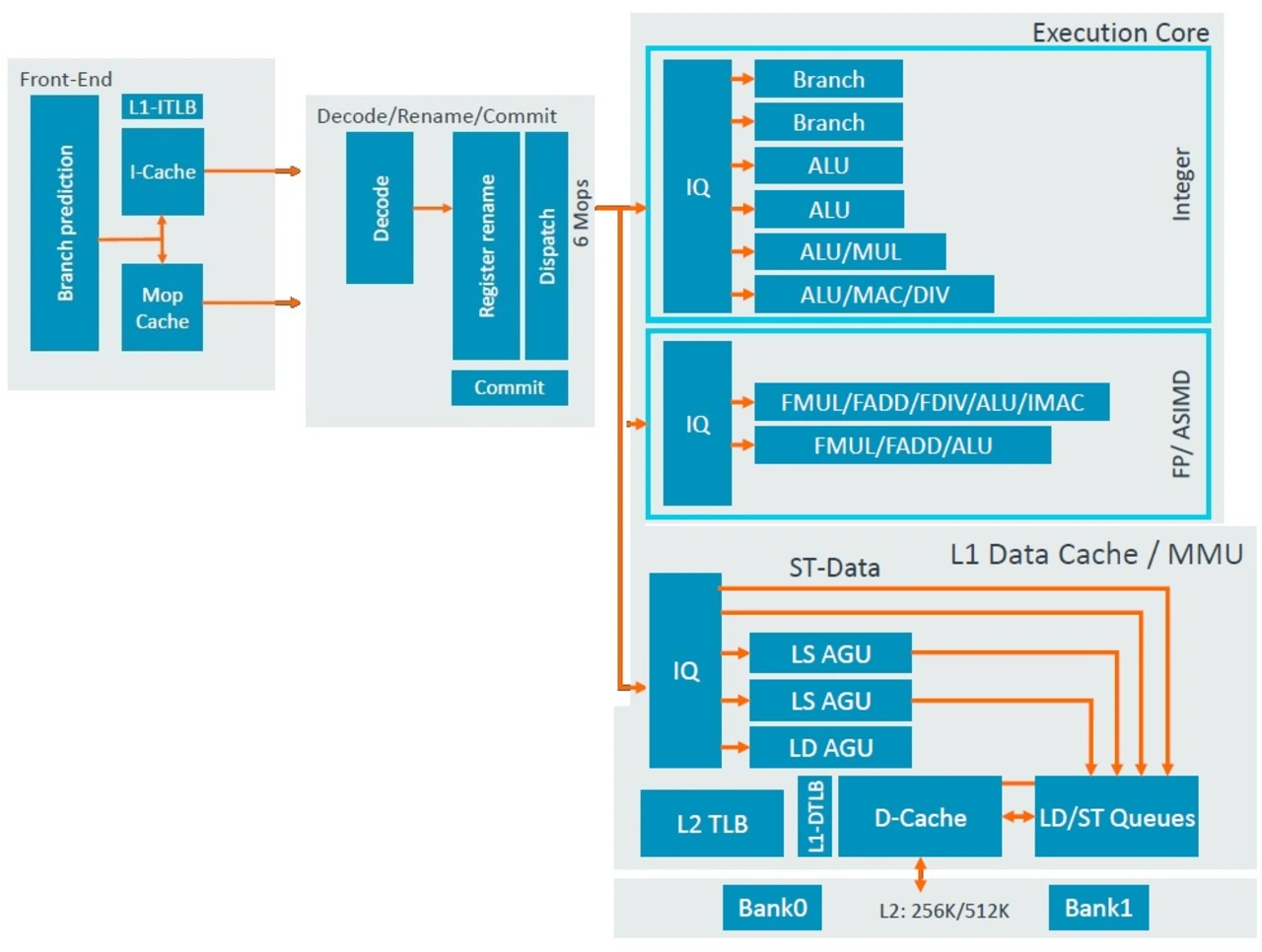

Die superskalare Out-of-Order-CPU kommt wie sein Vorgänger mit sechs Befehlsdekodern und statt mit zehn jetzt mit 11 Ausführungseinheiten daher (Bild 2). Im Frontend hat Arm erneut seine mit dem A76 eingeführte Einheit für die Sprungvorhersage und das Laden einer Instruktion eingebaut, welche predict-directed fetch genannt wird, da die Sprungvorhersage Daten direkt in die Befehlsabrufeinheit einspeist. Dies ist ein Ansatz, der einen höheren Datendurchsatz sowie eine geringere Stromaufnahme zur Folge hat.

Die Sprungvorhersage setzt dabei einen hybriden indirekten Prädiktor ein. Der Prädiktor ist von der Fetch-Einheit entkoppelt und seine wichtigsten Strukturen arbeiten unabhängig vom Rest der CPU. Er wird wie schon beim A77 von zweistufigen Branch-Target-Caches unterstützt: einem 64 Einträge umfassenden L1-BTB mit einem Taktzyklus Latenzzeit und einem 8000 Einträge umfassenden Haupt-BTB. Die Strukturen konnten gegenüber dem A77 durch eine höhere Dichte der Einträge verkleinert werden, um Fläche einzusparen. Die Sprungvorhersage unterstützt nunmehr 2 erfolgte Sprünge pro Taktzyklus, um die Fetch-Bandbreite für den Core zu erhöhen.

Die Trefferquote hinsichtlich richtig prognostizierter Verzweigungen im Programmablauf soll sich gegenüber dem A77 nochmals gesteigert haben, die Bandbreite der Sprungvorhersage beträgt weiterhin 64 Byte/Taktzyklus, was bedeutet, dass der Prefetcher bis zu 16 Instruktionen pro Taktzyklus holen kann (Arms Befehle sind 32 bit breit, Thumb-Anweisungen nur 16 bit) was ein früheres Prefetching bei L1-Cache-Misses ermöglicht und die gefürchteten Bubbles (=Pipeline-Stalls) bei angesprungenen Verzweigungen im Fall der Annahme, dass nicht verzweigt wird, verhindert.

Der A78 beinhaltet auch den mit dem A77 eingeführte Macro-Op-Cache (Mop) dar, der einen 1,5 K Einträge (ca. 50 KB) großen Befehls-Cache für dekodierte Instruktionen, die sogenannten Macro-Ops, darstellt und an ähnliche Implementierungen in Intels und AMDs x86-CPUs erinnert. Im Fall eines Cache-Hits wird die Rename-Stufe in der Pipeline direkt aus dem Mop gefüttert, er ist somit quasi ein L0-Cache und seine Trefferrate soll laut Arm bei mehr als 85 % liegen. Die Latenzzeit im Fall einer Sprungbefehlvorhersage beträgt im besten Fall nur noch 10 Taktzyklen statt 11 Taktzyklen, ein sensationeller Wert, der z.B. 30 % unter den 16 Taktzyklen von Intels Skylake-CPUs oder Samsungs Armv8-basierter CPU-Eigenentwicklung M3 liegt.

Die Verzweigungseinheit kann pro Taktzyklus acht 16-bit-Instruktionen verarbeiten, welche in eine Fetch-Warteschlange vor dem Laden eines Befehls münden. Diese Warteschlange umfasst zwölf Blöcke. Die Fetch-Einheit selbst arbeitet nur mit halbem Datendurchsatz, also pro Taktzyklus werden maximal vier 16-bit-Instruktionen geladen. Im Falle einer fehlerhaft vorhergesagten Verzweigung kann diese durch diese Architektur vor der restlichen Pipeline verborgen werden, ohne die Fetch-Einheit und den Rest der CPU zu blockieren.

Die Dekodier- und Registerumbenennungsblöcke können sechs Mops pro Taktzyklus verarbeiten. Um einen zu großen Anstieg der Leistungsaufnahme zu verhindern, wurde ein Port-sharing-Mechanismus implementiert.

Am Ausgang der Dekodierer finden sich die Macro-Ops, die im Schnitt laut Arm um den Faktor 1,06 größer als die ursprünglichen Befehle sind. Die Registerumbenennung erfolgt getrennt für Integer/ASIMD/Flag-Operationen in separaten Einheiten, die mit Clock-Gating von der Taktversorgung abgeschnitten werden, wenn sie nicht benötigt werden. Dies führt zu enormen Energieeinsparungen. Benötigt die Dekodierung beim A78 zwei Taktzyklen, so benötigt die Registerumbenennung nur einen Taktzyklus. Die Makro-Ops werden mit einem Verhältnis von 1,2 Micro-Op pro Instruktion zu Micro-Ops erweitert, am Ende der Stufe werden bis zu 12 Micro-Ops pro Taktzyklus ausgegeben.

Die Commit-Puffergröße des A78 beträgt wie beim A77 160 Einträge, wobei der Puffer in zwei Strukturen für die Befehlsverwaltung und Registerrückgewinnung aufgeteilt ist – Arm nennt es hybrides Commit-System. Dies erlaubt eine noch größere Code-Parallelisierung. Der neue A78 verbessert gegenüber dem A77 die Energieeffizienz und die Dichte der Befehle, die in den Puffer gepackt werden können, wodurch sich die Befehle pro Flächeneinheit der Struktur erhöhen.

Die Warteschlangen, Register-Umbenennungsstrukturen und Registerdateien wurden im Hinblick auf ihre Effizienz optimiert, wobei manchmal eine Verringerung ihrer Größe zu verzeichnen ist. Insbesondere bei den Registerdateien wurde die Dichte der Einträge, die sie aufnehmen können, neu gestaltet, so dass mehr Daten auf gleichem Raum untergebracht werden können.

Arm hat sogar die Größe des Out-of-Order-Fenster reduziert. Vergößerungen an dieser Stelle liefern im Allgemeinen keine hohe Rendite in bezug auf den Ernergieverbrauch und das Ziel des A78 war es ja, die Effizienz zu maximieren.

Die Ausführungseinheiten

Der Integer-Teil enthält wie bisher zwei Lade/Speichereinheiten, jedoch gegenüber dem A77 eine weitere reine Ladeeinheit, was die Lade-Bandbreite gegenüber dem A77 um 50 % steigert. Pro Taktzyklus können nunmehr 32 Bytes gespeichert werden, eine Verdoppelung der 16 Byte des A77. Auch die Schnittstelle zum L2-Cache wurde so ausgebaut, dass doppelt soviel Daten pro Taktzyklus übertragen werden können.

Auf der Integer-Seite gibt es beim A78 nunmehr vier ALUs, die in der Lage sind, einfache arithmetische Operationen in einem Taktzyklus und komplexere wie Logik-Operationen, Test/Compare-Operationen oder Verschiebeoperationen in zwei Taktzyklen durchzuführen, davon wie beim A77 eine komplexe Pipeline Multiplikations-, Divisions- und CRC-Operationen ausführen. Neu ist allerdings, dass eine zweite ALU zusätzlich Multiplikationen ausführen kann, was bedeutet, dass statt beim A77 eine nunmehr zwei Integer-Multiplikationen pro Taktzyklus ausgeführt werden können. Die Latenzzeiten blieben gegenüber dem A77 unverändert.

Der für Gleitkomma- und Vektoroperationen (ASIMD) zuständige Teil enthält wie beim A77 zwei Pipelines, wobei eine Pipeline auch für die AES-Verschlüsselung genutzt werden kann.

Laden und Speichern von Daten

Der Daten-Cache kann neuerdings statt fix 64 KB nun auch 32 KB betragen und ist 4-fach assoziativ. Die Latenzzeit bleibt bei vier Zyklen. Der ebenfalls neuerdings 32 oder 64 KB große L1-Befehls-Cache liest bis zu 32 Bytes/Taktzyklus, gleiches gilt für den L1-Daten-Cache in beide Richtungen. Der L1 ist ein Writeback-Cache. Der L2-Cache ist in 256 oder 512 KB Größe konfigurierbar und weist datenseitig die gleichen 2 × 32 Byte/Taktzyklus-Schreib- und Leseschnittstellen zum L3-Cache der DSU auf. Ein größeres Fenster für In-Flight-Lade- und Speicheroperationen führt zu noch mehr Parallelität auf Speicherebene. Die beiden Store-Daten-Pipelines haben dedizierte Ausführungsports. Es können parallel zwei µOps für die Adresserzeugung und 2 µOps für Datenspeicherungen verarbeitet werden. Die Befehlswarteschlangen wurden zur Aufrechterhaltung der Energieeffizienz vereinheitlicht.

Der A78 bekam einen nochmals gegenüber dem A77 optimierten Daten-Prefetcher mit neuen Engines für eine höhere Genauigkeit, er kann desweiteren größere maximale Adress-Distanzen arbeiten, um eine höhere Bandbreitenauslastung im DRAM zu ermöglichen. Dies bedeutet, dass die Prefetcher sich wiederholende Zugriffsmuster über größere virtuelle Adressbereiche erkennen können als zuvor.

Systembezogenes Prefetching bedeutet eine verbesserte Toleranz gegenüber unterschiedlichen Speicher-Subsystemimplementierungen, dynamische Abstände für unterschiedliche Latenzen und dynamisch angepasste Aggressivität basierend auf der DynamIQ-L3-Auslastung.

Der L2-TLB wurde von 1280 auf 1024 Seiten reduziert - dies verbessert im Wesentlichen die Energieeffizienz der Struktur, während immer noch genügend Einträge für die vollständige Abdeckung eines 4 MB großen L3-Caches beibehalten werden, wobei die Zugriffslatenz in dieser Hinsicht immer noch minimiert wird.

Im Allgemeinen verspricht Arm einen Anstieg der IPC (Instruktionen pro Taktzyklus) bei Integer-Anweisungen um 7 % und bei Gleitkomma-/Vektoroperationen ebenfalls um 7 %. Letzteres ist überraschend, da Arm im Backend die Gleitkomma-Pipelines gegenüber dem A77 unverändert gelassen hat. Die einzige Erklärung, die mir dazu einfällt ist, dass SPECInt FP sehr speicherlastig ist und hier die Verbesserungen am Speichersystem durchschlagen.

Wenn man das Speichersystem identisch konfiguriert (also mit 64 KB L1-Caches) wie beim Cortex-A77, erhält man je nach Betriebspunkt beim A78 eine um 30 % bzw. sogar 36 % geringere Lesitungsaufnahme (Bild 3).

Und last but not least: Arm rechnet damit, dass die meisten Kunden den A78 in TSMCs bald verfügbaren 5-nm-FinFet-Prozess eindesignen werden, was natürlich zu Energieeinsparungen und potentiell höheren Taktfrequenzen führt. Vergleicht man einen mit 3.0 Ghz getakteten und in 5FF implmentierten Cortex-A78 mit einem Cortex-A77, der in 7FF implementiert wird und damit “nur” 2.6 GHz erreicht, kommt man auf eine Steigerung der Integer-Rechenleistung um 20 % bei identischer Leistungsaufnahme von 1 W/Core. Oder setzt man eine feste Rechenleistung von 30 Punkten beim SPECInt2006 fest, erzielt dies ein Cortex-A78 in 5FF-Prozess mit 2.1 GHz, während der Cortex-A77 in 7FF-Fertigung auf 2.3 GHz getaktet werden muss. Der A78 nimmt in dieser Konfiguration rund 50 % weniger Leistung auf als sein Vorgänger.

- Arm Cortex-A78 und -X1 – Schneller und energieeffizienter

- Erste Cortex-X-CPU aus kundenspezifischem Entwicklungsprogramm

- Fazit