Bauteile für Wearables

Chip-Widerstände schrumpfen weiter

Durch den Erfolg von Geräten wie Smartphones oder Tablet-PCs ist die Nachfrage nach sehr kleinen passiven Bauelementen gestiegen – bei gleichbleibend hoher Qualität natürlich. Weiter angeheizt wird der Bedarf durch die aufkommenden Wearables. Was hat sich da bei Chip-Widerständen getan?

Mit der existierenden Produktionstechnik konnten jedoch seit 2004 keine Chip-Widerstände mehr hergestellt werden, die kleiner als das 0402-Format (0,4 mm × 0,2 mm) waren. Ursache hierfür war zum großen Teil die durch den Schneidvorgang bedingte große Maßtoleranz der Gehäuse (etwa ±20 µm).

Jobangebote+ passend zum Thema

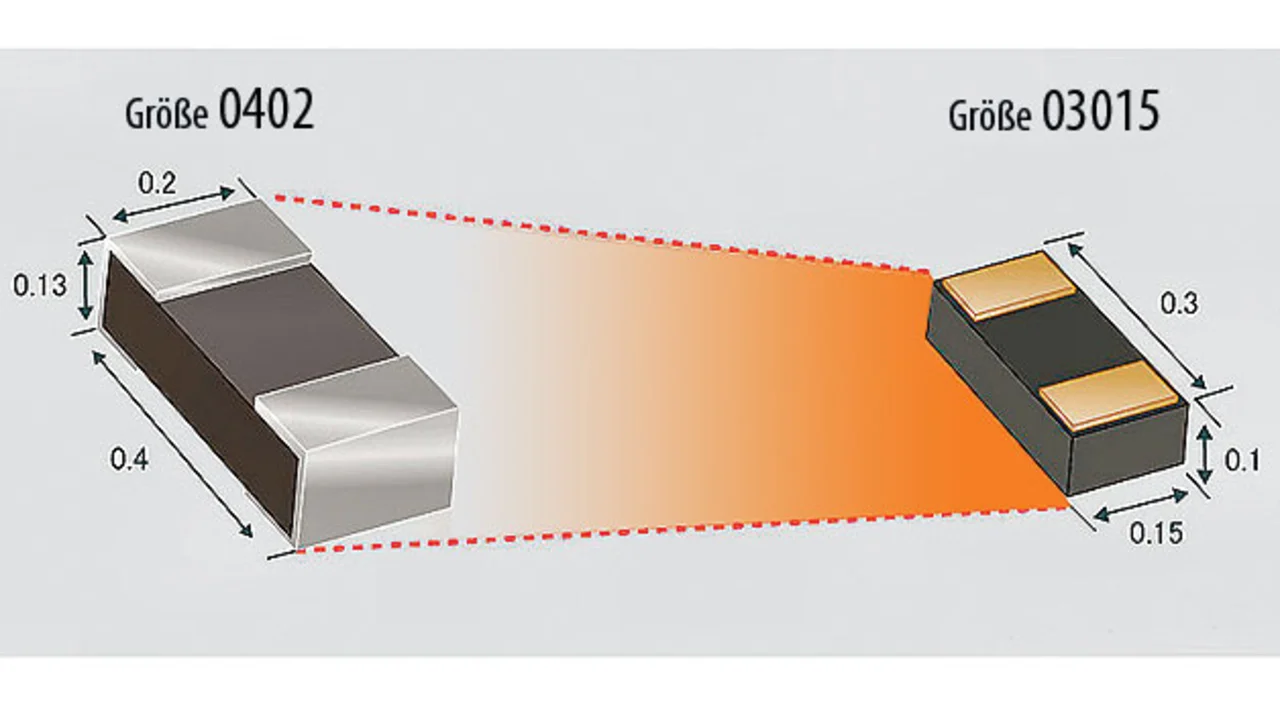

Der Halbleiterhersteller Rohm setzte aus diesem Grund auf proprietäre Technologien, die bereits bei der IC-Miniaturisierung Anwendung fanden, und übertrug diese auf diskrete und passive Bauelemente. So gelang es, kleinste Produkte anzubieten – beginnend bei Widerständen über Transistoren und Dioden bis hin zu Tantalkondensatoren und LEDs. Dabei wird eine Maßhaltigkeit von ±10 µm geboten. Im Jahr 2011 gelang dem Halbleiterhersteller die Entwicklung des weltweit kleinsten Chip-Widerstands im 03015-Format (0,3 mm × 0,15 mm), was den Footprint gegenüber dem 0402-Format um 44 % (Bild 1) verkleinerte.

2012 produzierte der Komponentenhersteller außerdem Z-Dioden im 0402-Format – seinerzeit die industrieweit kleinsten Halbleiterbauelemente. Die RASMID-Technologie beschränkt sich nicht auf die Produktminiaturisierung, sondern schließt auch Verfahren für die Befestigung auf der Platine mit ein.

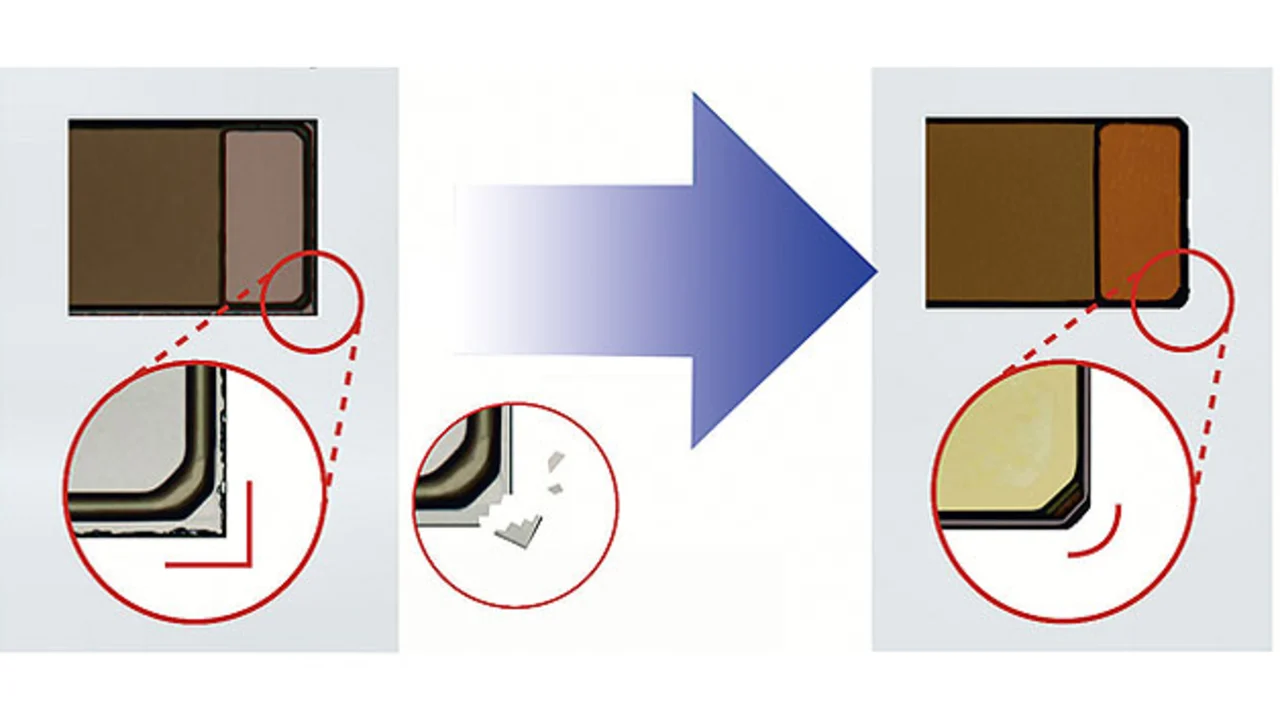

Abgesehen von der Entwicklung von Fertigungssystemen, die sich proprietäre Miniaturisierungstechnologien zunutze machen, wurden auch die Dicing-Methoden überarbeitet, um die beim Schneidprozess erzielte Maßtoleranz auf nunmehr ±10 µm zu reduzieren. Weil hier keine Grate und Risse mehr entstehen, werden Haftungsfehler auf ein Minimum reduziert, während sich die Positioniergenauigkeit verbessert (Bild 2).

- Chip-Widerstände schrumpfen weiter

- Weniger Befestigungsfehler dank Bodenelektrode