DTMF-Generierung

Umsetzung mit einer FPGA-Steuerung

Fortsetzung des Artikels von Teil 1

Ressourcenbedarf für das gewählte Design

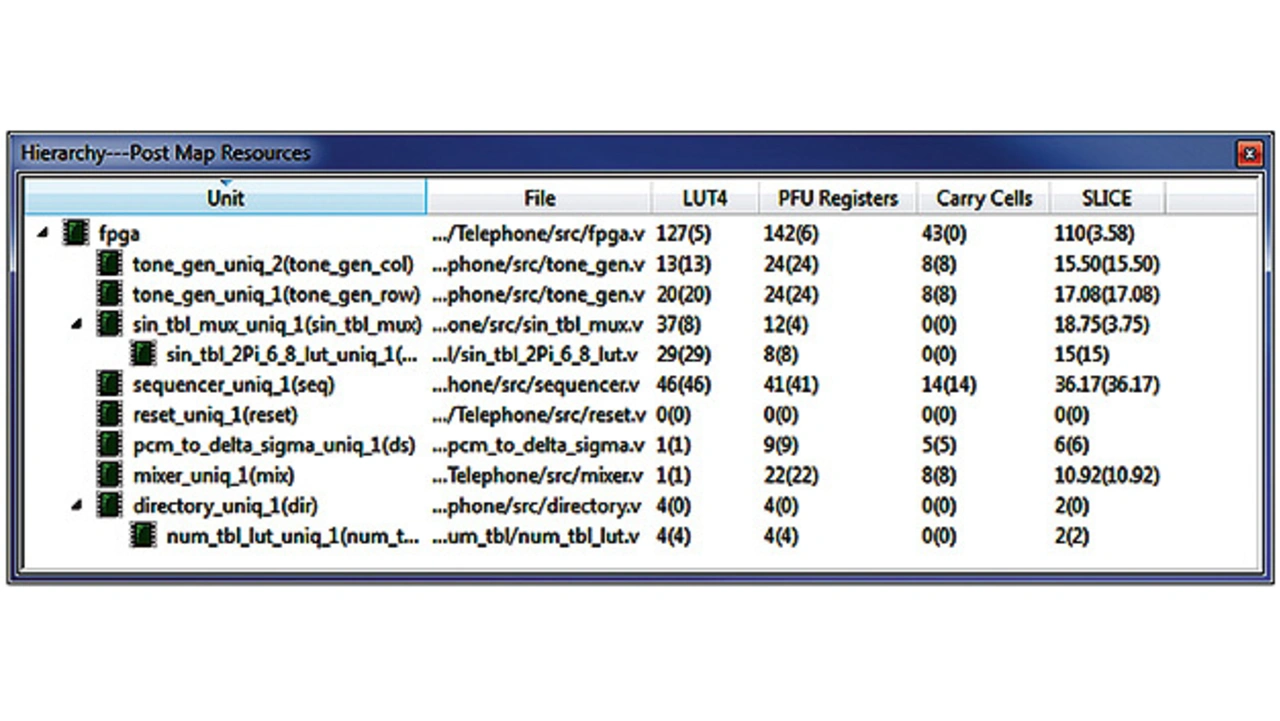

Alles in allem ist dies eine überschaubare Aufgabe: Fragt sich nur, wie viele Ressourcen man braucht, wie viele LUTs, RAMs und Multiplizierer, wie klein also das FPGA sein kann, in das die Logikschaltung hinein passt. Um die Antwort vorweg zu nehmen: Das kleinste FPGA der MachXO2-Familie von Lattice ist schon groß genug. Es hat zwar weder Multiplizierer noch RAM-Blöcke, zudem auch keine PLL und mit 256 Stück auch nicht gerade viele LUTs. Trotz alledem reichen die knappen Ressourcen aus.

Die LUTs der Bausteine der MachXO2-Familie von Lattice sind so konzipiert, dass sie auch als RAM oder ROM verwendet werden können. De facto bemerkt man gar keinen Unterschied, ob bei der Generierung eines ROM-Moduls mit der grafischen Bedienoberfläche „IPexpress“ Block-RAM oder LUTs verwendet werden. Um ein ROM der Größe 128 × 8 bit zu erzeugen, braucht man in einem Fall ein Bock-RAM und im anderen Fall eben 32 LUTs. Dank dieser Eigenschaft ist die Erzeugung der ROMs für die anzurufende Telefonnummer und für die Sinuswerte auch dann möglich, wenn das FPGA gar kein Block-RAM hat.

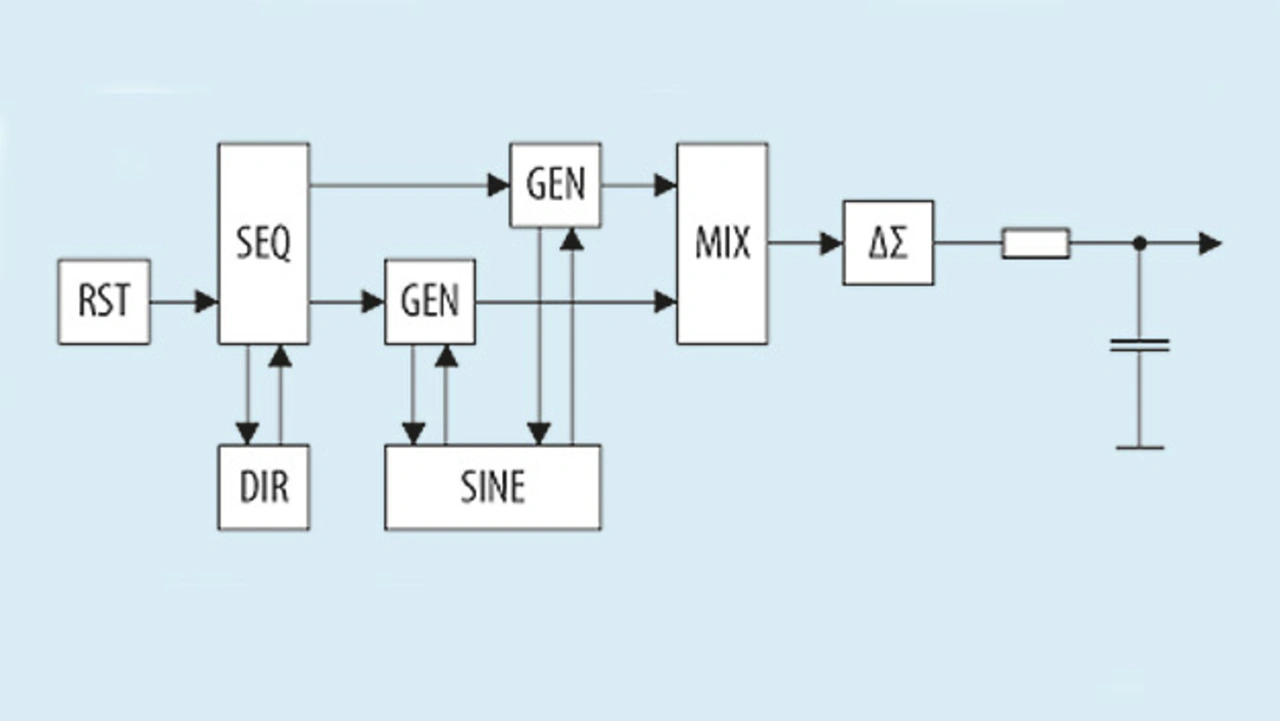

Das Blockschaltbild der Logik (Bild 1) ist relativ einfach: Der Sequencer wird durch ein externes Triggersignal aktiviert. Er liest die anzurufende Telefonnummer Ziffer für Ziffer aus dem Verzeichnis (DIR) und aktiviert die beiden Tongeneratoren. Diese beiden lesen mit unterschiedlicher Geschwindigkeit die Sinustabelle aus und geben die Werte an den Mischer, der die Werte unterschiedlich bewertet und addiert. Die Wandlung in analoge Spannungswerte erfolgt schließlich im Zusammenspiel von Delta-Sigma-Wandler und externen R/C-Filtern.

Jobangebote+ passend zum Thema

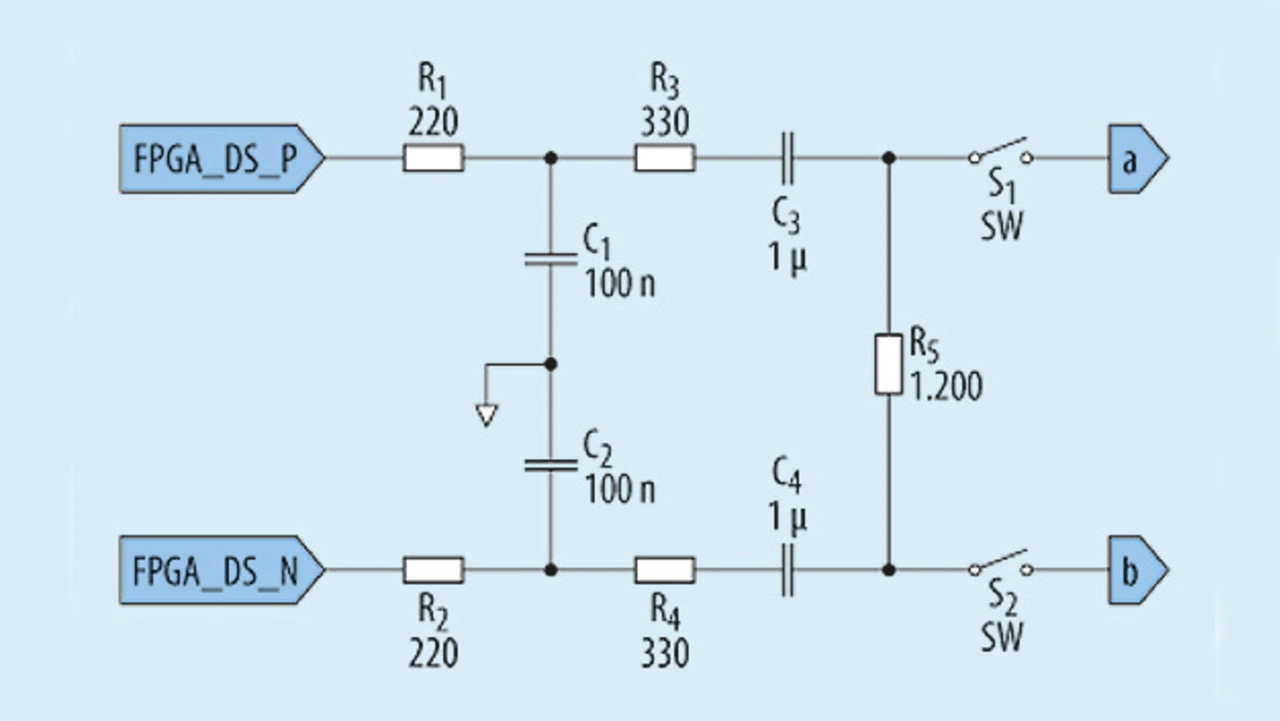

Die Dimensionierung von Widerstand und Kondensator folgt dabei der üblichen Methode, wonach man dafür eine Zeitkonstante (2πRC) von mindestens dem 1000-fachen der Periodendauer des Arbeitstakts wählt. In diesem Fall liegt die Dämpfung der Arbeitsfrequenz bei über 60 dB. Bei 12 MHz Arbeitstakt und der Berücksichtigung des maximalen Ausgangsstroms eines I/O-Pins von 16 mA wären das also z.B. 220 Ω und 100 nF (Bild 2). Zu guter Letzt wird mit einem zweiten Filter der Sendepegel angepasst, galvanisch entkoppelt und über zwei Relais an das a/b-Interface angelegt.

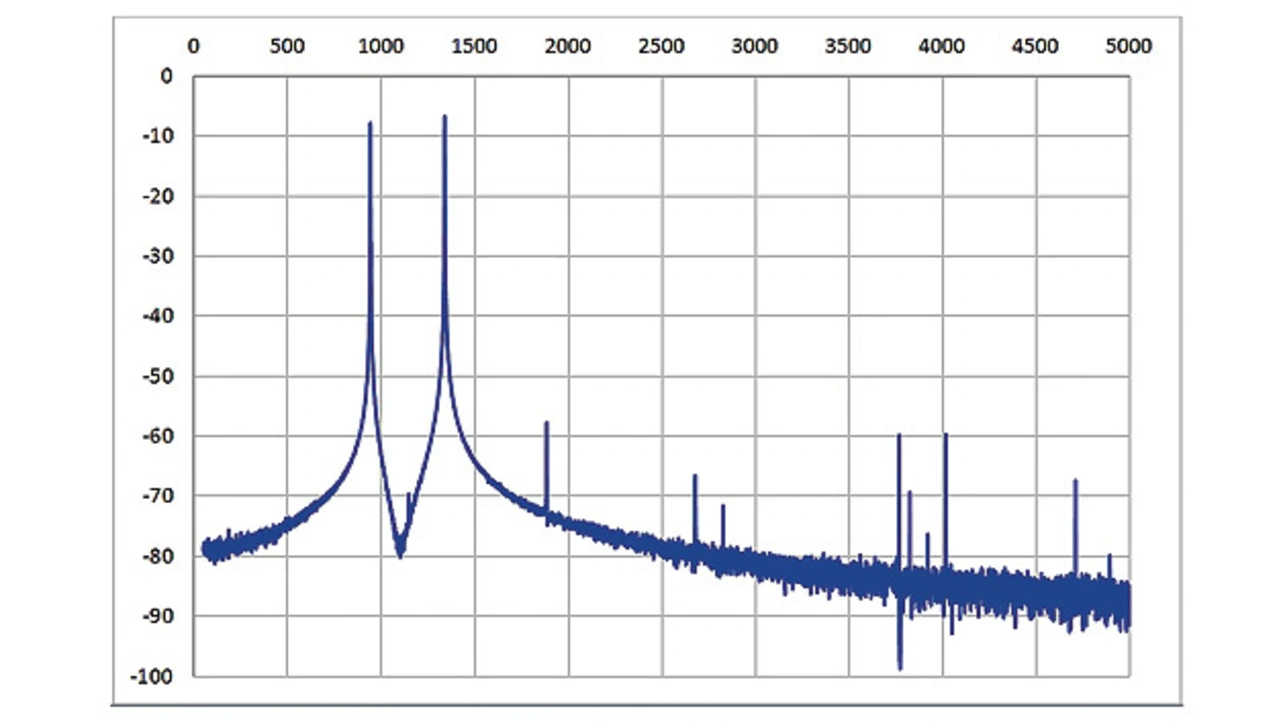

Soweit die Theorie: Die ganze Logikschaltung passt aber nur dann in ein kleines FPGA hinein, wenn man die Breite des Adressbusses und des Datenbusses der Sinustabelle sinnvoll wählt. Wie breit also muss der Zähler sein, mit dem man die X-Achse zwischen 0 und 2π auffächert? Und wie viele Bits muss man für die Werte benutzen? Die Simulation des parametrierbaren FPGA-Designs mit nachfolgender Fourier-Analyse zeigt, dass man bereits bei 6 bit für die Abszisse und 8 bit für die Ordinate ein ausreichend gutes Ausgangssignal erhält, dessen fehlerhafte Spektralanteile unter –50 dB bezogen auf das Nutzsignal liegen (siehe Bild 3); dies entspricht damit dem, was die Norm fordert.

Dank dieser schmalen Busbreiten passt die gesamte Logikschaltung in etwa 220 LUTs; und damit in ein FPGAs der MachXO2-Familie von Lattice. Dabei schlägt das ROM für die Sinustabelle mit 37 LUTs zu Buche, das für die Telefonnummer mit vier. Einen recht großen Anteil am gesamten Ressourcenverbrauch hat der Sequencer mit 46 LUTs, weil dort breite Zähler nötig sind, um die langen Ton- und Pausenzeiten abzuzählen (siehe Bild 4).

Implementierung basiert auf einem MachXO2-/-XO3-¬Evaluierungs-Kit

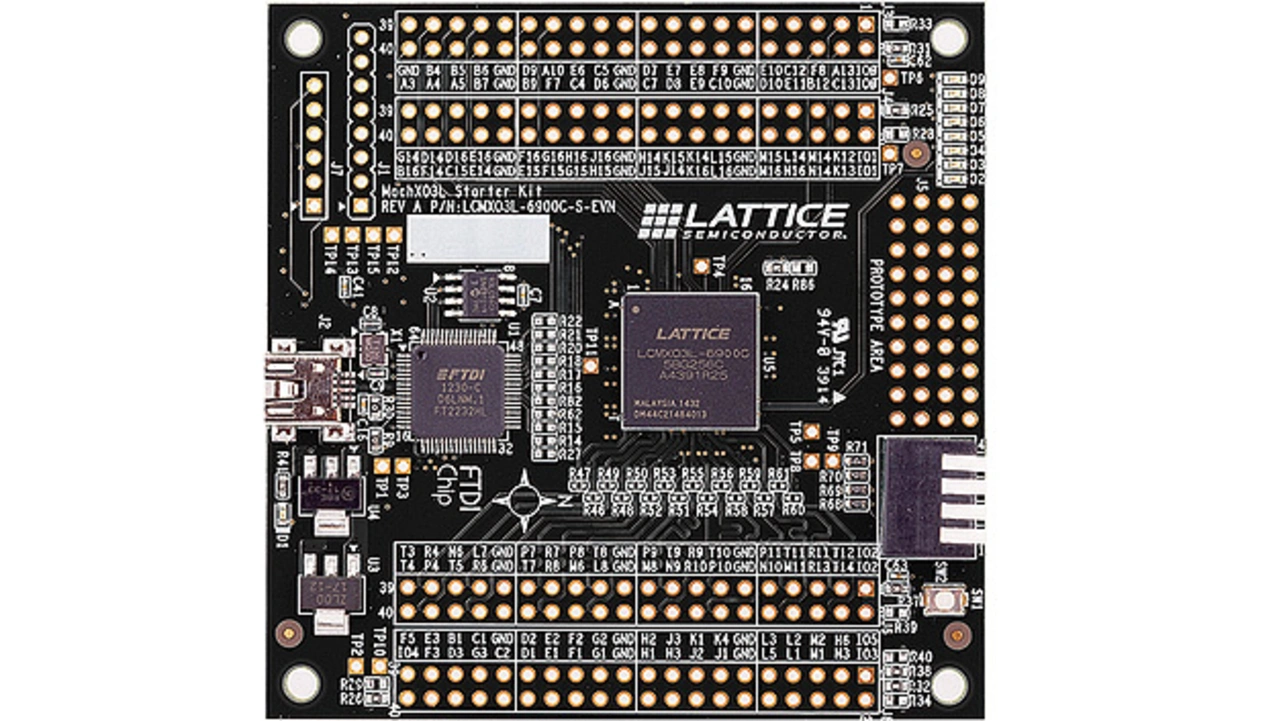

Für die reale Testimplementierung kann man fast jedes Evaluierungs-Board der MachXO2 oder MachXO3-Familie verwenden, denn die Bausteine dieser beiden Familien sind technologisch nahe verwandt. So kann man z.B. das kostengünstige MachXO3LF Starter Kit (Bild 5) verwenden, um die korrekte Funktion des Designs zu validieren. Das auf dem XO3LF Starter Kit verbaute FPGA ist mit 6900 LUTs zwar deutlich überdimensioniert, aber das Board ist sehr günstig, und es hat genügend Anschlussmöglichkeiten für die externe Beschaltung.

Die Taktversorgung des ¬FPGA erfolgt bei dieser Beispiel¬implementierung durch den 12-MHz-Takt des USB-Controllers. Die zwei R/C-Filter und die Pegelanpassung lassen sich leicht an nachträglich eingelötete Stiftleisten anschließen – ebenso das Anschlusskabel zur lokalen Telefonanlage. Anschließend muss noch das Design in das Flash des FPGAs programmiert werden – und los geht’s. Ruf an!

Der Autor

| Harald Flügel |

|---|

| hat von 1981 bis 1985 an der Hochschule für Technik in Karlsruhe Nachrichtentechnik studiert und danach knapp 25 Jahre lang in der Entwicklung von Embedded-Systemen gearbeitet, auch wenn diese noch nicht so hießen. Seit 2008 ist er mit unterschiedlichen Aufgaben, die stets mit Programmierbarer Logik zu tun haben, beim Distributor Arrow tätig; derzeit als Spezialized Field Application Engineer für die Produkte des Herstellers Lattice. Aus seiner Feder stammt auch das Buch „FPGA-Design mit Verilog“. |

hfluegel@arroweurope.com

- Umsetzung mit einer FPGA-Steuerung

- Ressourcenbedarf für das gewählte Design