Funkkommunikation

HF-Layout der Leiterplatte optimieren

Fortsetzung des Artikels von Teil 1

Wenn Referenzdesigns nicht passen

Anbieter von Funk-SoCs bieten Referenzdesigns an, die so bemessen sind, dass sie bestmögliche Funkleistung bieten. Aufgrund von Beschränkungen wie Größe oder Formfaktor ist es aber nicht immer möglich, dieses Design eins zu eins für ein Endsystem umzusetzen. Jede Abweichung vom Referenzdesign kann die Leistungsfähigkeit beeinträchtigen. Bei hohen Frequenzen können Änderungen bei den Abständen zwischen den Bauteilen die parasitären Induktivitäten verändern, da die Leiterbahnen verschieden lang sind. Eine andere Substratdicke oder dielektrische Konstante oder Spalten zwischen den Leiterbahnen können die parasitären Kapazitäten verändern. Wird der Abstand oder die Ausrichtung von Bauteilen, die in Bezug zueinander stehen, verändert, kann dies die Signalkopplung beeinflussen. Die Änderung ganzer Bauelemente oder Bausteingrößen von den empfohlenen Werten kann ebenfalls verschiedene parasitäre Effekte mit sich bringen.

Eine schlechte Designentscheidung kann das Anpassungs- und Filternetzwerk verstimmen und auch die Last des Quarzes verändern. Die mögliche Folge ist dann eine reduzierte Ausgangsleistung (Tx), eine verringerte Empfangsempfindlichkeit (Rx), eine Zunahme der Störemissionen, eine erhöhte Stromaufnahme und möglicherweise ein Frequenzversatz (Offset) zwischen verschiedenen Leiterplatten. All dies macht sich bei Messungen leitungsgebundener und abgestrahlter Signale bemerkbar.

Mögliche Probleme sind nicht allein auf den HF-Teil des Schaltkreises beschränkt. Aus Sicht der HF-Strahlung ist das gesamte Leiterplattendesign zu berücksichtigen, da die Masse-Ebene und deren Größe die Leistung des gesendeten Signals beeinflusst – vor allem wenn eine Monopol-Antenne zum Einsatz kommt. Die abschirmende Wirkung der Masse-Ebene beeinflusst auch den Grad der abgestrahlten Störungen genauso wie nicht-HF-bezogene Leitungen. Dabei muss sichergestellt sein, dass die Störungen innerhalb der EMV-Grenzwerte verbleiben. Ebenfalls zu berücksichtigen ist, dass selbst eine Eins-zu-eins-Umsetzung eines Referenzdesigns keine vollständige Anwendung darstellt. Dazu sind auch die anderen Schaltkreise auf dem Board zu beachten, die sich außerhalb des Referenzdesigns befinden.

Layout-Tipps für den HF-Teil

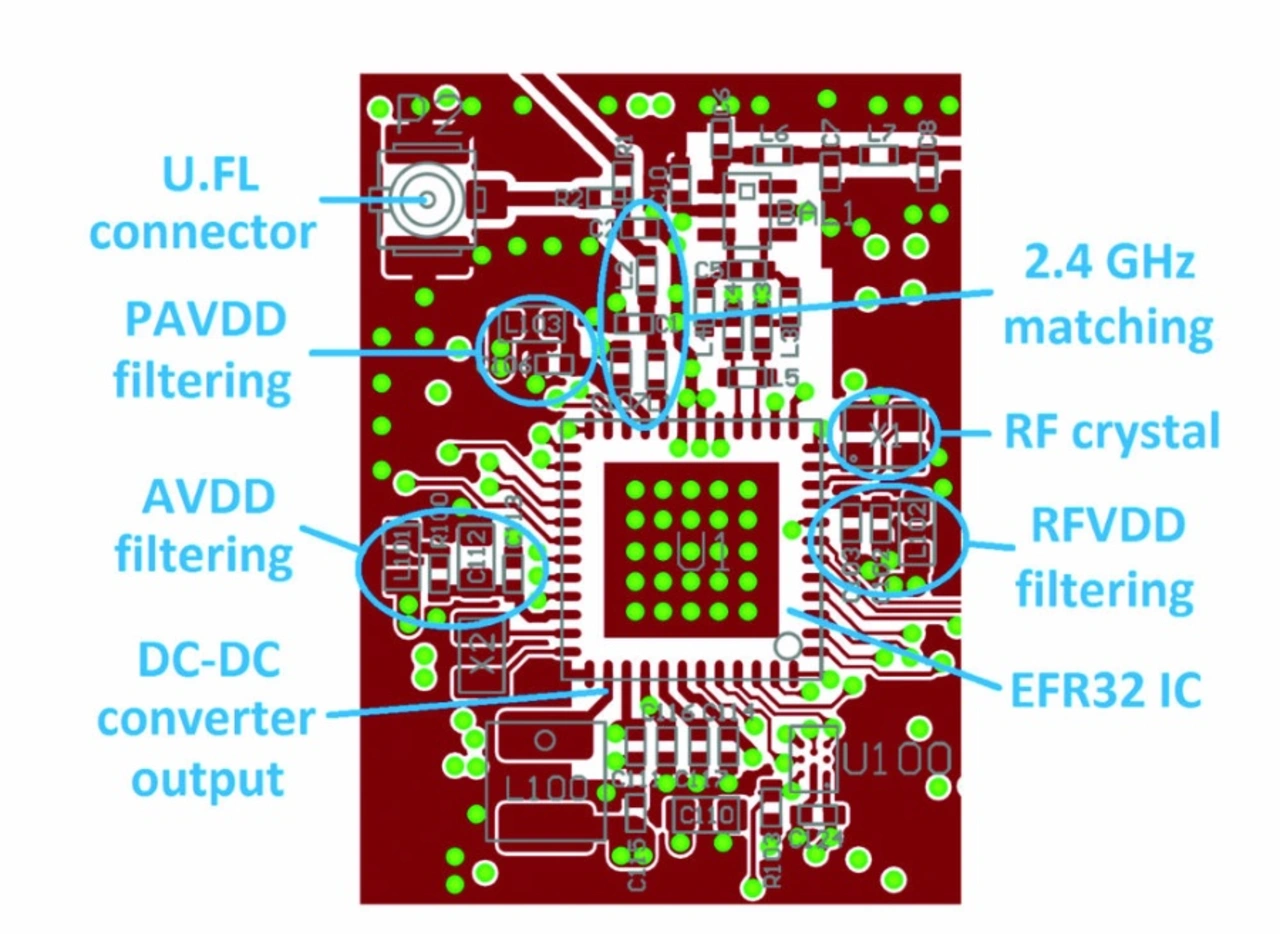

Ist es nicht möglich, ein Referenzdesign eins zu eins umzusetzen, sollten die folgenden Richtlinien beachtet werden. Bild 2 beschreibt beispielhafte Richtlinien für das Layout einer 2,4-GHz-Funkplatine.

Beginnend mit dem Anpassungsnetzwerk sollte das erste Bauteil so nah wie möglich am Tx-Ausgangspin des HF-ICs platziert werden, um ein Verstimmen aufgrund parasitärer Induktivitäten längerer Signalleiter zu verringern. Die verbleibenden Komponenten für das Anpassungsnetzwerk sollten nahe beieinander angeordnet sein, um die parasitäre Kapazität der Leiterplatte gegen Masse oder zusätzliche parasitäre Induktivitäten zwischen Bauteilen zu minimieren. Die Leiterbahnbreite zur Verbindung dieser Bauteile sollte genauso breit sein wie die Pads. Damit sind 0,5 mm für SMD-Bauteile der Größe 0402 ausreichend.

Die richtige Platzierung der Entkopplungskondensatoren an allen Versorgungspins ist entscheidend. Die Ableitungskondensatoren mit den niedrigsten Kapazitätswerten filtern Signale rund um die fundamentalen Tx/Rx-Frequenzen heraus und sind möglichst nah an den IC-Pins zu platzieren – mit guter Erdung mittels mehrerer Durchkontaktierungen (Vias) zur Massefläche. Ableitungskondensatoren mit Werten um die 100 nF unterdrücken Taktsignale im zweistelligen MHz-Bereich, die sonst innerhalb des ICs verstärkt werden und unerwünschte Störungen rund um die Trägerfrequenz verursachen. Die Kondensatoren mit den höchsten Kapazitäten filtern Störungen der Schaltnetzteile, die bei einigen hundert Kilohertz liegen. Diese lassen sich weiter entfernt von den Versorgungspins platzieren, bei einem batteriebetriebenen Gerät sind sie hinfällig.

Der Quarz sollte so nah wie möglich am HF-IC platziert werden, um sicher zu sein, dass parasitäre Via-Kapazitäten minimal ausfallen und sich der Frequenzoffset verringert. Das Gehäuse des Quarzes sollte über mehrere Vias mit Masse verbunden sein, um eine Strahlung von ungeerdeten Teilen zu vermeiden. Jegliches Metall, das elektrisch nicht verbunden und somit elektrisch »schwebt«, kann eine unerwünschte Strahlungsquelle sein. Mit einer isolierenden Metallunterlage zwischen dem Quarz und den Leiterbahnen mit der Versorgungsspannung VDD lässt es sich vermeiden, dass die Stromversorgung den Quarz verstimmt. Zugleich wird damit unterbunden, dass das Quarz- und das Taktsignal sowie deren Harmonische in die Versorgungsleitungen einkoppeln.

- HF-Layout der Leiterplatte optimieren

- Wenn Referenzdesigns nicht passen

- Layout-Tipps für die Masse-Anbindung