Systemdesign / 5G-Entwicklung

Verifikation unter dem 5G-Dreieck

Fortsetzung des Artikels von Teil 1

Beispiele

Der erste Trend, die Minimierung der Verlustleistungsaufnahme, ist in allen Bereichen des 5G-Netzwerks eine Herausforderung. Aus der Chip-Entwicklungsperspektive ist es wichtig mit dem dynamischen Stromumsatz im Kontext von Software umgehen zu können. Weiterhin muss das Schalten von Power-Domains innerhalb eines Chips auf Basis von Standardbeschreibungen effizient analysier-, optimier- und verifizierbar sein (basierend auf dem IEEE 1801-Standard-Format UPF).

Die heutigen Chip-Verifizierungstools wie Xcelium-Simulation und Palladium Z1-Emulation von Cadence unterstützen das IEEE 1801 UPF-Format. Damit werden jene Effekte, die das Abschalten bestimmter Power-Domains – von denen große SoCs heutzutage einige Hunderte tragen - frühzeitig simuliert.

Die aktuellen Aktivitäten in der IEEE 1801-Standardisierung erstrecken sich tatsächlich bis auf die Systemebene. Dadurch wird eine Spezifikation der Stromzustände innerhalb der Chipblöcke und ihrer Steuerung möglich.

Dies ist für die Entwicklung von "Dark Silicon", bei dem ein Chip fast komplett abgeschaltet wird, wichtig; aktiv bleiben dabei ein kleiner Mikrocontroller und ein Low-Power-Betriebssystem, die nach bestimmten Eingangssignalen den Chip schnell in den Arbeitsmodus schalten können, zum Beispiel basierend auf ankommenden Verkehr.

Für den dynamischen Stromumsatz können Chip-Verifikationstools wie Simulation und Emulation tatsächlich mit den Implementierungstools verbunden werden. Funktionale Aktivitätsdaten des Chips, die aus der Emulation abgeleitet sind, können mit Bibliotheksinformationen kombiniert werden. Das stellt die Verlustleistung der Chip-Implementierung akkurat dar.

Dies ergibt eine ziemlich genaue frühzeitige Darstellung des Stromumsatzes für einzelne Chips und Chips in Systemumgebungen. Die Genauigkeit ist besonders hoch, wenn die Aktivität von der echten Software abgeleitet wird – dazu ist die geforderte Emulationsgeschwindigkeit sowie der aus der Simulation abgeleitete Netzwerkverkehr, nötig. Mit diesen Techniken geschieht die Analyse innerhalb eines Projektes tatsächlich früh genug, um noch Änderungen zur Optimierung zuzulassen.

Bezüglich der Verifikation vom „System der Systeme“, dem zweiten Trend, ist der Einsatz eines Arrays von miteinander verbundenen Verifizierungswerkzeugen, wie Emulatoren zur Verifikation eines kompletten Netzwerks von Endknoten über Basisstationen, Routern bis hin zur Cloud zwar sehr faszinierend, aber nicht praktisch umzusetzen. Ein Problem ist dabei alle Komponenten zur richtigen Zeit für die Emulation bereit zu haben. Einige Komponenten werden bereits in Silizium verfügbar sein, einige noch konzeptionell, andere können als RTL zur Emulation zur Verfügung stehen. Die Branche hat mit verschiedenen Ansätzen für dieses Szenario experimentiert, unter anderem mit reinen virtuellen Modellen, virtuellen Modellen die an FPGA-Prototypen oder Emulation angeschlossen sind, Netzwerken von Hardware-Prototypen, bis hin zu einer Kombination aus allen genannten.

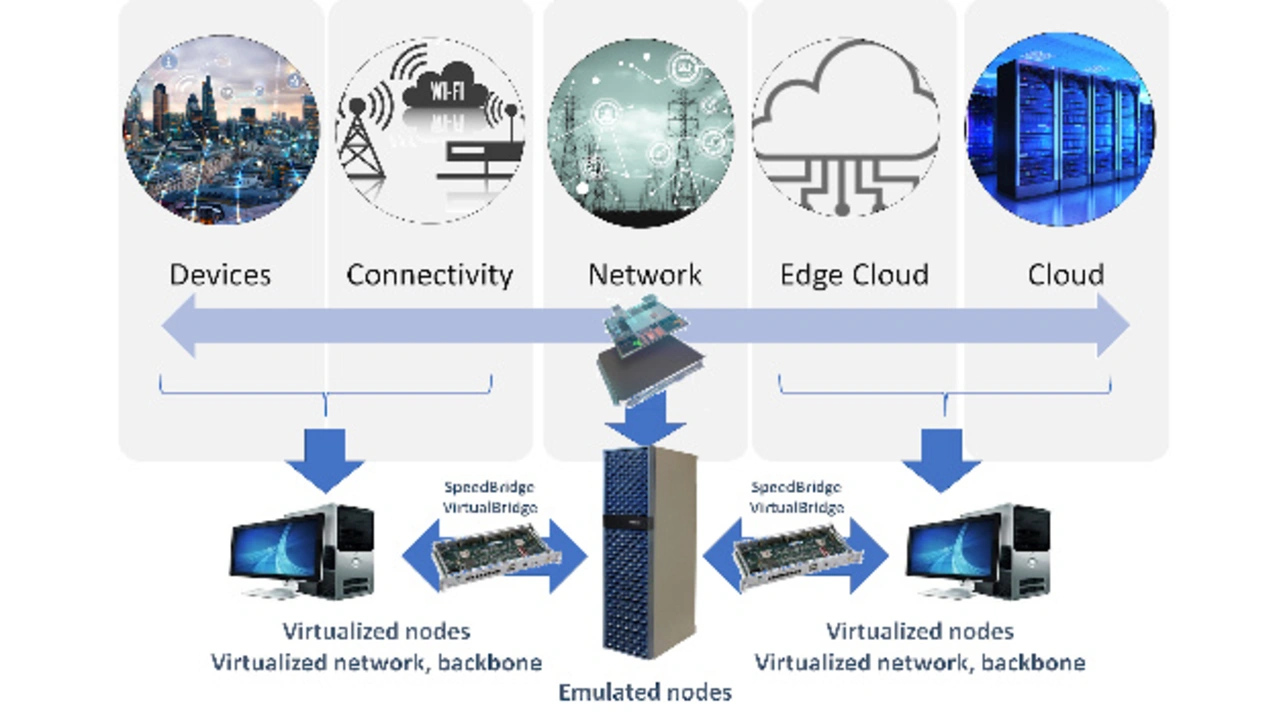

Daher ist eine vollständig ausführbare Spezifikation des Netzwerks ebenso wünschenswert wie unrealistisch. Die Alternative ist die richtige Aufteilung des Systems in Teilsysteme, sowie die Abstraktion einiger Aspekte, die sich nicht direkt auf die entwickelte Komponente auswirken. Bild 3 zeigt die gängige Electronic-Design-Automation-Praxis; mehrere Knoten eines Systems werden auf verschiedenen Abstraktionsebenen kombiniert, sowohl mit realen als auch virtuellen Knoten. Dies ist eine natürliche Erweiterung dessen, was in der Industrie schon als hybride Emulation bekannt ist.

Jobangebote+ passend zum Thema

Im obigen Beispiel in Bild 3 werden einige Systemknoten emuliert, die über Adapter verbunden sind; einige der Knoten werden dabei virtualisiert und laufen als Software auf einem Host. Diese Umgebung mit gemischter Abstraktion ermöglicht die Verifikation und Validierung der zu emulierenden Komponenten. Einige unserer Kunden integrieren sogar bereits mehrere Chips in unserem Emulator. Eine der Herausforderungen dabei ist die Darstellung der Analog/Mixed-Signal-Schnittstellen.

Der dritte Trend – die systemweite Architekturanalyse und Validierung der Performanz kann mit einem ähnlichen Setup wie in Bild 3 erreicht werden. Netzwerktester und Traffic Generatoren – zum Beispiel von Keysight Ixia oder Rohde & Schwarz – können an Palladium Z1 Emulation und Protium S1 Prototypen angeschlossen werden. Damit kann der in der Entwicklung stehende Chip mit realen Eckfällen, wie Sie in einem Netzwerk passieren würden, geprüft werden. Genaue Performanz-Informationen lassen sich ableiten; damit wird das System derart optimiert, dass Schlüsselmerkmale wie die geforderte Latenz, erreicht werden. Neue Technologien und Standards zur Erstellung von sogenannten „Portablen Stimuli“ werden derzeit in der Accellera Portable Stimulus Gruppe diskutiert und haben das Ziel, basierend auf abstrakten Szenarien wiederverwendbare Tests in C automatisch zu erzeugen. Dies ist ein spannendes Marktsegement, in dem EDA, Test und System-Modellierung derzeit enger zusammenwachsen.

Ausblick

Die Herausforderungen bei der Verifikation von Systemen der 5G-Komplexität sind so breit gefächert, dass kein Unternehmen in der Lage ist, alle gleichzeitig abzudecken. Industrien die 5G-Entwicklungen ermöglichen, verändern sich selbst. Sie begegnen diesen Herausforderungen und bilden Ökosysteme für 5G, welche die Fähigkeiten der EDA, des Tests, der System-Modellierung für Software und Halbleiter-IP kombinieren. Gute Beispiele dafür sind die Partnerschaften von Cadence mit Unternehmen wie National Instruments, um Pre-Silicon-Verifikation und Post-Silicon-Tests verbinden, sowie mit Keysight Ixia, um 5G-Testgeräte an EDA-Verifikations-Angebote wie Simulation, Emulation, und Prototyping anzubinden. (ct)

- Verifikation unter dem 5G-Dreieck

- Beispiele