Test- und Debug-Strategien

Fehleranalyse in PCIe-6.0-Designs

Bei der mit Spannung erwarteten nächsten PCIe-Generation kommt es darauf an, Bitfehlerratenmessungen zu verstehen.

Von Hiroshi Goto, Anritsu

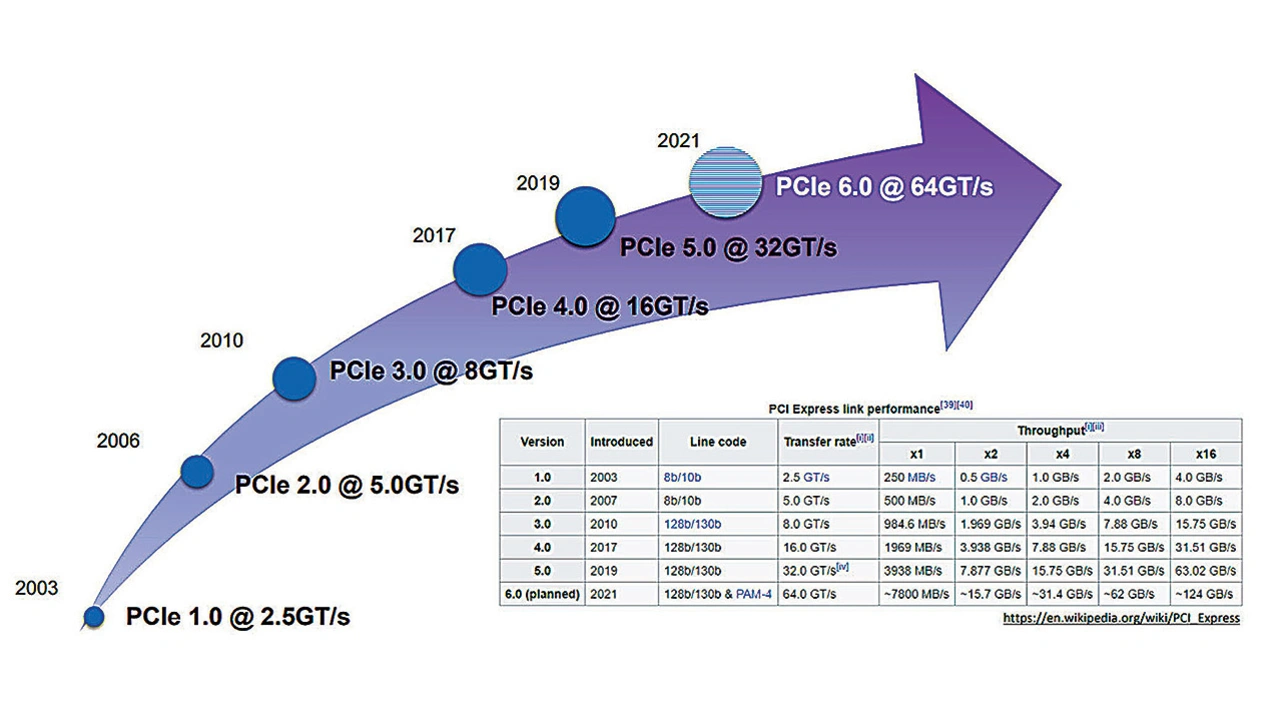

PCI Express (PCIe) 6.0 wird entwickelt, um den wachsenden Anforderungen an eine schnelle Datenübertragung in neuen Anwendungen gerecht zu werden, insbesondere in Rechenzentren, die 5G unterstützen. Es bietet eine Verdoppelung der Datenraten und andere verbesserte Leistungsmerkmale, allerdings auf Kosten zusätzlicher Komplexität beim Design der superschnellen Übertragungskomponenten (Bild 1). Entwickler in diesem Bereich müssen deren Leistungsfähigkeit mittels Echtzeitanalyse überprüfen - ein Ansatz, der Zeit spart und die Wiederholbarkeit verbessert.

Jobangebote+ passend zum Thema

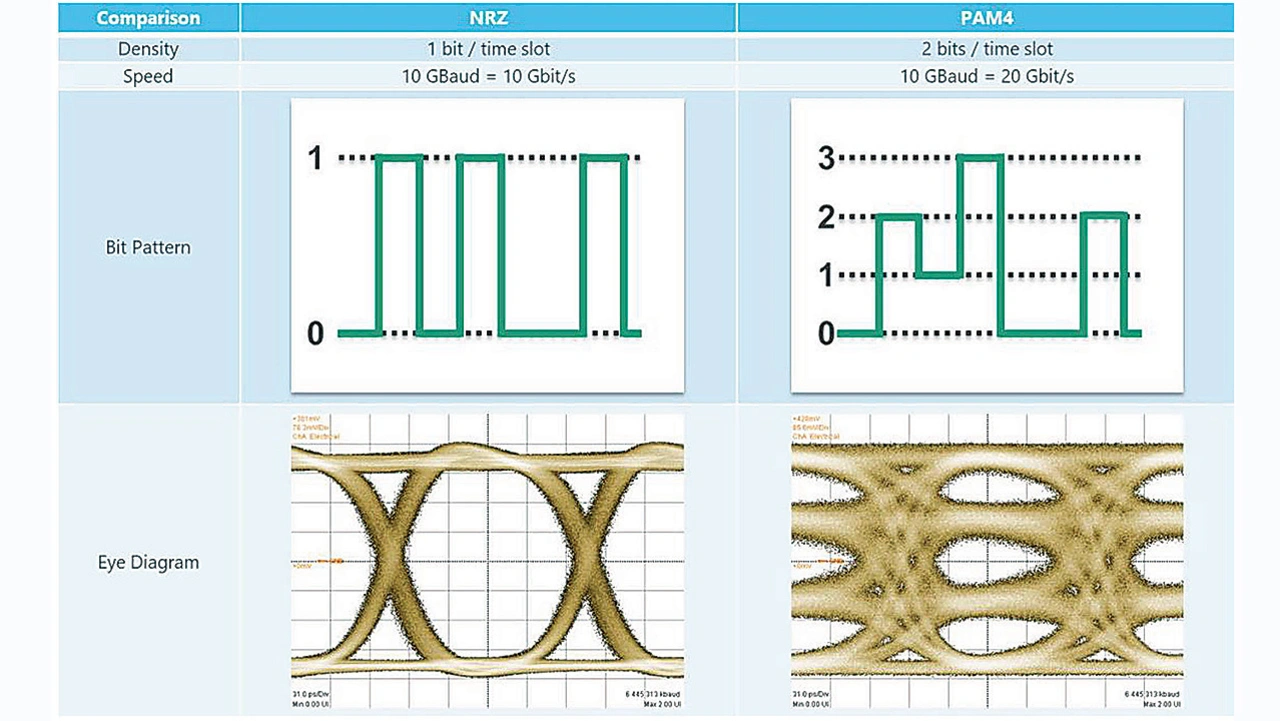

Um schnellere Technologien zu ermöglichen, nutzt PCIe 6.0 die 32-GBaud-PAM4-Signalisierung (Pulse Amplitude Modulation). Bei der PAM4-Modulation werden zwei Bits zu einem Symbol mit vier Amplitudenstufen kombiniert. Dadurch verdoppelt sich die Datenrate eines Netzwerks im Vergleich zur binären 1/0-High-Low-Signalisierung. Alle früheren Generationen (1 bis 5) der PCIe-Spezifikation verwenden die binäre »Non-Return-to-Zero«(NRZ)-Signalisierung.

Mit PAM4 bleibt die Kanalreichweite der Spezifikation ähnlich der PCIe-5.0-Spezifikation. Wie bei allen früheren PCIe-Generationen ist PCIe 6.0 vollständig abwärtskompatibel, sodass auch NRZ unterstützt wird. Während einerseits PAM4 die Übertragungsgeschwindigkeit verdoppelt, reduziert dieser Ansatz andererseits die Bandbreite pro Bit und verschlechtert das Signal-zu-Rausch-Verhältnis, wodurch ein kleineres Auge entsteht (Bild 2).

Mit anderen Worten: Die zusätzlichen Signalzustände von PAM4-Signalen machen diese fehleranfälliger als NRZ-Signale. Die zugrundeliegende Frequenz ist mit 32 GT/s NRZ die gleiche wie in der PCIe-5.0-Spezifikation, aber für den PAM4-Modus in PCIe 6.0 sind aufwendigere Schaltungen und Logiken erforderlich. Dieses ist notwendig, um die vier Symbolzustände zu verfolgen, aber auch für die Realisierung des erstmals eingesetzten Flow-Control-Unit(FLIT)-Modus.

Die FLIT-Codierung findet auf logischer Ebene statt, um Daten in Pakete fester Größe aufzuteilen. Kurz gesagt, ist ein FLIT eine logische Informationseinheit. Ein Netzwerkpaket besteht aus FLITs. Das erste FLIT eines Pakets ist das Header-FLIT und enthält Informationen über die Zieladresse des Pakets. Nachfolgende Body-FLITs enthalten die eigentliche Datennutzlast, und das letzte, das Tail-FLIT, dient der Buchführung, um die Verbindung zwischen den beiden Knoten zu schließen.

Frühere Versionen der PCIe-Spezifikation sahen keine Anwendung von FEC (Forward Error Correction) vor. Die Definition der logischen Schicht in Paketen fester Größe ermöglicht es PCIe 6.0 jedoch, FEC und andere Fehlerkorrekturmethoden einzubinden, da diese Methoden Pakete fester Größe erfordern. Sobald die Verbindung im FLIT-Modus arbeitet, muss jede Geschwindigkeitsänderung zu niedrigeren Datenraten auch denselben FLIT-Modus verwenden. Der kleine Overhead ermöglicht eine hohe Bandbreiteneffizienz und kurze Latenzzeiten.

Bei der PAM4-Signalisierung kommt es zu weniger Kanalverlusten, da sie im Vergleich zur 1/0-Signalisierung mit der halben Frequenz und zwei Bits pro Einheitsintervall (UI) arbeitet. Ein Nebeneffekt ist jedoch eine Verringerung des SNR um 10 dB. Das Ergebnis ist eine geringere Höhe und Breite der drei Augen. Folglich ist die Bitfehlerrate (BER) bei PAM4 verglichen mit NRZ um mehrere Größenordnungen höher. Bei PCIe 6.0 ist die BER eine Kombination aus der First Bit Error Rate (FBER), der Korrelation der Fehler in einer Leitung und der Korrelation der Fehler über alle Leitungen hinweg. FBER ist die Wahrscheinlichkeit, dass der erste Bitfehler an einem Empfänger in einem Link auftritt. Die Standardorganisation legte für PCIe 6.0 eine FBER von 10–6 fest. Bei PCIe 6.0 wird ein einzigartiger Ansatz verwendet, um die Latenzzeit für Hochgeschwindigkeitsanwendungen niedrig zu halten. Es integriert eine niedrigere FBER mit einer latenzarmen Forward Error Correction (FEC) für die Anfangskorrektur. FEC ist eine fortschrittliche Codierungstechnik, die die notwendigen Daten zur Fehlerkorrektur über die PAM4-Verbindung überträgt. Sie dient als Schlüsseltechnologie, um die erforderliche Übertragungsqualität sicherzustellen. Sie ist wegen der durch PAM4 verursachten Verringerung des SNR ein wesentliches Element beim Testen.

Nach der FEC erkennt eine zyklische Redundanzprüfung (CRC) alle verbleibenden Fehler. Das Ergebnis ist ein Link-Level-Retry-Mechanismus, der sicherstellt, dass PCIe 6.0 die Anforderungen an niedrige Latenz, hohe Bandbreite und hohe Zuverlässigkeit erfüllt.

Die PCI-SIG hat für PCIe 6.0 eine FEC mit niedriger Latenzzeit von unter 2 ns festgelegt – als Teil der spezifizierten Gesamtsignallatenz von weniger als 10 ns. FEC basiert auf einer festen Anzahl von Symbolen. Daher ist es einfach, zu FLITs überzugehen, da diese ebenfalls eine feste Größe haben.

Performance-Tests

Für die Bewertung der Performance ist die Festlegung eines Schwellwerts für FEC-Symbol-Fehler ein empfohlener Ansatz. Das gibt den Technikern eine umfassendere Kontrolle über die Fehlerbedingungen, die sich auf das Pattern während der Erfassung auswirken. Unbedeutende Ereignisse unterhalb des Schwellwerts werden ignoriert, da diese normalerweise in der FEC-Umgebung korrigiert werden.

Um einen Schwellenwert festzulegen, erzeugt ein BER-Tester (BERT) ein PAM4-Signal für den Empfängereingang des zu prüfenden Geräts (DUT). Der Prüfling bestimmt den logischen Zustand des Eingangssignals und leitet seine Entscheidung in einer Schleife an den Senderausgang weiter. Der Fehlerdetektor (ED) eines BERT ermittelt, ob die Entscheidung des Prüflings korrekt war. Dabei müssen die Jitter- und Rauschprofile des BERT den Standardnormen entsprechen. Zur Durchführung der FEC-Symbol-Fehlermessungen sollte das verwendete BERT-System über einen hochempfindlichen 116-Gbit/s-PAM4-Fehlerdetektor verfügen.

Bei der Durchführung des Tests ist zu beachten, dass ein Zufallsfehler nicht so aussagekräftig ist wie ein Fehler, der in einem Burst auftritt. Ebenfalls wichtig: Einige Burst- Fehler können ab einer bestimmten Grenze nicht mehr durch FEC korrigiert werden. Über diese Grenze hinaus muss eine Nachbearbeitung stattfinden, um festzustellen, warum der Prüfling ein ankommendes Symbol falsch interpretiert. Mit diesem Ansatz können Techniker ein Gerät anhand standardmäßiger PRBS-Muster (Pseudo-Random Binary Sequence) bewerten und gleichzeitig die Fehlererkennung auf Ereignisse stützen, die in einer FEC-Umgebung problematisch sein könnten.

Werden die Eingangsdaten erfasst, sobald die Anzahl der FEC-Symbolfehler den eingestellten Schwellenwert überschreitet, sollte eine FEC-Symbol-Erfassungsmessung erfolgen. So kann festgestellt werden, welcher Datenstrom die un- korrigierbaren Fehler verursacht. Ein nicht korrigierbarer Burst-Fehler ist definiert als die Anzahl von mehr als 16 Reed-Solomon(RS)-FEC-Symbolfehlern pro Codewort.

Der Autor

Hiroshi Goto ist Senior Architect bei Anritsu in den USA.