Messtechnik wird zum Erfolgsfaktor

Anforderungen und Designregeln für PCIe-5.0-Systeme

PCIe ist nach wie vor der bevorzugte Bus für den Anschluss von Peripheriegeräten an moderne Server und Computer. Die neueste Version PCIe 5.0 erhöht Datenraten deutlich – und stellt Entwickler vor neue Test- und Designanforderungen. Ein Blick "hinter die Kulissen" von PCIe 5.0.

PCIe 5.0 ist die fünfte Version der PCIe-Spezifikation (Peripheral Component Interconnect Express), dem gängigsten Verbindungsstandard für den Anschluss von Peripheriegeräten an Server und Computer. Die PCIe-Standards gewährleisten, dass Motherboards, Grafikkarten, Ethernet-Karten, WLAN-Karten, Speicherträger und andere Peripheriegeräte verschiedener Hersteller nahtlos miteinander kompatibel sind, wenn sie in einen Server oder Computer integriert werden.

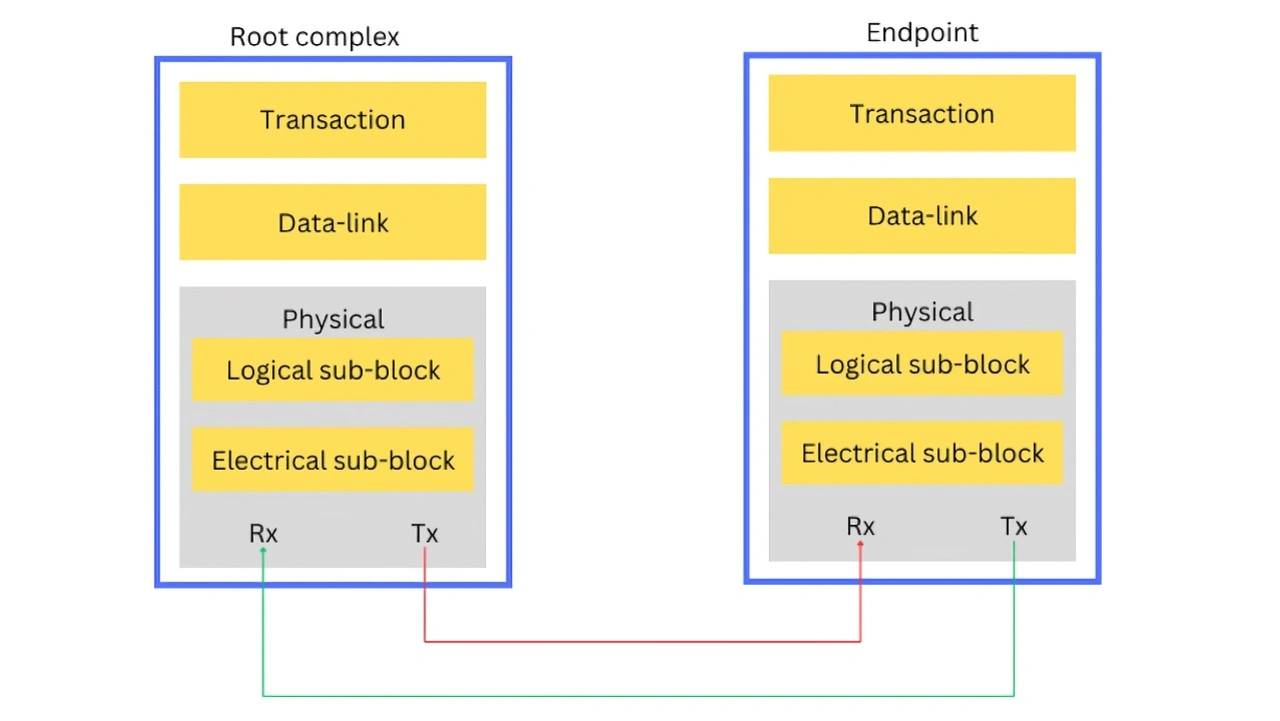

Die logischen Unterblöcke, aus denen sich die PCIe 5.0-Standards zusammensetzen, sind in Bild 1 dargestellt. In Bezug auf die Datenübertragung ist PCIe 5.0 eine serielle Schnittstelle, die aus mehreren parallelen Lanes besteht. Jede Lane überträgt Daten seriell bitweise. Alle Lanes senden und empfangen jedoch gleichzeitig, um den Nettodurchsatz zu erhöhen, und verhalten sich dabei ähnlich wie ein paralleler Bus.

Potenzielle Anwendungsfälle für PCIe 5.0

Künstliche Intelligenz wird ein wichtiger Anwendungsbereich für PCIe 5 [1] und höher sein. Insbesondere große generative KI-Modelle (im Bereich von 20 Milliarden bis über 500 Milliarden Parametern) erfordern, dass Daten aus den Systemspeicherkomponenten oder dem Arbeitsspeicher mit maximaler Kapazität und Geschwindigkeit über den Interconnect-Bus an KI-Beschleunigerkarten übertragen werden. KI-Beschleuniger für Server und den privaten Gebrauch profitieren enorm von den hohen Bandbreiten der Generation 5.

Jobangebote+ passend zum Thema

Daneben ist PCIe 5.0 ein zentraler Bestandteil in Hyperscale-Rechenzentren, die moderne KI-, Big-Data- und Hochleistungsrechneranwendungen unterstützen. PCI Express 5 ermöglicht schnellere Technologien, wie zum Beispiel:

- Ethernet der nächsten Generation: PCIe 5 ermöglicht Netzwerkkarten und Switches in Rechenzentren mit 400-Gigabit-Ethernet (400GE).

- Hochgeschwindigkeits-Speicher: Enterprise-Speichertechnologien wie NVMe-SSDs (Non-Volatile Memory Express Solid State Storage Drives) über Glasfaserkanäle basieren auf PCIe 5. Speichercontrollerkarten und Chipsätze, die verschiedene Speichermodule mit Motherboards und Prozessoren verbinden, basieren auf PCIe und profitieren von der Geschwindigkeit von PCIe 5. Zu diesen Speichertechnologien gehören SAS (Serial Attached Small Computer System Interface) und SATA (Serial Advanced Technology Attachment).

- Beschleunigerkarten: Moderne Beschleunigerkarten wie Grafikprozessoren (GPUs) und Tensorprozessoren (TPUs) für KI- oder Grafik-Workloads profitieren von PCIe 5 und höheren Standards.

Gamer, professionelle Grafiker und Videobearbeiter profitieren von den hohen Datenübertragungsgeschwindigkeiten von PCIe 5 zwischen Grafikkarten (wie den Nvidia GeForce RTX-GPUs) und dem Systemspeicher durch direkten Speicherzugriff.

Darüber hinaus wird die Systemleistung durch PCIe Gen 5 SSD- und M.2 NVMe-Controller gesteigert, die dafür sorgen, dass der Speicher bei der Arbeit mit modernen Hochleistungs-CPUs (Central Processing Units) und den neuesten DDR5-Systemspeichern (Double Data Rate) weniger zu einem Engpass wird.

Die wichtigsten Leistungsverbesserungen von PCIe 5.0

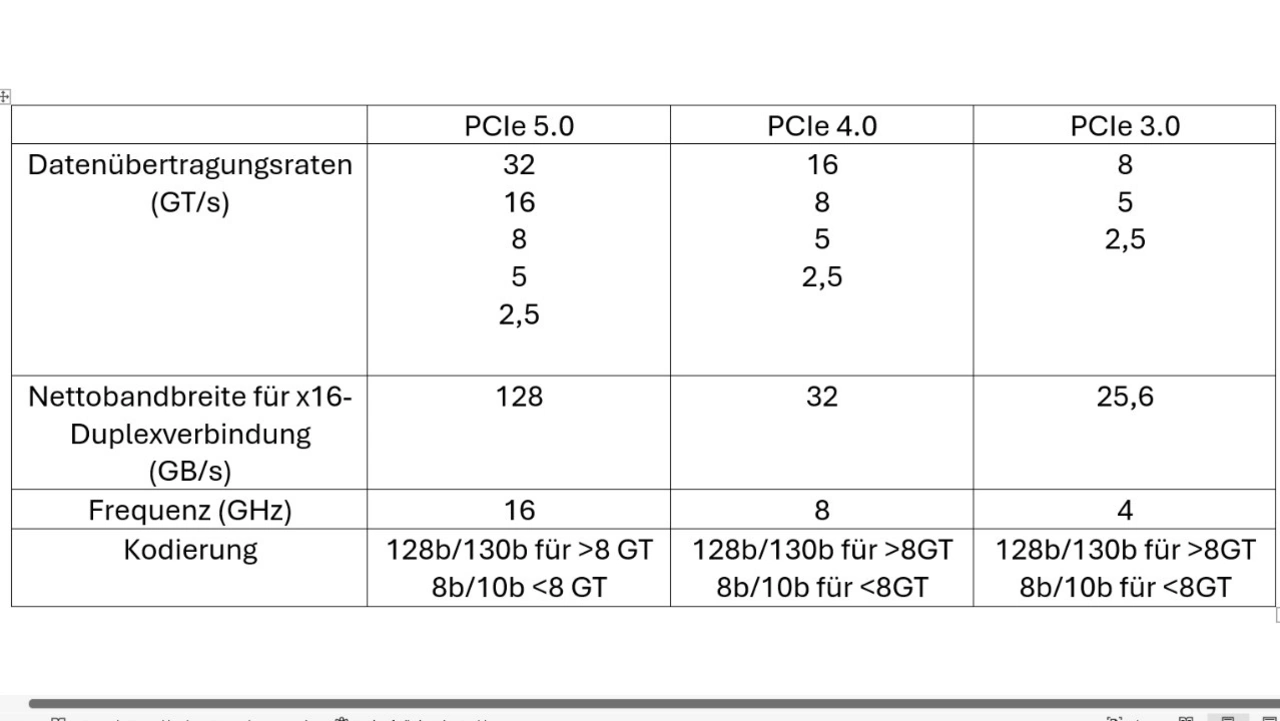

PCIe 5.0 kann eine maximale Bandbreite von 32 Gigatransfers pro Sekunde (GT/s) pro Lane und Richtung erreichen. Jeder Transfer umfasst einen Signalübergang in eine Richtung, und jeder Signalübergang entspricht einem Bit. Die effektive Bandbreite beträgt somit 32 Gigabit pro Sekunde (Gbps) pro PCIe-Lane und Richtung.

Bei einer 16-spurigen Duplex-Schnittstelle (wie dem typischen x16-Steckplatz einer GPU) entspricht dies einer Nettobandbreite von 128 Gigabyte pro Sekunde (GB/s). Der 8-spurige (x8) Duplex-PCIe-Steckplatz einer typischen Ethernet-Karte liefert netto 64 GB/s, was für den von 400GE-Netzwerken benötigten Durchsatz von 50 GB/s mehr als ausreichend ist.

Auch die Signalintegrität wurde verbessert. Die NRZ-Signalübertragung (Non-Return-to-Zero) von PCIe 5 läuft mit einer Frequenz von 16 Gigahertz (GHz), was doppelt so viel ist wie die 8 GHz von PCIe 4.0. Der höheren Signalabschwächung aufgrund von Einfügungsverlusten im Kanal bei dieser höheren Frequenz muss wirksam entgegengewirkt werden.

PCIe 5.0 nutzt daher neue Entzerrungs- und andere Techniken [2], um die Signalintegrität bei diesen höheren Geschwindigkeiten aufrechtzuerhalten. Dadurch werden eine bessere Leistung, höhere Zuverlässigkeit und geringere Fehlerraten erzielt und längere Kabellängen ermöglicht.

Gleichzeitig weist PCIe 5 reduzierte Fehlerraten auf. Der Standard schreibt eine niedrige Bitfehlerrate (BER) von 10-12 und einen Gesamtkanal-Einfügungsverlust von nur 36 dB vor. Um der Möglichkeit von mehr Burst-Fehlern entgegenzuwirken, schreibt es eine Vorcodierung an den Sendern vor.

Und schließlich kann PCIe 5.0 aufgrund seiner höheren Bandbreite mehr Geräte gleichzeitig ohne Engpässe unterstützen. Insbesondere in Rechenzentrumsumgebungen ist das von Vorteil.

Geschwindigkeit und Datenraten

Während PCIe 4.0 eine Datenrate von 16 GT/s erreicht, verdoppelt PCIe 5 diese auf 32 GT/s pro Lane in jeder Richtung. In Byte ausgedrückt kann ein PCIe Gen 4 x16-Gerät 32 GB/s erreichen, während PCIe 5.0 128 GB/s erreicht. Im Vergleich zu PCIe 3.0 mit 8 GT/s bietet PCIe 5 eine viermal höhere Durchsatzrate pro Lane. In Tabelle 1 sind weitere Parameter im Vergleich zu den Vorgängerversionen dargestellt.

Die maximale Datenübertragungsrate bei PCIe 5.0 beträgt 32 GT/s pro Lane und Richtung. Damit ergeben sich maximale Datenraten von 128 GB/s für einen x16-Duplex-PCIe-Steckplatz, 96 GB/s für x12 Duplex, und so weiter bis zu 8 GB/s für x1 Duplex.

Kompatibilität zu älteren Versionen

Die PCIe 5-Spezifikation schreibt vollständige Abwärtskompatibilität mit allen früheren Versionen vor. Außerdem ist davon auszugehen, dass PCIe 5-Geräte zukunftssicher sind und auch mit künftigen PCIe-Versionen problemlos funktionieren werden. Darüber hinaus kann ein PCIe-Gerät mit weniger Lanes in einen breiteren Steckplatz mit mehr Lanes eingesetzt werden. So kann beispielsweise eine x8-Netzwerkkarte in einen x16-Anschluss eingesetzt werden.

All dies ist durch Mechanismen zur Aushandlung gegenseitig kompatibler Lane-Anzahlen, PCIe-Versionen, Datenraten und Codierungsschemata möglich:

- Link-Training: Während des Link-Trainings kommunizieren die Endgeräte mit dem Root Complex. In dieser Phase der Link-Initialisierung werden PCIe-Versionen, Datenraten, Lanebreiten und Codierungsschemata ausgehandelt. Anschließend wird die Stabilität der Verbindung anhand dieser ausgehandelten Parameter überprüft.

- Capability-Register: Capability-Register in PCIe-Geräten liefern Informationen darüber, welche Versionen das Gerät unterstützt, wie viele Lanes maximal verfügbar sind und andere Parameter.

- Signalisierung: PCIe 5 verwendet wie alle früheren Versionen NRZ-Signalisierung. Das Datenkodierungsschema – wie 128b/130b oder 8b/10b – wird so ausgewählt, dass es gegenseitig kompatibel ist.

Aufwändige Anforderungen beim PCIe 5-Design

Die Entwicklung einer einwandfreien Signalintegrität ist bei PCIe 5 Designs von entscheidender Bedeutung. Übersprechen, Reflexion und Modenkonversion sind wichtige Faktoren, die zu Bitfehlern führen können und daher verhindert werden müssen.

Um die Einhaltung der strengen Standards zu gewährleisten, sind umfassende Tests der Bitübertragungsschicht erforderlich. Dazu gehören zeitaufwendige Analysen und Simulationen sowohl im Zeit- als auch im Frequenzbereich.

Außerdem müssen Entwickler bei der PCIe 5 beachten, dass hohe Datenraten zu Schwierigkeiten bei der Steuerung der Anstiegszeiten und zu Signalverzerrungen führen können.

Auch die differenzielle Signalübertragung muss überprüft werden: Jede PCIe-Lane besteht aus zwei differenziellen Paaren – einem Paar für das Senden und einem für das Empfangen. Eine ordnungsgemäße differenzielle Signalübertragung unter Vermeidung elektromagnetischer Störungen (EMI) erfordert sorgfältige Designs und Simulationen.

Um schließlich sicherzustellen, dass PCIe 5-Endpunkte und Root-Komplexe mit Geräten früherer Versionen zusammenarbeiten können, sind ebenfalls umfangreiche Simulationen erforderlich.

Herausforderungen und Einschränkungen

Wie aus diesen Anforderungen schon erkennbar ist, wird es bei der Einführung von PCIe 5.0 zu Herausforderungen kommen:

- Signalintegrität: Hochgeschwindigkeitsverbindungen wie PCIe 5 führen zu größeren Reflexionen bei Impedanzdiskontinuitäten, was das Augendiagramm verschlechtert, ein wichtiges Maß für die Signalqualität.

- PCB-Design (Printed Circuit Board): Das PCIe 5-Design erfordert verlustarme dielektrische Materialien, breite Signalbahnen und Techniken wie Back-Drilling von Durchkontaktierungen oder Micro-Via-Technologie, was den Designaufwand und die Komplexität erhöht.

- Fortschrittliche Messgeräte: Die Komplexität des digitalen Designs von PCIe 5 erfordert ausgefeiltere Messgeräte für die Analyse und Charakterisierung. Entwicklungsingenieure müssen über fundierte Kenntnisse der Signalausbreitungseigenschaften verfügen und Geräte wie 16-GHz-Vektor-Netzwerkanalysatoren einsetzen, um eine vollständige Charakterisierung der Komponenten der Bitübertragungsschicht zu erreichen.

- Jitter-Management: Kürzere Taktzyklen bedeuten geringere Jitter-Budgets. Die Reduzierung des Jitters in PCIe 5 ist im Vergleich zu früheren Generationen komplexer.

- Rückflussdämpfung: Es ist von entscheidender Bedeutung, dass die Rückflussdämpfung bei verschiedenen Frequenzen über bestimmten Grenzwerten bleibt. Dazu sind eine sorgfältige Kanalplanung und Konformitätsprüfungen erforderlich.

- Empfängerdesign: Empfänger sind aufgrund von Hochfrequenzkanalverlusten anfälliger für Signalverschlechterungen. Es ist daher unerlässlich, robuste Empfänger zu entwickeln, die Signalverschlechterungen tolerieren und gleichzeitig akzeptable BER-Werte erzielen.

- Protokolltests: Verschiedene Zustandsübergänge innerhalb der Protokollschicht sowie LTSSM (Link Training and Status State Machine) müssen mithilfe ausgefeilter Emulations- und Testaufbauten validiert werden.

- Arbeitsintensive Tests: Die Komplexität von PCIe 5 macht den Testprozess sehr arbeitsintensiv. Unternehmen benötigen robuste automatisierte Testlösungen, um die Testdauer von Tagen auf Stunden zu reduzieren.

EDA-Software für PCIe 5.0-Design?

EDA-Tools (Electronic Design Automation) sind für die Bewältigung der zuvor beschriebenen Herausforderungen und zeitaufwendigen Aufgaben von entscheidender Bedeutung.

So helfen sie beispielsweise bei der Simulation der Signal- und Leistungsintegrität. Angesichts der zunehmenden Vielfalt der Kanaltopologien und der steigenden Anzahl von Parametern sind zur Gewährleistung der Signal- und Leistungsintegrität Tools erforderlich, die die elektromagnetischen Auswirkungen von integrierten Hochgeschwindigkeitsschaltungen und PCB-Verbindungen simulieren können. EDA-Tools können Bedingungen wie Übersprechen und Reflexionen simulieren, um Signalverschlechterungen und Timing-Probleme zu vermeiden. Dazu gehört auch die Minimierung von Jitter, was angesichts immer kürzerer Taktzyklen von entscheidender Bedeutung ist.

Mit EDA-Software können IBIS-Modelle (Input-Output Buffering Information Specification) und AMI-Modelle (Algorithm Modeling Interface) zur Simulation analoger Kanäle und durchgängiger Signalpfade erstellt und ausgeführt werden. Außerdem hilft EDA-Software beim Verständnis und bei der Optimierung jeder einzelnen Schicht – Bitübertragungsschicht, Datenverbindungsschicht und Transaktionsschicht.

Durch die gleichzeitige Co-Simulation verschiedener Bereiche ermöglicht EDA-Software End-to-End-Analysen. EDA-Software ist für die Durchführung der von der PCI-SIG (PCI Special Interest Group) geforderten Konformitätstests von entscheidender Bedeutung. Diese Tests überprüfen, ob die elektrische Leistungsfähigkeit den PCIe 5.0-Standards entspricht.

Mit EDA-Tools können Entwickler einen Großteil des Testprozesses automatisieren und so maximale Effizienz erzielen. Die Automatisierung von Konformitätstests und die Erstellung von Berichten tragen zu einer schnellen Validierung und Anpassung der Designs bei.

Keysights Angebot für PCIe 5.0-Design und -Verifizierung

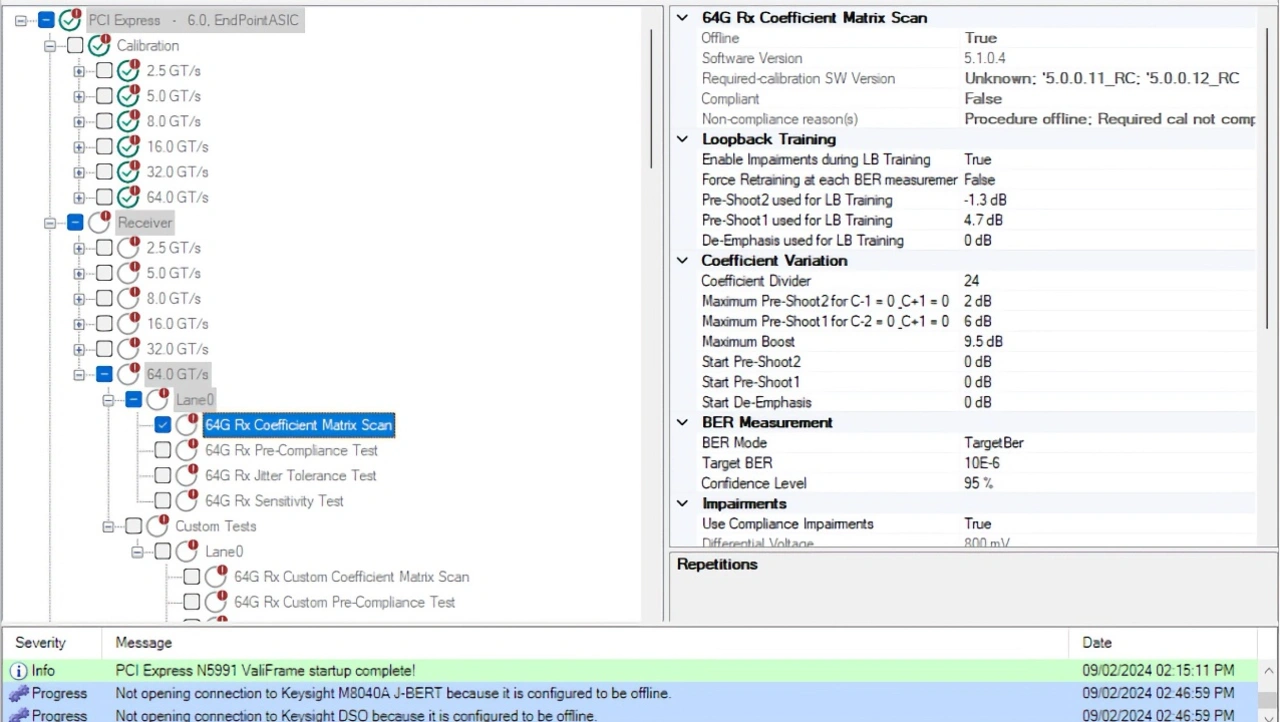

Keysight bietet ein umfassendes Angebot an Softwarelösungen und Hardware- Messgeräten für die detaillierte Entwicklung, Simulation und Prüfung von PCIe 5. Dazu gehören EDA-Lösungen wie der System Designer for PCIe, eine End-to-End-Entwicklungsumgebung für die Modellierung und Simulation von PCIe 5.0-Systemen. Auch Softwarelösungen für Transceiver-Tests bietet Keysight an, vom Physical Layer Test System (PLTS) für die Prüfung der Signalintegrität der Verbindungen, über die Receiver Compliance Test Automation Platform zum Test von PCIe 5-Empfängern (Bild 2) bis zur Transmitter Electrical Performance Validation and Compliance Software zum Testen von PCIe 5-Transmittern.

Schließlich bietet Keysight für die Protokollanalyse den PCIe 5 Protocol Exerciser und den Protocol Analyzer für die Analyse aller Topologien und Anwendungsfälle (Bild 3).

Quellen:

[1] https://pcisig.com/how-pcie%C2%AE-technology-enables-machine-learning-and-artificial-intelligence

[2] https://www.youtube.com/watch?v=najBAl2BBqE