Mikrocontroller für die Medizin

Die ersten ARMv8-M-CPUs: Cortex-M23/M33

Fortsetzung des Artikels von Teil 2

Cortex-M33 mit neuer Pipeline

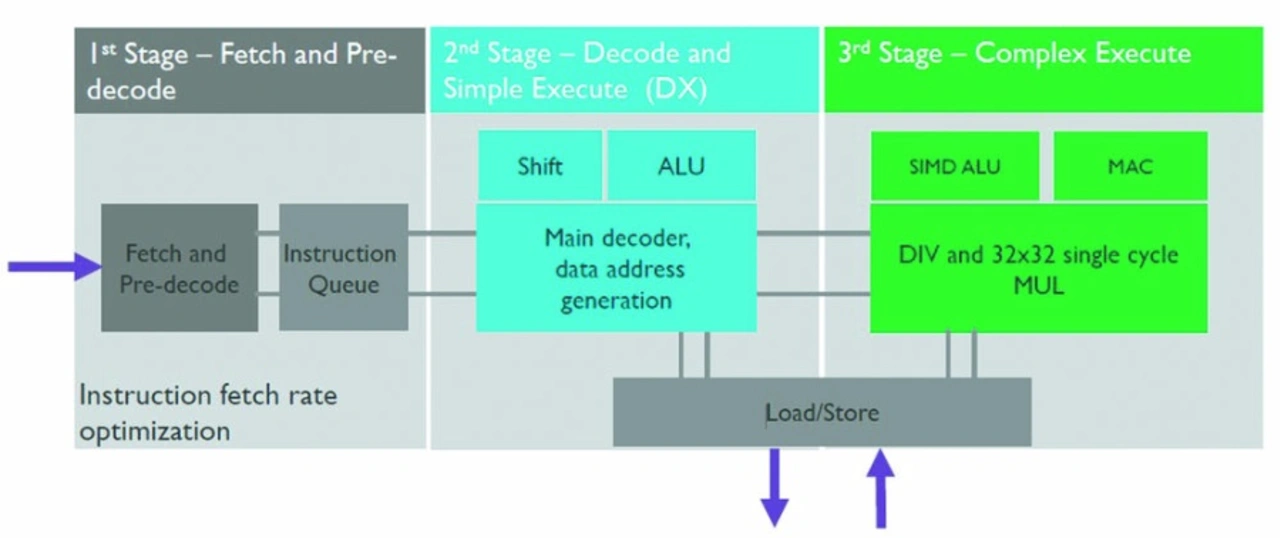

Anders als beim M23 wurde für den M33 eine gegenüber dem Cortex-M4 vollständig neue Pipeline entwickelt (Bild 3). Diese besteht zunächst quasi aus den ersten zwei Stufen des M0+, allerdings mit Harvard-Architektur. Der Zugriff auf Befehl- und Datenspeicher erfolgt jeweils über je einen eigenen AHB5-Bus. Hinzu gekommen ist eine weitere (dritte) Stufe, in der komplexe Operationen wie SIMD, MAC, DIV und 32x32-Multiplikation abgearbeitet werden. Bereits in der 1. Stufe werden wie bei M0+ (und M23) 16-bit-Thumb-Instruktionen vordecodiert und in eine der fünf Befehlswarteschlangen eingestellt. In der 2. Stufe sind Haupt-Befehlsdecoder, Arithmetisch-Logik-Einheit (ALU) und Verschieboperationen verortet. Der Vorteil ist, dass beim Abarbeiten derartiger Instruktionen schon nach der 2. Stufe Schluss ist. Dazu werden in der 2. Stufe alle Verzweigungen aufgelöst. Bei M3/M4 passiert dies in vielen Fällen erst in der 3. Stufe und bei denen, die in der 2. Stufe aufgelöst werden, kommt ein spekulativer Prefetch der Zieladresse zum Einsatz, was die Leistungsaufnahme erhöht.

Neu ist auch die Möglichkeit der Dual-Issue-Befehlsausführung für Thumb-16- und Verzweigungsinstruktionen. Der Cortex-M4 erlaubt lediglich IT-Folding, d. h. beim Auftreten einer If-then-Bedingung-Instruktion (IT, bis zu vier folgende Befehle können in Abhängigkeit des Eintretens einer Bedingung ausgeführt werden) kann die CPU mit der Ausführung der ersten Instruktion in dem IT-Block beginnen, während die IT-Instruktion selbst noch in der Ausführung ist.

Schließlich wurde noch der Zugriff beim Laden/Speichern von Daten beschleunigt, indem die Adresserzeugung bereits in Stufe 2 beginnt. Beim Cortex-M3/M4 ist dies erst in Stufe 3 der Fall, wodurch Ladeoperationen zwei Taktzyklen benötigen. Die Interrupt-Latenzzeiten betragen zwölf Taktyzklen, wenn die CPU im sicheren oder unsicheren Status verbleibt. Bei einem Statuswechsel, bei dem der vollständige Registersatz gerettet werden muss, sind es 21 Taktzyklen.

Was ist das Ergebnis der neuen Mikroarchitektur? Statt 3,40 Coremark/MHz liefert der M33 eine Rechenleistung von 3,86 Coremark/MHz, immerhin eine Steigerung um 13 %.

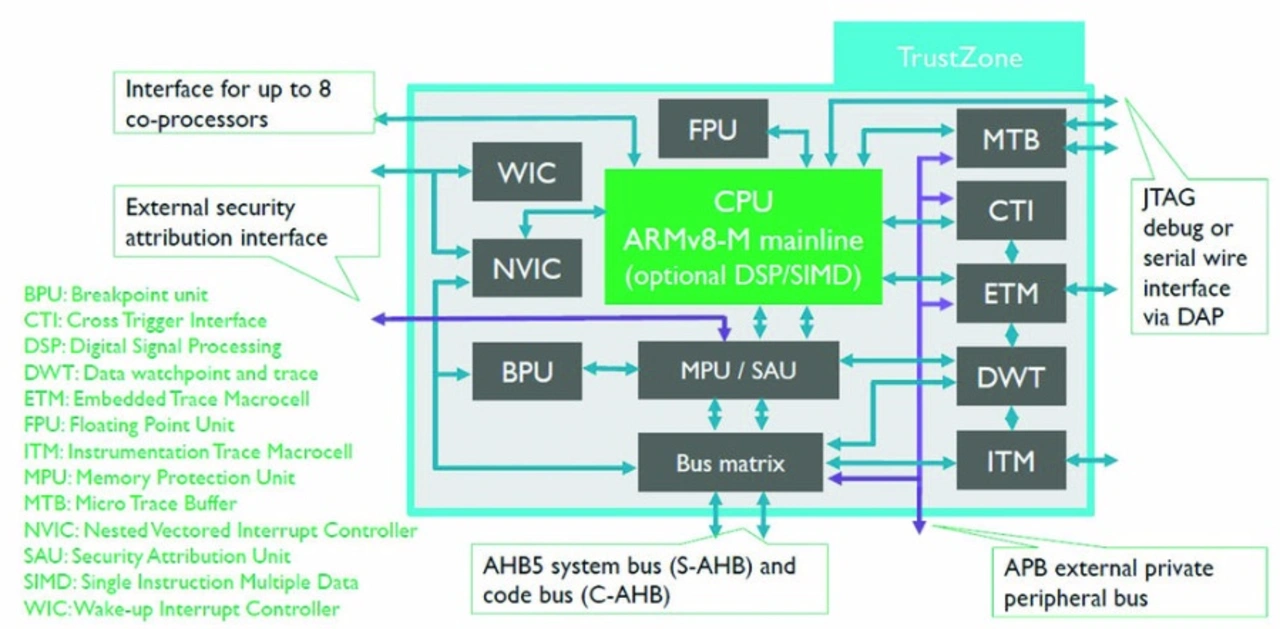

Bild 4 zeigt das Blockdiagramm des Cortex-M33. Während die DSP-Funktionalität im Cortex-M4 fest eingebaut ist, ist auch diese beim M33 optional konfigurierbar, genauso wie die Gleitkommaeinheit (FPU). Das »Mainline«-Profil des M33 enthält zusätzlich zu weiteren 32-bit-Befehlen auch optional die schon vom M4 bekannten 80 DSP- und/oder 45 FPU-Instruktionen gemäß IEEE 754. Viele Kunden wollen entweder DSP oder FPU haben, daher hat man die Auswahlmöglichkeiten erhöht. Kunden, die z. B. mit Gleitkomma-DSPs arbeiten, können mit dem Integer-DSP des Cortex-M4 nichts anfangen, haben ihn aber zwangsläufig mitgeliefert bekommen. Dies wird zukünftig nicht mehr der Fall sein, sodass bedarfsbezogen Gatter und Siliziumfläche eingespart werden.

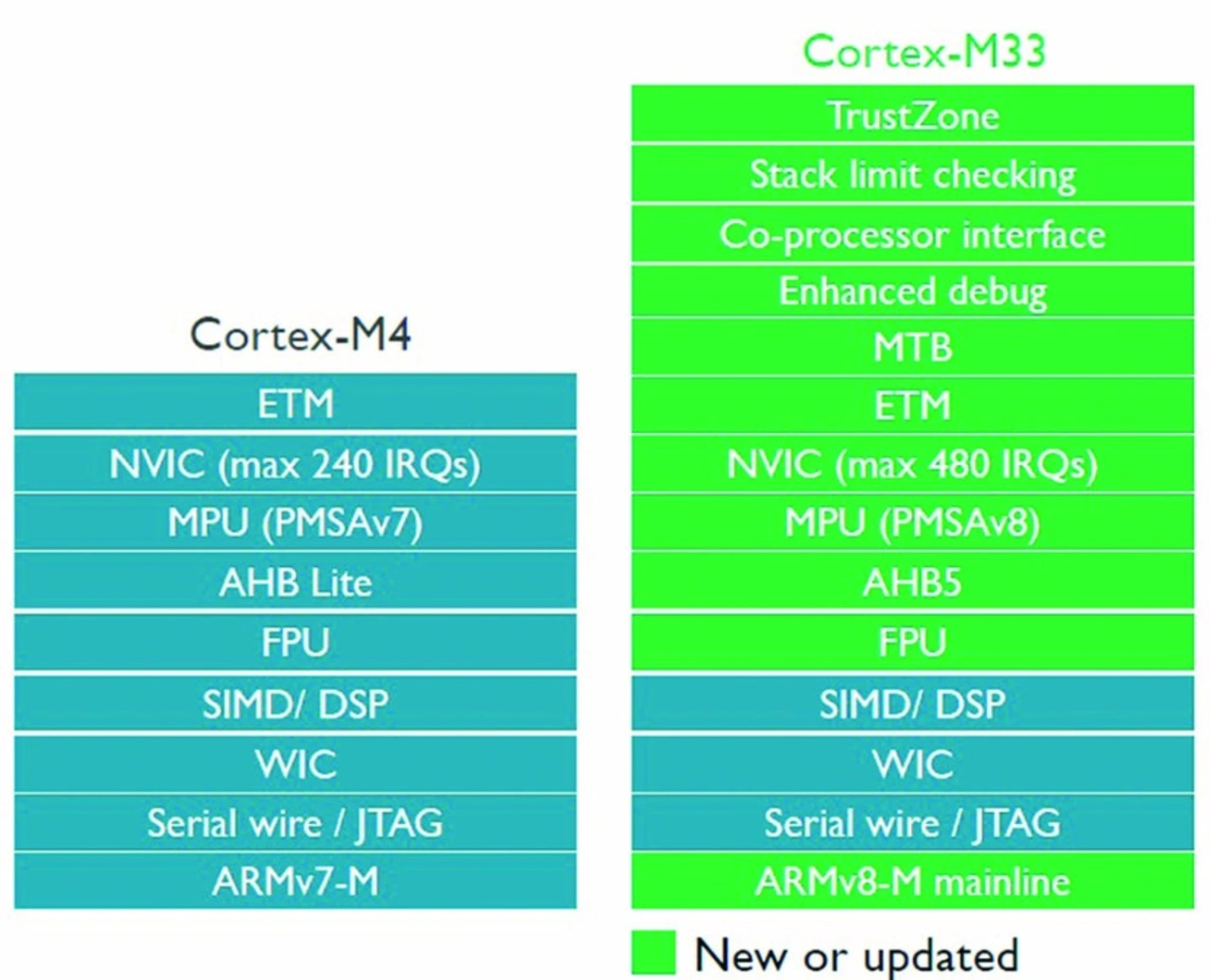

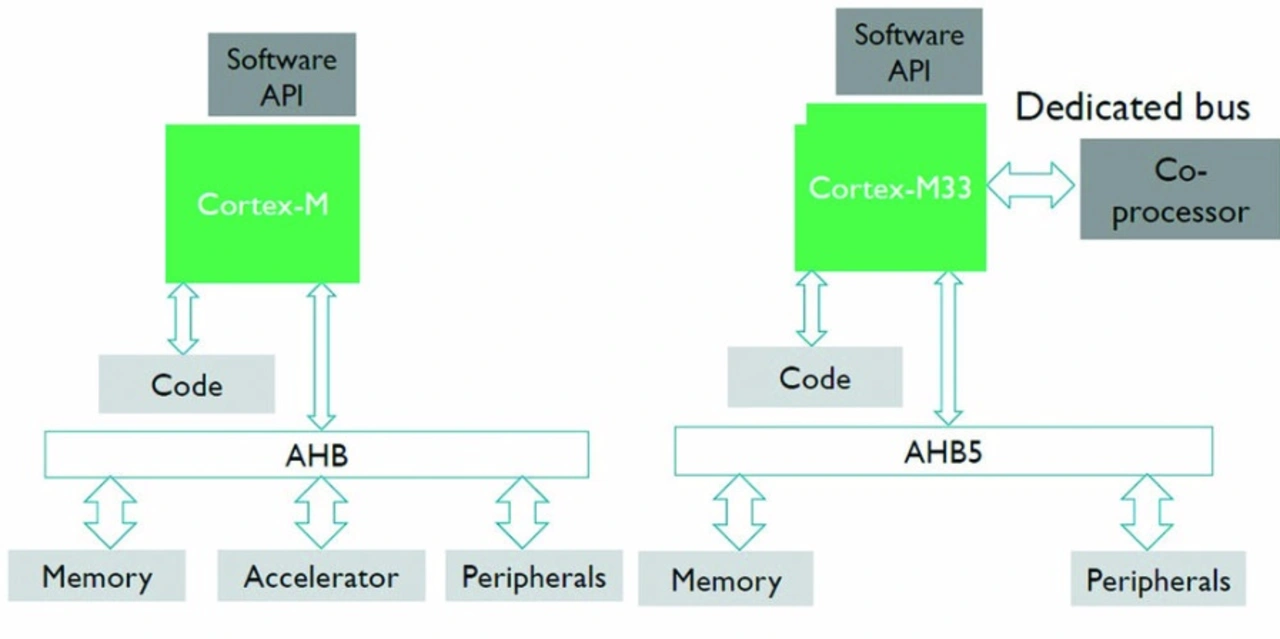

Was alles einen Cortex-M33 von einem Cortex-M4 unterscheidet, zeigt in komprimierter Form Bild 5. Einen echten Fortschritt bringt die neue Coprozessor-Schnittstelle. In Bild 6 ist links der bislang verwendete Ansatz der Cortex-M-CPUs dargestellt, bei dem sich Hardwarebeschleuniger, Speicher und Peripherie den AHB-Bus teilen. Da die Chips jedoch zunehmend komplexer werden (mehr Speicher, mehr Peripherieblöcke, Beschleuniger für Verschlüsselung, mathematische Funktionen u.v.m.), wurde es Zeit, den AHB-Bus zu entlasten. Mit der neuen Schnittstelle, welche die Anbindung von bis zu acht Beschleunigern direkt an die CPU erlaubt (Bild 6 rechts), wird dies realisiert. Das Ganze funktioniert so, dass es eine Transfer-Instruktion gibt, über die eine ID (welcher Beschleuniger soll adressiert werden) und ein bis zwei 32-bit-Werte in Registern übergeben werden. Alternativ kann die weitere Codeausführung warten, bis der Coprozessor Ergebnisdaten zurückgeliefert hat. Man kann aber auch einen Interrupt konfigurieren, der ausgelöst wird, wenn die Daten bereitstehen.

- Die ersten ARMv8-M-CPUs: Cortex-M23/M33

- Schnellzugriffsoption

- Cortex-M33 mit neuer Pipeline

- Microchip lizensiert Cortex-M23 und/oder -M33