Mikrocontroller für die Medizin

Die ersten ARMv8-M-CPUs: Cortex-M23/M33

Fortsetzung des Artikels von Teil 1

Schnellzugriffsoption

Wie beim M0+ können beim M23 alle zwei Taktzyklen über den 32-bit-Bus jeweils zwei 16-bit-Werte gemeinsam aus dem Flashspeicher geladen werden, was besonders bei sequenziellem Code Vorteile bringt, da weniger häufig auf den stromfressenden Flashspeicher zugegriffen werden muss. Des weiteren kann mit der »Schnellzugriffsoption auf I/O« in jeweils einem statt zwei Taktzyklen auf I/Os zugegriffen werden, weil parallel zum AHB5-Bus ein weiterer Port installiert ist. Über diesen kann doppelt so schnell auf GPIOs und Register zugegriffen werden (eine LOAD-/STORE-Anweisung kostet normalerweise zwei Taktzyklen), für Speicherzugriffe eignet sich der Schnellzugriffsport hingegen nicht.

Besonders für Echtzeitanwendungen wichtig ist die optionale Möglichkeit, die Interrupt-Vektor-Tabelle vom Flashspeicher ins RAM zu verschieben. Da z. B. die Löschung eines Flashblocks mehrere Millisekunden dauern kann und der Controller in dieser Zeit »blind« für Interrupts ist, weil die Interrupt-Vektoren im für diesen Zeitraum blockierten Flashspeicher liegen, ist er für diverse Echtzeitanwendungen unbrauchbar. Beim M23 kann man die Vektor-Tabelle ins RAM verschieben, so dass auch während eines Flash-Schreib- oder -Lösch-Vorgangs Interrupts verarbeitet werden können.

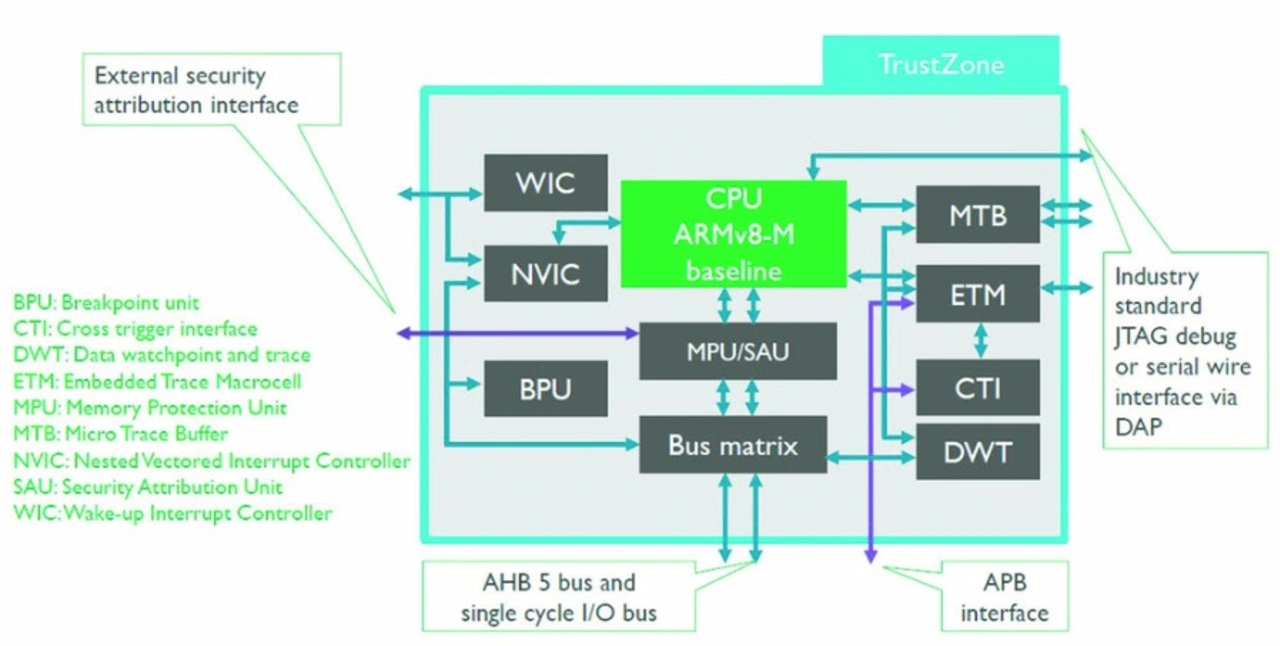

Bild 1 zeigt das Blockdiagramm des Cortex-M23. Alle Blöcke, die in grüner Schrift aufgezählt sind, können optional konfiguriert werden, dies gilt auch für die beiden MPUs (eine für sicheren und eine für unsicheren Zustand [1]) und auch für die SAU. Dieser Security-Attribution-Einheit genannte Block definiert sichere und unsichere Speicherregionen mit einer Auflösung von 32 Byte. Anders formuliert: Ob sich die CPU im sicheren oder unsicheren Zustand befindet, definiert sich ausschließlich über die zugegriffene Speicheradresse und deren Zustandsdefinition über die SAU. Ein MCU-Hersteller hat neben der softwaremäßig programmierbaren SAU auch hardwaremäßig auf Systemebene die Möglichkeit, bestimmte Adressräume unüberschreibbar als sicher zu definieren – z. B. Verschlüsselungsperipherie oder bestimmte Bereiche eines Flashspeichers, in die er Firmware geladen hat.

Neu ist beim M23 gegenüber dem M0+, dass für das Debugging neben einem Micro-Trace-Puffer (MTB) auch eine Embedded-Trace-Macrocell (ETM) implementierbar ist, die man vom M3, M4 und M7 kennt. Der MTB zeichnet alle nicht-sequenziellen Anweisungen auf (z. B. JMP, Interrupt, CALL), sodass im Fehlerfall der Programmfluss zu erkennen ist. Der Vorteil für Entwickler ist, dass sie z. B. einen Breakpoint setzen können und bei Erreichen des Breakpoints eine Traceaufzeichnung bekommen, in der sie genau verfolgen können, welche Programmteile zuvor ausgeführt wurden. Hilfreich ist dies beispielsweise bei sporadischen Problemen, die durch fehlerhaften Code wie ein Befehlsreihen-Folgeproblem in Interruptroutinen verursacht werden.

Weiter als der MTB geht die ETM. Diese und deren Weiterentwicklung »Core-Sight« unterstützt sowohl Programm- als auch Datentrace. CoreSight erlaubt zusätzlich das Tracen der Context-ID und ist zudem multicorefähig. Zur Übertragung der Tracedaten an den Debug-Host kommt ein relativ breitbandiger Traceport zum Einsatz, der in mehreren Modi mit unterschiedlichen Datenraten betrieben werden kann. Die zu übertragenden Tracedaten werden vorher durch FIFO-Buffer serialisiert. Im Allgemeinen sieht das ETM-Konzept Komparatoren für Adressbereiche, Daten sowie den Zugriffsmodus (Lesen oder Schreiben) vor. Speziell für den Programmtrace kann definiert werden, zu welchem Zeitpunkt in der Pipelineverarbeitung (Fetch oder Execute) ein Adresskomparator auf eine passende Adresse reagiert. Durch Verknüpfung der einzelnen Komparatoren können komplexere Triggerbedingungen zur Steuerung der Traceaufzeichnung definiert werden. Mit Hilfe von Zählern und eines Sequenzers zur Realisierung einer State-Machine mit maximal drei Zuständen lässt sich auch das sequenzielle Verhalten sehr gut rekonstruieren. Durch die Verfügbarkeit der ETM auch für die »kleinen« ARMv8-M-CPUs hat der Entwickler nun (endlich möchte man sagen) die Möglichkeit eines einheitlichen Debuggings über alle CPUs.

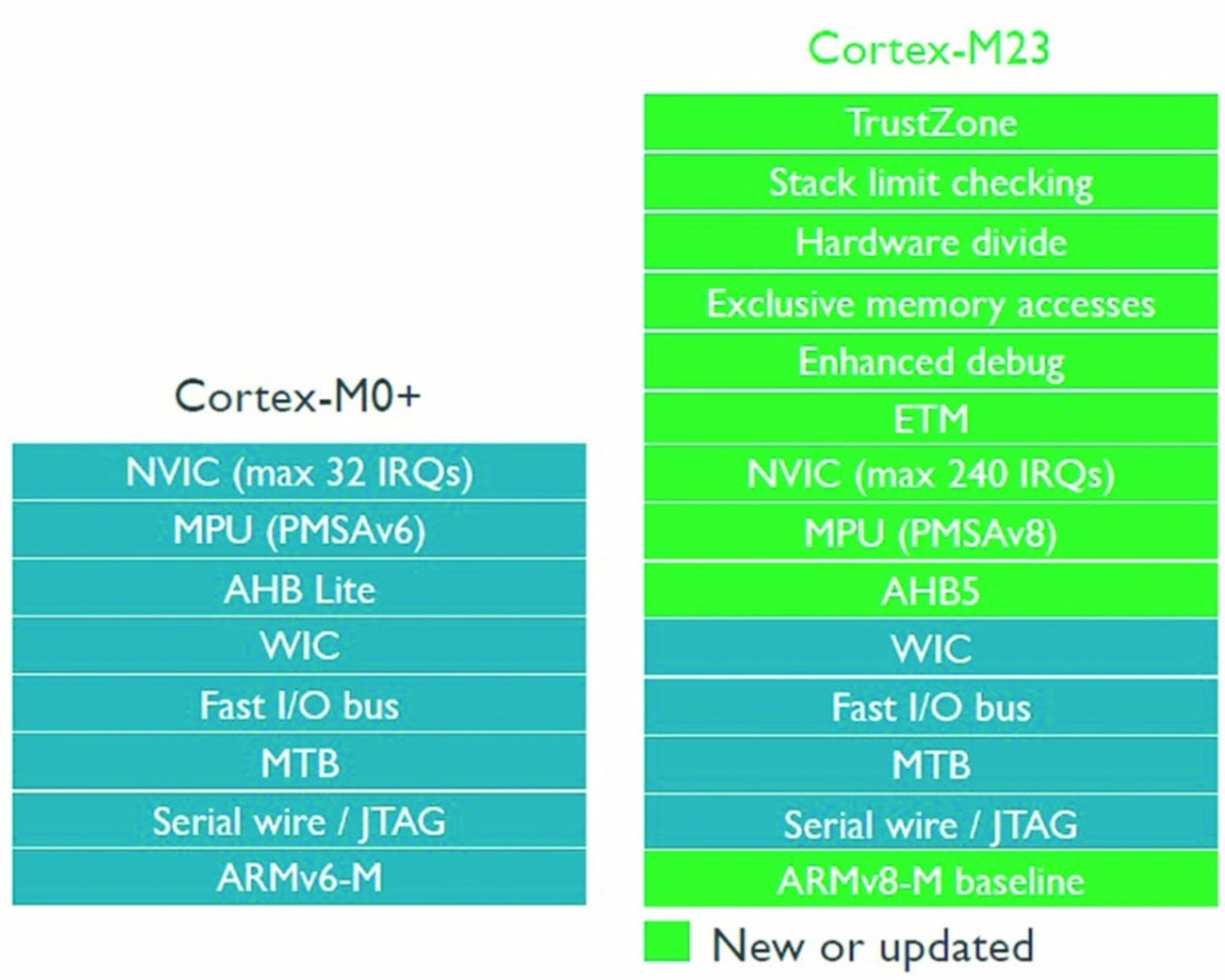

Die sogenannte Cross-Trigger-Schnittstelle (CTI) ist nur bei Multicore-Implementierungen relevant. Mit ihr lassen sich z. B. im Fall eines Breakpoints alle CPUs gleichzeitig anhalten. Bild 2 fasst alle Veränderungen/Verbesserungen des M23 gegenüber dem M0+ zusammen. Insbesondere durch den erweiterten Befehlssatz des Baselineprofils ist die Rechenleistung allerdings sehr moderat gestiegen: Statt 2,46 Coremark/MHz stehen nunmehr 2,50 Coremark/MHz zu Buche.

- Die ersten ARMv8-M-CPUs: Cortex-M23/M33

- Schnellzugriffsoption

- Cortex-M33 mit neuer Pipeline

- Microchip lizensiert Cortex-M23 und/oder -M33