Miniaturisierung der Chip-Verdrahtung

Toolbox mit neuen Prozessen, Leitermaterialien und Boostern

Fortsetzung des Artikels von Teil 1

Supervia-Strukturen für besseres Routing

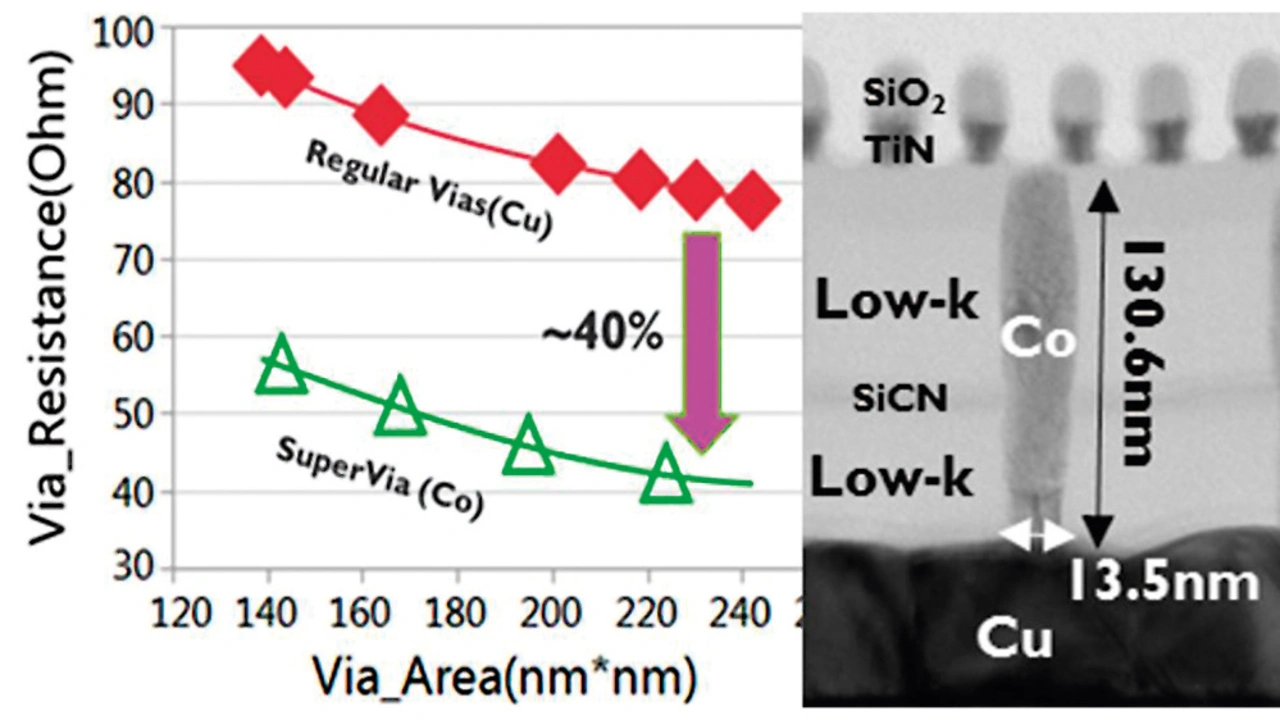

Eine weitere Verbesserung der Verbindungsmöglichkeiten ermöglichen Supervia-Strukturen, also Durchkontaktierungen mit großem Aspect Ratio. In ihrer einfachsten Form verbinden sie eine Mx-Lage mit einer Mx+2-Lage. Supervias gehören zur Familie der Scaling Booster. Sie wurden eingeführt, um die Anzahl der Verbindungen zu reduzieren, als eine Methode zur weiteren Verkleinerung der Chipfläche – und um damit auch die Höhe von Standard-Logikzellen zu reduzieren.

In ihrer einfachsten Form stellt die Supervia eine direkte Verbindung zwischen einer Mx- und einer Mx+2-Lage her, und zwar durch die Umgehung einer Mx+1-Zwischenlage in selbst ausrichtender Weise. Supervias und reguläre Vias können in demselben Chip-Entwurf koexistieren, wobei die Supervias dort implementiert werden, an denen sich ein Vorteil durch den kurzen Verbindungsweg (jumping faster) ergibt (Bild 4).

Jobangebote+ passend zum Thema

Erste Anwendungsfälle sind SRAMs und vergrabene Leiterbahnen für die Stromversorgung, Versorgungsleitungen, die im FEOL-Bereich der Chip-Fertigung im Chip eingebettet sind, schaffen Platz für die Verbindungen in den Metallisierungslagen. Auf der IITC 2019 hat das IMEC z.B. einen Ru-Ätzprozess für Kavitäten mit hoher Konstanz der Verbindungswiderstände und niedrigem Leiterbahnwiderstand vorgestellt – ein wichtiger Schritt bei der Integration vergrabener Versorgungsleitungen.

Um Supervia-Strukturen zukünftig einzusetzen, über den 3-nm-Technikknoten hinaus, hat das IMEC eine Roadmap definiert, die eine zweite – von Mx auf Mx+3 und Mx+4 – und eine dritte – von Mx auf Mx+5 – Generation von Supervias umfasst. Diese ultimative dritte Generation, auch als »Ubervia« bezeichnet, ist komplex und noch weit vor ihrer Realisierung. Doch sie würde es erlauben, direkt zu den breiteren metallischen Leiterbahnen zu »springen«, und damit die geeigneten Mittel zur weiteren Reduktion der RC-Metrik bieten.

Schlüsseltechniken: alternative Leitermaterialien

Über die letzten Jahre war das IMEC ein Pionier und Wegbereiter bei der Suche nach neuen Metallen als Ersatz der mehr konventionellen Materialien wie Cu, Wolfram (W) und Co. Diese alternativen Leiter werden der Schlüssel zur Realisierung der oben beschriebenen Innovationen sein, einschließlich der »nächsten Generation« von Dual-Damascene- und Semi-Damascene-Modulen sowie der Supervia-Strukturen.

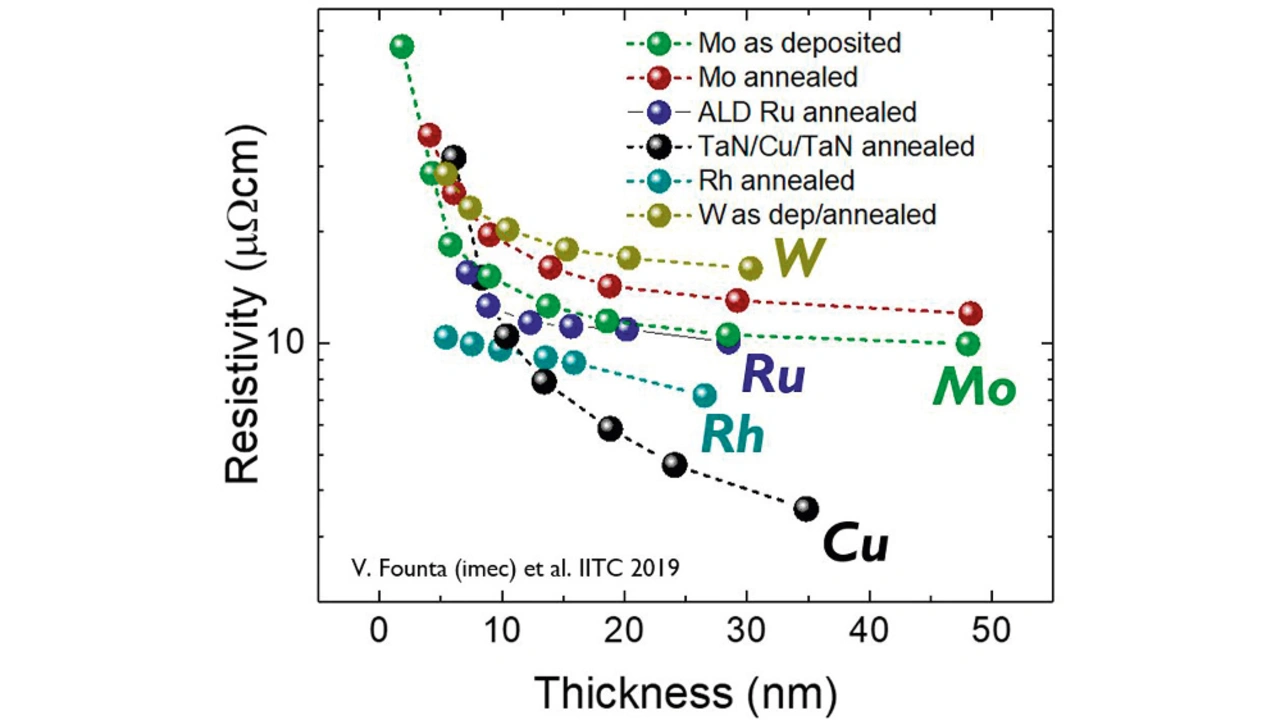

Als ein erster Schritt bei der Suche nach alternativen Metallen wurde eine Kennzahl (FOM) definiert, um eine Rangliste der Kandidaten zu ermöglichen. Diese FOM, definiert als das Produkt aus dem spezifischen Widerstand und der mittleren freien Weglänge der Ladungsträger im Metall, wird mittlerweile von der wissenschaftlichen Gemeinschaft als ein guter Startpunkt für die Bewertung gesehen – mit Cu, W und Co als Referenzmaterialien. Das Metall mit der niedrigsten FOM ist Rhodium (Rh), gefolgt von Platin (Pt), Iridium (Ir), Nickel (Ni), Ruthenium (Ru), Molybdän (Mo) und Chrom (Cr).

Die Rangliste enthält allerdings keine Metrik in Bezug auf die Kosten, die Empfindlichkeit gegenüber dem Tempern oder der Adhäsion auf dem Dielektrikum. So zeigen Ir und Rh beispielsweise eine sehr schwache Adhäsion gegenüber dem Dielektrikum, und besonders Rh ist sehr teuer – sogar teurer als Gold (Au).

Auf der experimentellen Seite hat das IMEC unter anderem demonstriert, dass Mo ein sehr viel versprechendes Material für Chip-Verbindungen ist, besonders als potenzieller Ersatz für W in stark miniaturisierten Dimensionen (Bild 5). Die Arbeiten an alternativen Metallen wurden von den IMEC-Wissenschaftlern ebenfalls auf der IITC 2019 vorgestellt.

Das Team befasste sich auch mit binären und ternären Verbindungen als

Alternativen für die konventionellen Leitermaterialien. Speziell die sogenannten MAX-Phasen verhalten sich besser als reine Elemente – und eröffnen damit eine Gelegenheit für weitere Forschungen. MAX-Phasen sind geschichtete Strukturen, die aus einem frühen Übergangsmetall (M), einem Element der A-Gruppe (A) und Kohlenstoff oder Stickstoff (X) bestehen.

Schließlich lässt sich der spezifische elektrische Widerstand von Metallen wie Ru auch durch das Abdecken der Leiterbahnen mit Graphen verringern, einem nur eine Atomlage dicken Material mit hoher elektrischer und thermischer Leitfähigkeit, sowie hoher Stromtragfähigkeit. Auf der IITC 2019 hat das IMEC den niedrigeren elektrischen Widerstand und die höhere thermische Stabilität von Ru-Drähten mit Graphen-Einkapselung demonstriert. Diese Ergebnisse zeigen einen möglichen Entwicklungspfad für hybride Kohlenstoff/Metall-Verbindungsleitungen auf.

Zusätzliche Funktionen in der Metallisierung

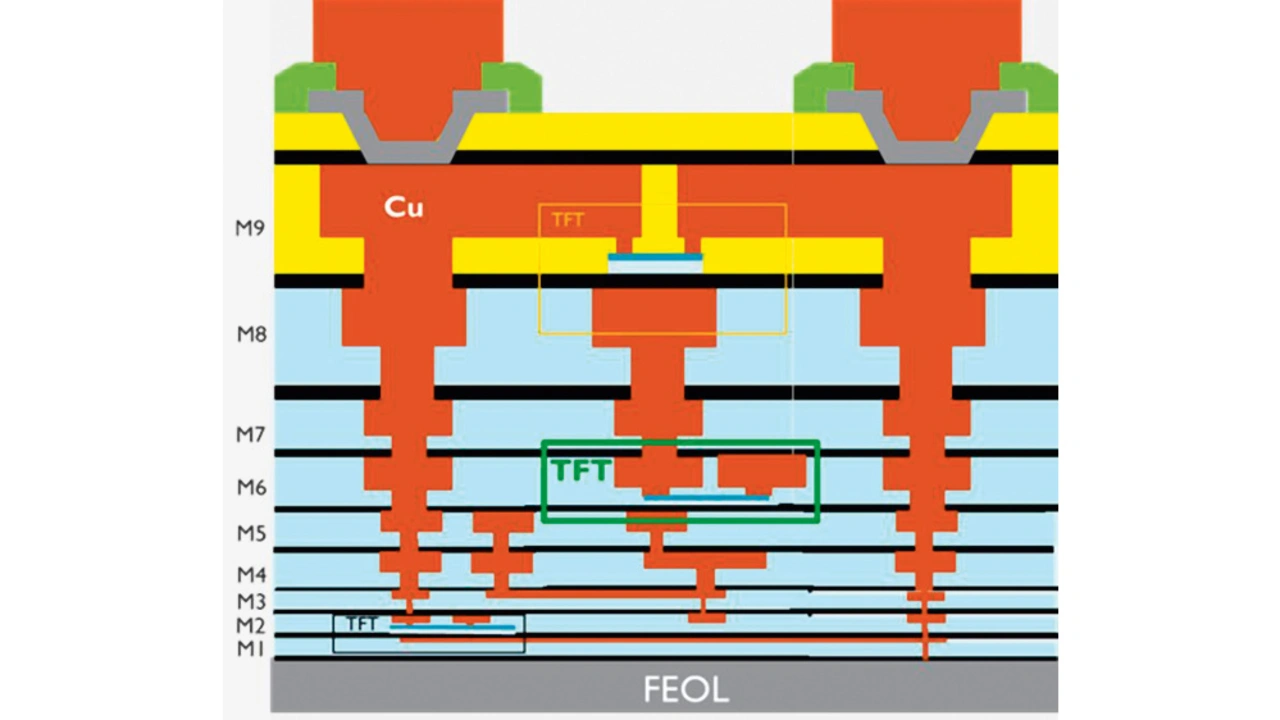

Auf der Zwischenebene von der M6- auf die M8-Lage ist die Dichte der Durchkontaktierungen bei fortschrittlichen Chips relativ gering. Das ermöglicht die Schaffung und Nutzung von freien Räumen, die sich zur Implementierung kleiner Transistoren eignen. Hinreichend kleine und temperaturkompatible Dünnschichttransistoren können diesen Zweck erfüllen. Das ermöglicht es, zusätzliche Funktionen in die Metallisierungslagen zu integrieren (Bild 6).

Die Ziel-Applikationen liegen in der IC-internen Stromversorgung, sowohl für Server-, als auch für Mobilfunk-ICs, in dualen VT-Logikschaltungen, in FPGAs mit großen SRAM-Arrays, in Ein-/Ausgängen mit Pegelumsetzern und in Signalpuffern für neuromorphische Konzepte. Auch der Einsatz in DRAM-Speicherbausteinen oder zum Auswählen nichtflüchtiger Speicher ist möglich.

Der ultimative Wunschtraum sind Signalverstärker (Repeater), die in den gegenwärtigen IC-Entwürfen einen großen Raum einnehmen. Doch dafür sind sowohl n-, als auch p-leitende TFTs erforderlich, wobei letztere nicht weit genug für eine reale Implementierung fortgeschritten sind. Andere Herausforderungen sind die Zuverlässigkeit, der Reifegrad der CMOS-Prozesstechnik, sowie die Kosten – obwohl bei diesen großzügigen Dimensionen die einfache Single-Print-Immersionslithografie eingesetzt werden kann, um das Verfahren kosteneffektiv einzusetzen.

Das IMEC-Team hat kürzlich einen Demonstrator mit funktionsfähigen Indium-Gallium-Zinkoxid-TFTs (IGZO) auf einem 300-mm-Wafer mit geringem Leckstrom – auch bei erhöhter Temperatur – präsentiert.

Der Autor

Zsolt Tokei, Ph.D.

ist Program Director für Nano-Interconnects beim IMEC. Er kam 1999 zum IMEC und hat seitdem mehrere technikbezogene Positionen eingenommen: zunächst als Prozessingenieur und Forscher auf dem Gebiet des Low-k-Cu-Interconnect. Anschließend leitete er die Metal Section. Später wurde er leitender Wissenschaftler und Program Director für Nano-Interconnects.

Tokei hat 1994 sein Physikstudium an der Kossuth Universität Debrecen in Ungarn mit dem Master abgeschlossen. Im Rahmen einer zweifach begutachteten Doktorarbeit an der ungarischen Kossuth Universität und der französischen Universität Aix Marseille-III erwarb er 1997 seinen Ph.D.-Grad in Physik und Materialwissenschaft. 1998 begann er seine Tätigkeit als Postdoc am Max-Planck-Institut in Düsseldorf. Beim IMEC setzte er seine Arbeit mit einer Reihe von Interconnect-Themen fort, einschließlich Skalierung, Metallisierung, elektrische Charakterisierung, Modul-Integration, Zuverlässigkeit und Systemaspekte.

zsolt.tokei@imec.be

- Toolbox mit neuen Prozessen, Leitermaterialien und Boostern

- Supervia-Strukturen für besseres Routing