Arm TechDays 2019

Auf in Cloud und Infrastruktur: Das ist Arms Neoverse-Universum

Fortsetzung des Artikels von Teil 4

Neoverse-Entwicklungsboard

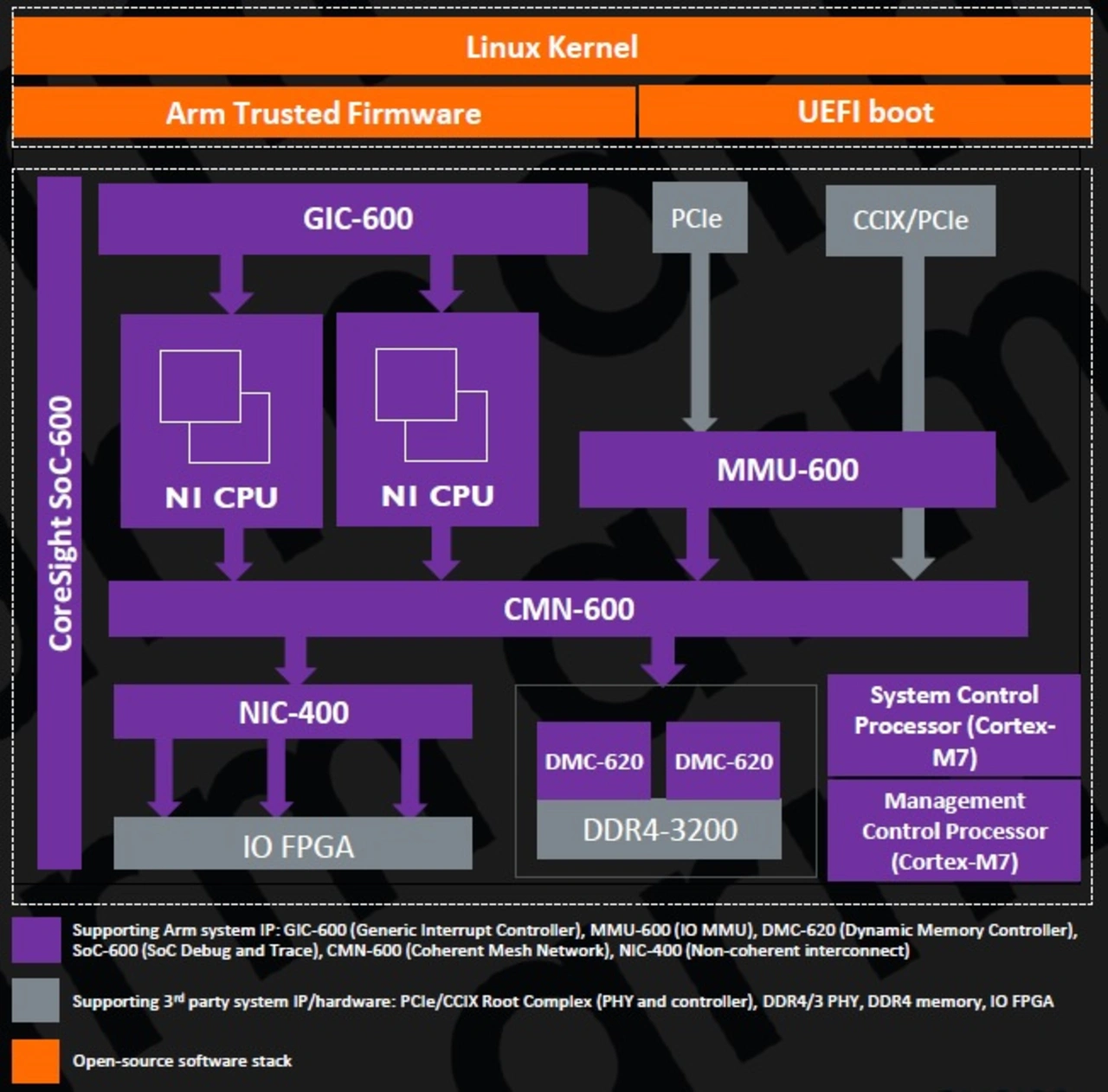

Um Kunden den Zugang zum Neoverse-Universum zu erleichtern, bietet Arm als Entwicklungsplattform die sogenannte Neoverse System Development Platform (SDP) an, die noch in diesem Quartal (Q1/2019) erhältlich sein wird (Bild 12).

Sie beinhaltet neben zwei in 7 nm implementierten Dual-Core-Neoverse-N1-CPU-Clustern mit jeweils 1 MB L2-Cache pro Core (Taktfrequenz bis 3 GHz möglich) auch zwei Cortex-M7-Mikrocontroller für die Systemsteuerung und Management-Aufgaben. An das CMN-600-Mesh-Netzwerk können über zwei Speichercontroller des Typs DMC-620 DDR4-3200-Speicherbausteine angeschlossen werden. Auf dem Board befinden sich zwei DDR4-RDIMMs mit 16 GB. An dem Mesh-Netzwerk hängen auch 8 MB System-Level-Cache wie auch die Speicherverwaltungseinheit MMU-600, an welche externe Beschleuniger-Hardware wie ein Xilinx-FPGA über PCIe (ein PCIe 3.0.Switch mit GbE, SATA und USB 3.0. gefinden sich auf dem Board ebenso wie 3 Standard-Erweiterungsslots mit 16, 8 und 1 Leitung) oder CCXI angeschlossen werden können. Der Cache-Coherent-Interconnect-for-Accelerators (CCIX), ausgesprochen "see six", ist eine vom CCIX-Konsortium entwickelte offene, cache-kohärente Verbindungsarchitektur. CCIX wurde entwickelt, um die Kommunikation zwischen dem zentralen Prozessor und den verschiedenen Beschleunigern im System durch eine cache-kohärente Erweiterung des Standards PCIe zu vereinfachen. Auf dem Board befindet sich ein CCIX/PCIe Gen4-Slot mit 16 Leitungen.

Ebenfalls am CMN-600 hängt ein nicht kohärenter CoreLink NIC-400 Network Interconnect, der es ermöglicht, eine AMBA-konforme Netzwerkinfrastruktur zu erstellen. Die möglichen Konfigurationen für den CoreLink NIC-400 Network Interconnect können von einer einzigen Bridge-Komponente, z.B. einer AHB-zu-AXI-Protokoll-Konvertierungsbrücke, bis hin zu einer komplexen Infrastruktur reichen, die aus bis zu 128 Mastern und 64 Slaves von AMBA-Protokollen besteht. Ein Anwendungsbeispiel ist z.B. ein FPGA als I/O-Baustein für Boot-Speicher, QSPI, eMMC, UART oder HDMI-Video. Der Plattform-Controller-Chip (PCC) verwaltet das SoC und die Board-Features und ist über I2C bzw. UART mit den beiden Cortex-M7-Controllern verbunden.

Der Open-Source-Firmware-Software-Stack beinhaltet 64-bit-Treiber, Dateisystem, Middleware, CCXI/PCIe-Treiber für Linux, den AArch64-Kernel, Hypervisor, Arm Trusted Firmware, Secure Boot, UEFI/ACPI-Port für die N1-CPUs u.a.

Jobangebote+ passend zum Thema

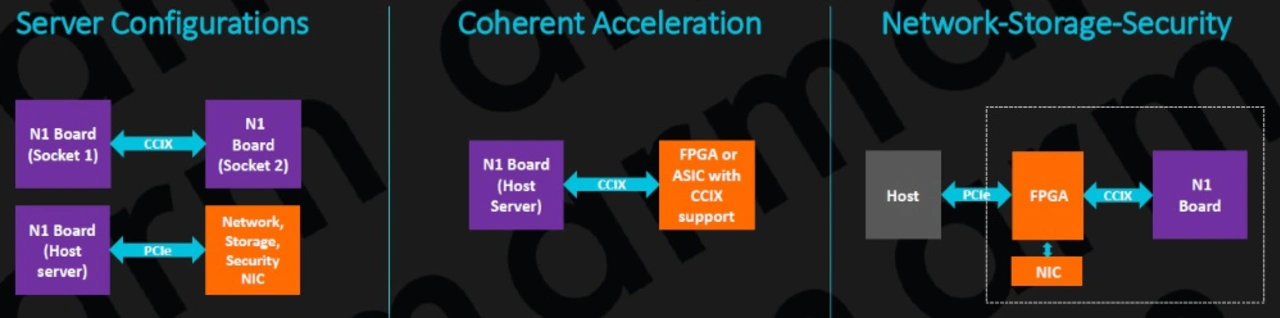

Bild 13 zeigt drei mögliche Anwendungsfälle für Prototyping, Software-Entwicklung und Performance-Evaluierung.

Als Entwicklungstools gibt es neben dem bekannten Arm-Development-Studio, das nunmehr auch einen Multi-Core/Multi-Thread-Debugger und eine Cache-Auslastungs-Analyse über die Neoverse-N1-Statistik-Erweiterungen ermöglicht, auch das Arm Allinea Studio mit speziell für High-Performance-Computing-Anwendungen entwickelte C++- und Fortran-Compiler enthält. Dazu bietet es handoptimierte Mathematik-Bibliotheken und eine skalierbare Debugging-Funktionalität und Performance-Analyse bis hin zu Supercomputer-Systemen.

- Auf in Cloud und Infrastruktur: Das ist Arms Neoverse-Universum

- Die Neoverse-E1-CPU

- Neoverse-Referenzdesigns

- Neoverse-N1-Hyperscale-Referenzdesign

- Neoverse-Entwicklungsboard

- Fazit