75 Prozent weniger Leistungsaufnahme

Neue FPGA-Familie bringt KI in die Edge

Lattice hat mit der Nexus-Plattform den ersten FD-SOI-Prozess für die Fertigung von FPGAs entwickelt, und damit die Leistungsaufnahme um 75 Prozent reduziert.

Außerdem bieten die ersten Mitglieder der neuen „CrossLink-NX“-FPGAs von Lattice eine um den Faktor 10 reduzierte Fläche und eine um den Faktor 100 höhere Zuverlässigkeit. Und was in der FPGA-Welt ebenfalls nicht selbstverständlich ist: Die ersten Chips stehen bereits zur Verfügung. »Wir wollten die CrossLink-NX-Familie ursprünglich Anfang 2020 vorstellen und sind jetzt sogar noch früher dran als geplant«, freut sich Gordon Hands, Director of Product Marketing von Lattice Semiconductor.

Ein großer Teil der reduzierten Leistungsaufnahme resultiert aus dem neuen 28-nm-FD-SOI-Prozess (Fully Depleted Silicon on Insulator), in dem Lattice die FPGAs bei Samsung fertigen lässt. Die Schwellwertspannung der FD-SOI-Transistoren ist programmierbar, so dass die Anwender die FPGAs auf hohe Leistungsfähigkeit oder geringe Leistungsaufnahme optimieren können. Das verlängert nicht nur die Batterielebenszeit, sondern spart im Betrieb Geld, wie Hands vorrechnet: »1 W schlägt im Jahr mit immerhin 1 Dollar zu Buche.« Zudem hat Lattice die Architektur der neuen CrossLink-NX-FPGAs mit deutlich mehr verteilten Speicher ausgestattet.

Jobangebote+ passend zum Thema

Das zeigt, auf welche Märkte Lattice mit den neuen FPGAs abzielt: Fabrik-Automatisierung, Industrie 4.0, Smart Building und Smart Home und allgemein IoT, wo zunehmend Machine Learning gefordert wird, ohne dazu eine Verbindung zur Cloud zu benötigen. Mit der gegenüber bisherigen FPGAs deutlich reduzierten Leistungsaufnahme und der Möglichkeit, auf hohe Performance oder geringe Energieaufnahme zu optimieren, sind dazu bereits wesentliche Schritte getan. Ein weiterer wichtiger Schritt besteht darin, dass Lattice gegenüber der bisherigen CrossLink-Architektur die 4-Input-Look-up-Tables mit einem dritten Speicherblock versehen hat. Pro Logikzelle kommen die neuen FPGAs jetzt auf eine Speicherkapazität von 170 Bit. »Das ist das höchste Verhältnis von Logik zu Speicher, das FPGAs in dieser Klasse bisher erreicht haben«, sagt Gordon Hands. Damit eignet sich die Architektur besonders, um auf ihr KI-Algorithmen abzubilden und Inferenzen in Edge-Geräten durchzuführen. Auch der große Speicheranteil auf dem Chip spart Leistung, denn es müssen nun nicht mehr große Datenmengen zwischen dem FPGA und den externen DRAMs hin- und hergeschaufelt werden. Außerdem entfallen Bedenken bezüglich des Datenschutzes, wenn die Daten von den Edge-Geräten nicht in die Cloud übertragen werden müssen sowie die Kosten für das Cloud-Computing.

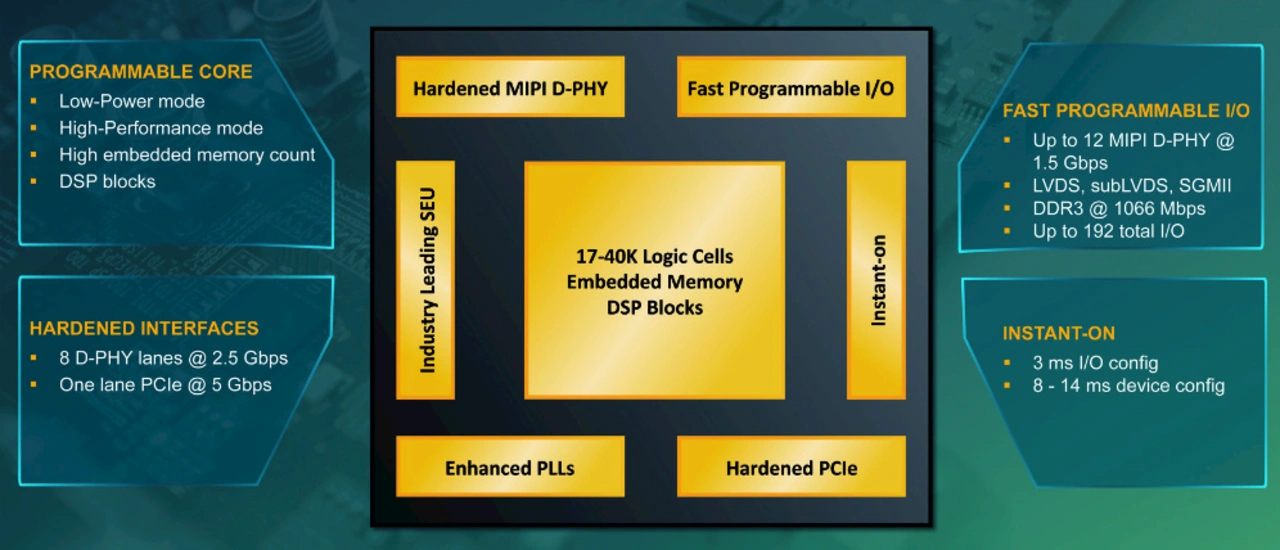

Eine weitere interessante Verbesserung besteht darin, dass sich die I/Os innerhalb von 3 ns konfigurieren lassen. Die gesamten Bausteine zu konfigurieren, dauert in Abhängigkeit von ihrer Komplexität nur 8 bis 14 ns. »Damit sind sie viel schneller als die derzeit erhältlichen SRAM-basierten FPGAs anderer Hersteller, die dazu zwischen 170 ns und fast 300 ns benötigen. Schnelle Boot-Zeiten sind aber sehr wichtig, weil die Endanwender erwarten, dass die Geräte schnell starten und weil sie anfangs flackernde Bildschirme irritieren«, sagt Gordon Hands. »Damit kommen jetzt SRAM-basierte FPGAs in den Bereich, der bisher den Flash-basierten Typen vorbehalten war. Unter anderem gelang dies dadurch, dass wir die Möglichkeiten des SPI-Interfaces voll ausgenutzt haben.«

- Neue FPGA-Familie bringt KI in die Edge

- Strahlungsfest und schnell dank FD-SOI-Prozess