Übergang von 2D- auf 3D-Architekturen

Paradigmenwechsel auf 3D-Speicher

Fortsetzung des Artikels von Teil 1

STT-MRAM-, PCM- und RRAM-Konzepte

STT-MRAM-, PCM- und RRAM-Konzepte

In den vergangenen Jahren war unter den Speicher-Experten die Ansicht verbreitet, dass in der Zukunft neue, hauptsächlich Widerstands-basierende Technologien die alten Ladungs-basierenden DRAM- und Flash-Technologien ablösen würden. Zunächst hieß es, dass PCM (phase change memory) die NOR-Flash-Technologie beerbt, und RRAM (resistive RAM) auf NAND-Flash folgt. STT-MRAM (spin-torque transfer magnetic RAM) galt als einzige Technologie, die wegen ihrer langen Standzeiten die DRAMs ersetzen könnte.

Diese Ansichten haben sich geändert. Immer mehr Experten sind überzeugt, dass die neuen Speichertechnologien zunächst in Embedded-Applikationen und in SCM-Speichersystemen zum Einsatz kommen. Ein Beispiel dafür ist STT-MRAM. Kernelement des STT-MRAM ist ein magnetischer Tunnel-Übergang mit einer dünnen dielektrischen Zwischenschicht – meist aus nur vier oder fünf Atom-Monolayern bestehend – zwischen einem magnetisch fixierten Layer und einem magnetisch freien Layer. Das Schreiben des Speicherinhalts in die Zelle besteht im Umschalten der Magnetisierung im freien magnetischen Layer.

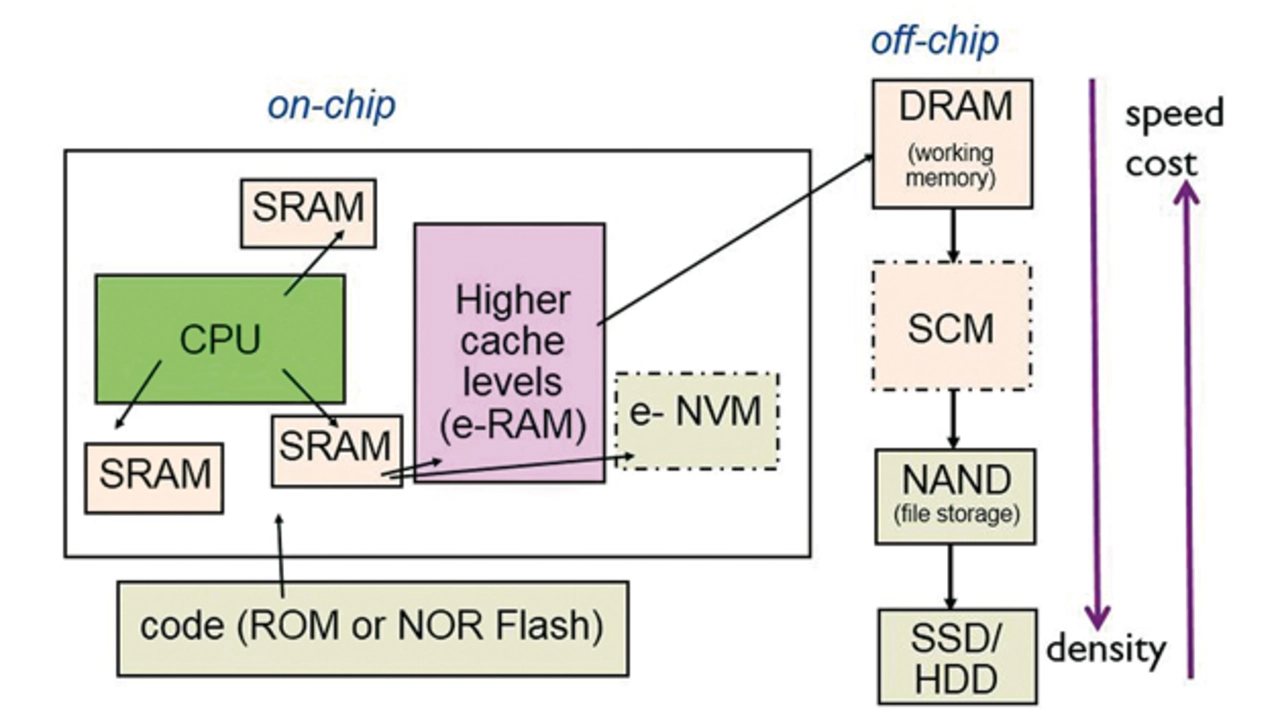

STT-MRAM ist ein viel versprechendes Speicherkonzept – wegen seines nicht-flüchtigen und schnellen Schaltverhaltens bei niedriger Spannung (<1 V) und beinahe unbegrenzter Zahl von Schreib/Lese-Zyklen. Allerdings gibt es auch einige Nachteile: STT-MRAM ist zu groß als Ersatz für Flash, und es kann (noch) nicht in 3D-Konfiguration genutzt werden. Außerdem arbeitet STT-MRAM stromgesteuert, also mit großem Leistungsbedarf beim Schreiben und mit großen peripheren Komponenten. Die Technologie könnte irgendwann die DRAMs ersetzen, doch sie kann derzeit nicht mit Low-cost-DRAMs konkurrieren. Wenn aber (3D) DRAM seine Grenzen erreicht hat und STT-MRAM sich weiter skalieren lässt, dann besteht die Möglichkeit des Ersatzes von DRAM durch MTT-MRAM. Mittelfristig dürfte STT-MRAM zunächst embedded SRAMs auf höherem Caching-Level (L3) ersetzen.

Als weitere aussichtsreiche Widerstands-basierende Technologie gilt PCM, bei der ein Chalkogenid-Material geschmolzen und rekristallisiert wird. PCM ist eine mehr oder weniger ausgereifte Technologie mit guter Standzeit (auf der Zellenebene), großem Programmierfenster und nicht-destruktivem Auslesemechanismus. PCM ermöglicht recht schnelles Schreiben bei niedrigen Spannungen. Allerdings wird PCM derzeit – wegen seiner großen erforderlichen Prgrammierleistung und Problemen der Materialstabilität – nur als Ersatz für den schrumpfenden Markt der NOR-Flash-Technologie gesehen.

Das Speicherprinzip des RRAM besteht aus der Formierung eines leitfähigen Filaments in einer ansonsten isolierenden Schicht. Typischerweise besteht ein RRAM-Element aus zwei Elektroden mit einer dünnen dielektrischen Zwischenschicht, die zum Ionentransport und als Speichemedium dient. Die Bewegung der Ionen und die strukturellen Änderungen in diesem Medium, die etwa durch ein elektrisches Feld erzeugt werden, bewirken eine messbare Änderung des Widerstandes. RRAM kommt in verschiedenen Varianten: als Oxide RAM (oder OXRAM), als CBRAM (conductive bridging RAM), und als VMCO- (vacancy modulated conductive oxide) RAM. Grundsätzlich bietet das Konzept niedrige Kosten und niedrige Spannungen, und RRAM lässt sich mit Standard-Materialien wie TaOx realisieren.

Obwohl die resistiven Schaltmechanismen exzellente Speichereigenschaften zeigen, liegt die Implementierung von hochdichten RRAM-Arrays noch in weiter Ferne – vor allem wegen des Kriechstrom-Problems. Um die Leckpfade zu schließen, ist ein nicht-lineares Selektionselement in Reihenschaltung zu jedem resistiven Schalter erforderlich, die die Speicherzelle bilden. Das ist eine der Schwächen des RRAM-Konzepts. Um mit der Flash-Technologie zu konkurrieren, müssen zwei größere Fortschritte eintreten: Die RRAMs müssen dichter werden, indem sie direkt auf echte 3D-Zellenstrukturen übergehen, also durch die vertikale Anordnung der Zellen auf dem Chip. In dieser Konfiguration ist allerdings kein Platz für den Selector. Deshalb ist ein weiterer Technologie-Durchbruch geboten: die Entwicklung eines 3D-RRAM-Konzepts ohne Selector. Doch das ist reine Zukunftsmusik. In einer ersten Entwicklungsstufe ist RRAM ein Kandidat für SCM und eNVM. Das Konzept ist somit besonders interessant für das Internet der Dinge und für Applikationen mit geringer Speicherdichte.

Weitere Newcomer

Neben diesen Ladungs- und Widerstands-basierenden Speicherkonzepten werden noch weitere Prinzipen verfolgt, um die Speicherhierarchie zu erweitern und aufzufüllen. Da wartet etwa die Ferroelektrik auf ihr Comeback in Gestalt des FeFET. Lange Zeit wurde FeFET sogar als idealer Speicher angesehen. Doch Materialprobleme mit dem Breakdown der Zwischenlayer und die schlechte Charakteristik des Datenerhalts erwiesen sich als Show-Stopper. Kürzlich wurde jedoch eine neue ferro-elektrische Phase in HfO2 – einem gut erforschten Material – entdeckt. Das hat das Interesse an dieser Speichertechnologie wieder wach gerufen.

Neben der Erforschung neuer Speicherprinzipien widmen sich die Forscher auch der Optimierung der Systemebene etwa in bezug auf SRAMs. Die Speicherhersteller betrachten diese nicht als echte Speichertechnologie, weil sie auf dem Chip in Standard-Logik-CMOS-Technologie ausgeführt sind. Andererseits wird ein Ersatz für die SRAMs gebraucht, denn sie verschlechtern sich mit jeder neuen CMOS-Technologie-Generation.

Überdies gibt es noch weitere interessante Optionen, die eine intensive Erforschung rechtfertigen. Dazu zählen ferro-elektrische Tunnel-Übergänge oder das Spin-basierende Domain-Wall-Switching. Spin-basierende Konzepte sind generell sehr attraktiv, denn sie können möglicherweise wichtige Probleme der Ladungs-basierenden Speicherkonzepte lösen, etwa die immer geringere Zahl der verfügbaren Elektronen, oder Widerstands-Speicher, die Strom-basiert sind.

Fazit: Paradigmenwechsel

Während immer neue Speicherprinzipien als Ersatz der gebräuchlichen DRAM- und Flash-Technologien für die Terabit-Ära angekündigt werden, pflegt die Industrie einen eher konservativen Ausblick und fokussiert auf die Weiterführung gut beherrschter Konzepte, obwohl die Forcierung der erforderlichen Speicherdichten auch kein einfacher Weg ist. Der noch nicht ausgereifte Status der Widerstands-basierenden Speicherkonzepte (PCM, RRAM und STT) hat deren Einführung in die Roadmap verlangsamt. Als erstes dürfte der Paradigmenwechsel von der planaren auf die 3D-Technologie eintreten, und erst dann der Übergang von Ladungs-basierenden auf Widerstands-basierende Speicher. Die Widerstands-basierenden Speicher werden außerdem zunächst in neuen Anwendungsfeldern wie SCM und embedded nichtflüchtigen Speichern erscheinen.

Jan van Houdt ist Chief Scientist bei IMEC und IEEE-Fellow.

Jobangebote+ passend zum Thema

- Paradigmenwechsel auf 3D-Speicher

- STT-MRAM-, PCM- und RRAM-Konzepte