Interview mit Marvell-CTO Zining Wu

»Neue Strukturen und Materialien lassen Moore's Law weitergehen«

Fortsetzung des Artikels von Teil 1

MoChi ist aber noch eine elektrische Schnittstelle, keine optische?

Wu: MoChi funktioniert elektrisch, allein schon aus Kostengründen. Optisch wäre viel zu teuer. Wir wollten eine sehr kosteneffektive Verbindung haben, die auch in Bezug auf die Zahl der Anschlüsse und die Leistungsaufnahme besonders effizient ist. MoChi verbindet über eine serielle Hochgeschwindigkeits-Schnittstelle direkt die Busse der einzelnen Chips in Form einer Punkt-zu-Punkt-Verbindung. Dabei müssen keine aufwändigen Protokolle abgearbeitet und übersetzt werden. Alle per MoChi verbundenen Einzelchips wirken nach außen wie ein einziges SoC.

Welche Fertigungstechnik steckt hinter MoChi? Handelt es sich um TSVs (Through Silicon Vias) oder werden die Chips beispielsweise über Bonddrähte verbunden?

Wu: Wir entwickelten MoChi so, dass sie gegenüber diesen fortschrittlichen Packaging-Techniken agnostisch ist. Alle diese Verbindungstechniken können genutzt werden. Die elektrischen Charakteristika sind so ausgelegt, dass sie eine Menge Flexibilität einräumen. Sie können das Interface über eine Leiterplatte genauso betreiben wie innerhalb eines Gehäuses, wo die Chips dicht gepackt sind und über ein Substrat mit kurzen Entfernungen miteinander kommunizieren.

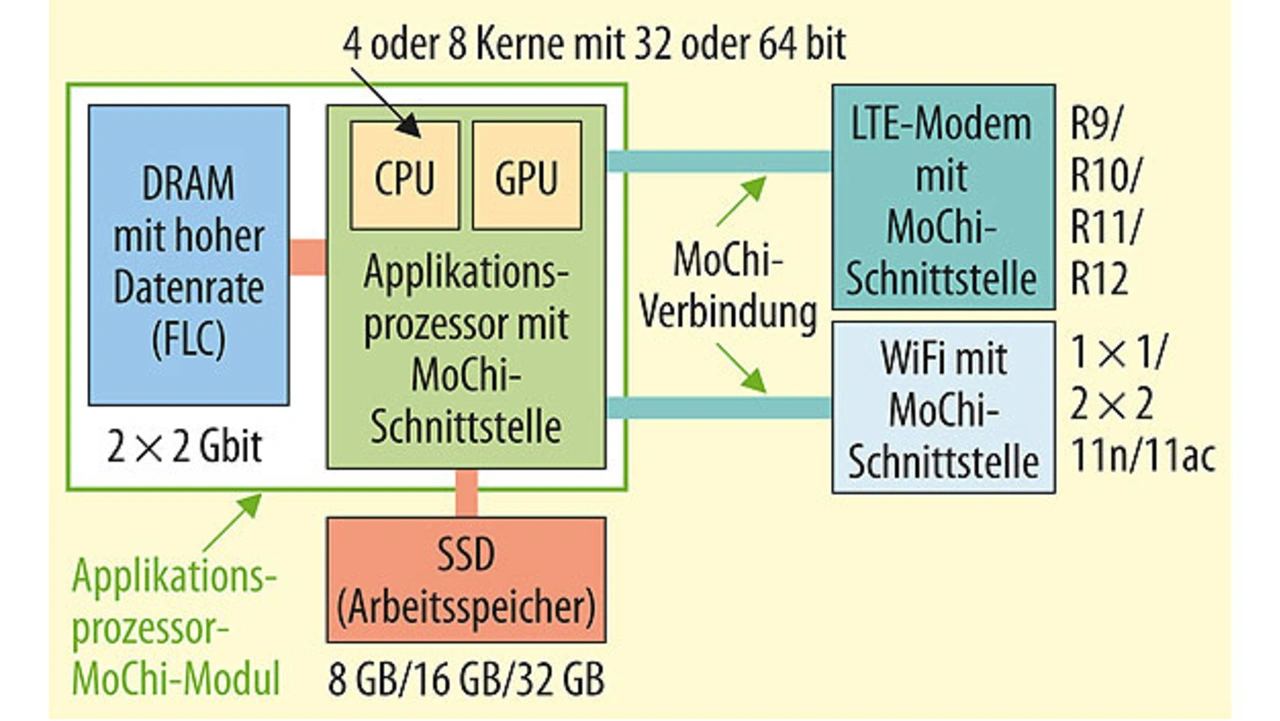

Mit MoChi können wir im Gegensatz zu komplizierten SoCs die Funktionen in wiederverwendbare Blöcke aufspalten, z.B. der CPU-Komplex wird zu einem Funktionsblock und mehrere Speicher-Peripherieschaltungen werden zu einem anderen. Weitere Funktionsblöcke umfassen Funkstandards wie WiFi oder Ethernet. Alle diese Funktionsblöcke lassen sich dann per MoChi im Daisy-Chain-Verfahren miteinander verbinden.

Wenn verschiedene Funktionen auf verschiedenen Chips implementiert werden, kann man den am besten geeigneten Halbleiterprozess für die jeweilige Funktion nutzen. Welche Rolle spielt dieser Aspekt bei MoChi?

Wu: Stimmt. Für den CPU-Komplex kann man den fortschrittlichsten Prozess wie 16 oder 14 nm FinFET nutzen, was zwar ziemlich teuer ist – aber wenn man die Leistung braucht? Jedoch für die Peripheriefunktionen wie Speicher-Controller oder WiFi kann man ältere Techniken nutzen und auch Chips wiederverwerten. Auf diese Art löst der MoChi-Ansatz die Problematik stetig steigender SoC-Kosten.

Was ist derzeit die fortschrittlichste Prozesstechnik, die Marvell nutzt?

Wu: Wir nutzen für unsere Armada-Prozessoren 16- und 14-nm-FinFET-Prozesse verschiedener Foundries.

Wann wird es kommerzielle Marvell-Produkte mit MoChi geben und für welche Anwendung?

Wu: Noch in diesem Jahr wollen wir Produkte mit MoChi auf den Markt bringen. Darunter sind Chips für den Internetzugang (Access Points), Drucker-SoCs sowie Prozessoren zur Steuerung von Speichern.

Jobangebote+ passend zum Thema

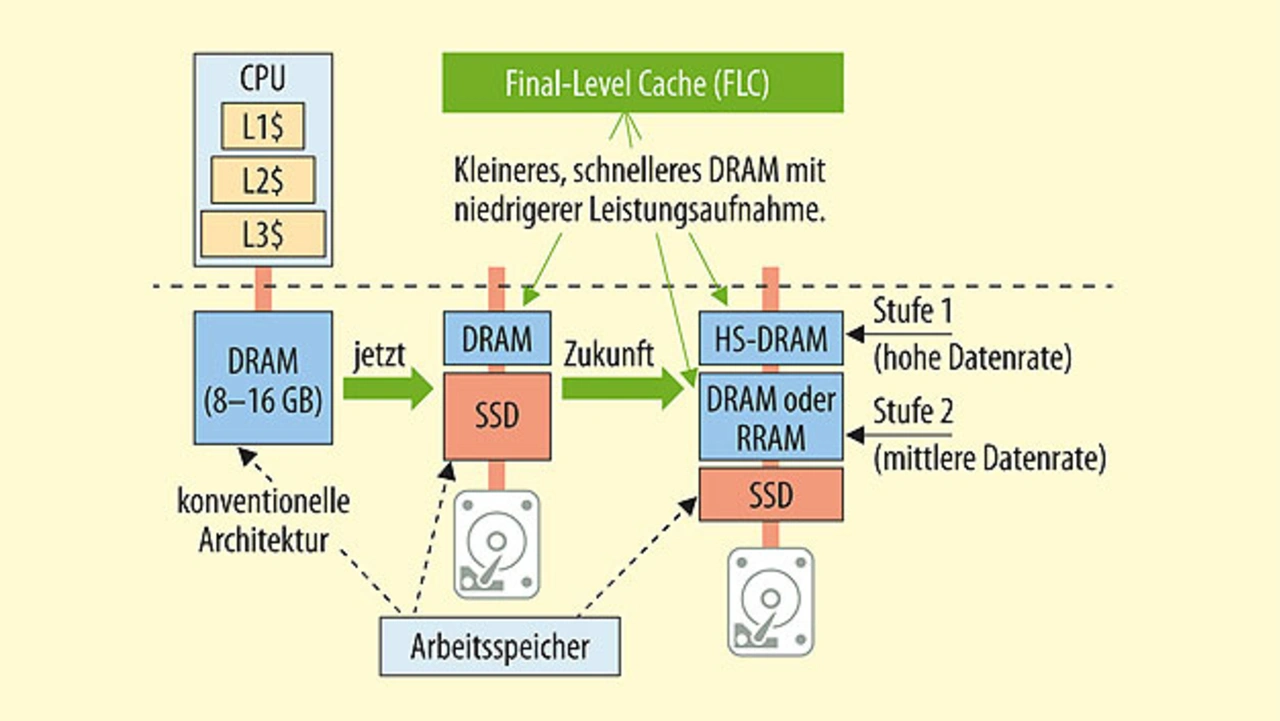

Über MoChi hinaus hat Dr. Sutardja mit der „Final Level Cache Architecture“ (FLC) auch eine neue Speicher-Hierarchie vorgeschlagen, die den klassischen Arbeitsspeicher – bestehend aus DRAMs – bis zum Faktor 10 reduzieren hilft. Was steckt dahinter?

Wu: Bei FLC handelt es sich um ein Cache-Verfahren, das eine Hardware Engine nutzt, um einen großen Cache zu verwalten. Wenn Sie sich klassische Computing-Systeme anschauen, dann werden von der CPU mehrere Cache-Ebenen – typischerweise bis zu drei – genutzt, bevor Daten aus dem Arbeitsspeicher geladen werden. Sehat Sutardja beobachtete, dass nur ein kleiner Teil von Anwendungscode im Arbeitsspeicher aktiv ist. Viele Prozesse ruhen, aber belegen Platz im DRAM. Seine Idee war nun, dass man diese inaktiven Prozesse in eine SSD (Solid State Disk) auslagern könnte, was deutlich billiger kommt. Nur die aktiven Code-Elemente werden im DRAM gehalten und der Arbeitsspeicher wird damit zum Cache der SSD.

Das heißt, dass Computersysteme künftig keine großen Arbeitsspeicher mehr brauchen?

Wu: Richtig, der Arbeitsspeicher wird durch einen im Vergleich zu typischen L1- oder L2-Caches sehr großen Cache ersetzt. Sie brauchen dann eine bestimmte Länge und Anzahl von Cache Lines. Es müssen genug Cache Lines sein, sodass kaum Cache Misses auftreten. In Software lässt sich ein solch großer Cache nicht sinnvoll verwalten. Deshalb haben wir eine Hardware Engine dafür entwickelt, die sich um die Suche, das Laden und das Löschen von Daten kümmert. So kommen wir mit einem viel kleineren DRAM aus als typische Arbeitsspeicher. Wir haben viele Tests unternommen und schaffen eine Cache-Miss-Rate von weniger als 0,1 Prozent.

Das gleiche Prinzip ist auf verschiedene Anwendungen übertragbar, beispielsweise bei der Steuerung von Massenspeichern. In Datenzentren lassen sich SSDs mit der FLC Engine als Cache für Festplattenspeicher verwenden.

Wie ist der Stand in der Entwicklung dieser FLC Engine?

Wu: Wir testen derzeit zwei Produkte in unseren Labors. Bei einem handelt es sich um ein Data-Storage-Produkt für hybride Massenspeicher, wo die SSD als Cache für Festplatten fungiert. So verhält sich eine 1-TB-Hybrid-Festplatte mit 32 GB SSD und 1-TB-Festplatte wie eine komplette 1-TB-SSD. Darüber hinaus setzen wir die FLC-Technik bei Applikationsprozessoren, z.B. in WiFi-Controllern, ein.

- »Neue Strukturen und Materialien lassen Moore's Law weitergehen«

- MoChi ist aber noch eine elektrische Schnittstelle, keine optische?