Configurable Logic Block

Komplexe diskrete Logik trifft Mikrocontroller

Der konfigurierbare Logikblock (CLB) als Peripheral in der MCU-Reihe »PIC16F13145« von Microchip ermöglicht Entwicklern, komplexe diskrete Logikfunktionen in Hardware zu implementieren, um die Stückliste zu verkleinern und anwendungsspezifische Logik zu entwickeln.

In Embedded-Systemen werden häufig diskrete Logikbausteine wie die 74HC-Serie verwendet. Der Vorteil dieser Bausteine liegt darin, dass sie unabhängig von der MCU arbeiten und viel schneller als Software reagieren können. Allerdings vergrößern diese Bausteine die Stückliste und den Platzbedarf auf der Leiterplatte.

Um diesen Nachteil zu beheben, verfügen viele MCUs von Microchip über ein Peripheral, das als Configurable Logic Cell (CLC) auf PIC-MCUs oder als Configurable Custom Logic (CCL) auf AVR-MCUs bekannt ist. Beide Peripherals implementieren eine softwaredefinierte Kundenlogik, die unabhängig von der CPU ausgeführt werden kann. Anders gesagt: Sobald die benutzerdefinierte Logikfunktion eingerichtet wurde, ist ihr Verhalten unabhängig von der MCU.

Eine Einschränkung dieser Peripherals besteht jedoch darin, dass die Menge an Logik pro Instanz sehr gering ist. Jede CLC entspricht in etwa einer einzelnen Lookup-Tabelle (LUT), während die CCL eine Instanz mit mehreren unabhängigen LUTs ist. Dennoch sind diese Peripherals leistungsstarke Tools für die Entwicklung einfacher Logikschaltungen, zum Mischen von Signalen und zur Integration mit anderer Hardware-Peripherie. So erfordern das Entprellen von Hardware-Tasten, die WS2812-Ausgabe und die Quadraturdecodierung diese Peripherals – aber wie gesagt, es gibt nur wenige davon in der MCU, was die Komplexität der Anwendungen einschränkt.

Jobangebote+ passend zum Thema

Logik-Peripheral neu definiert

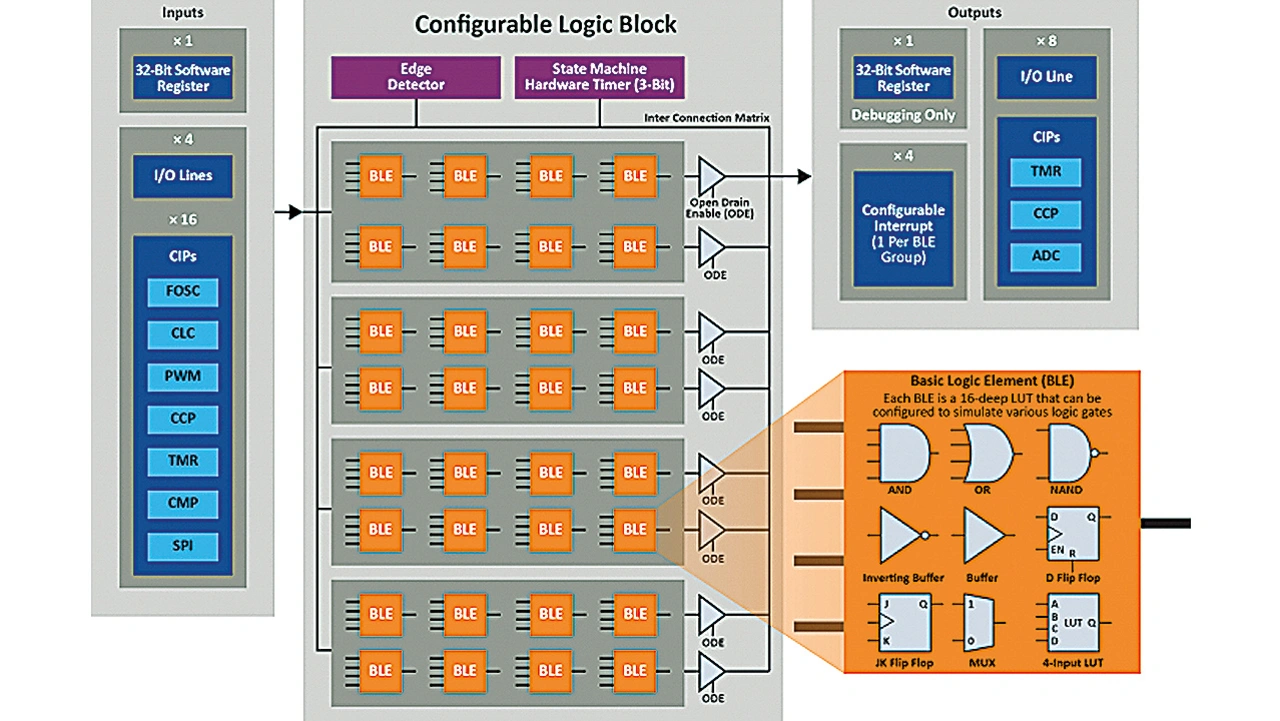

Um komplexere Anwendungen zu unterstützen, hat Microchip in seiner MCU-Reihe »PIC16F13145« ein neues Logik-Peripheral eingeführt, das als konfigurierbarer Logikblock (Configurable Logic Block, CLB) bezeichnet wird (Bild 1) und mit einem CPLD (Complex Programmable Logic Device) vergleichbar ist. Dabei gilt zu beachten, dass der CLB die CLC- oder CCL-Peripherals nicht ersetzt und dass Bausteine sowohl mit CLC/CCL(s) als auch mit einem CLB ausgestattet sein können.

Das CLB-Modul im PIC16F13145 besteht aus vier Logikgruppen mit jeweils acht BLEs (Basic Logic Elements). Die BLEs der Logikgruppen sind miteinander verbunden – jede Logikgruppe stellt zwei GPIO-Ausgänge und einen optionalen Interrupt für die CPU dar. Bei einer Betriebsspannung von 5,5 V haben die BLEs eine typische Ausbreitungszeit (Input to Output) von weniger als 6 ns. Alle BLEs teilen sich einen gemeinsamen Taktgeber, der zusammen mit einem optionalen Taktteiler per Software konfiguriert wird. Der CLB kann eine der internen Taktgeberquellen der MCU oder eine extern bereitgestellte Quelle verwenden.

Das CLB-Modul wird aus dem Speicher der MCU initialisiert und kann Pins direkt über PPS (Peripheral Pin Select) aus der Logik-Fabric selbst steuern. PPS ermöglicht dem Nutzer, die mit der Hardware-Peripherie verwendeten I/O-Pins neu zuzuweisen, um die Flexibilität beim Entwickeln zu erhöhen. Wenn beispielsweise der RA1-Pin für den SPI-Takt (Serial Peripheral Interface) verwendet wurde und es vorteilhafter wäre, RA6 zu verwenden, kann PPS den Pin neu zuweisen.

Zu den weiteren Elementen des CLB gehören ein dedizierter 3-bit-Hardware-Timer (mit decodierten Ausgängen), ein Flankendetektor für Eingangssignale und ein 32-bit-Ausgangsregister (für Debugging-Zwecke). Weitere CIPs (Core Independent Peripherals) des Mikrocontrollers können für komplexere Designs als Eingänge für den CLB verwendet werden

CLB-Synthesizer für die Konfiguration

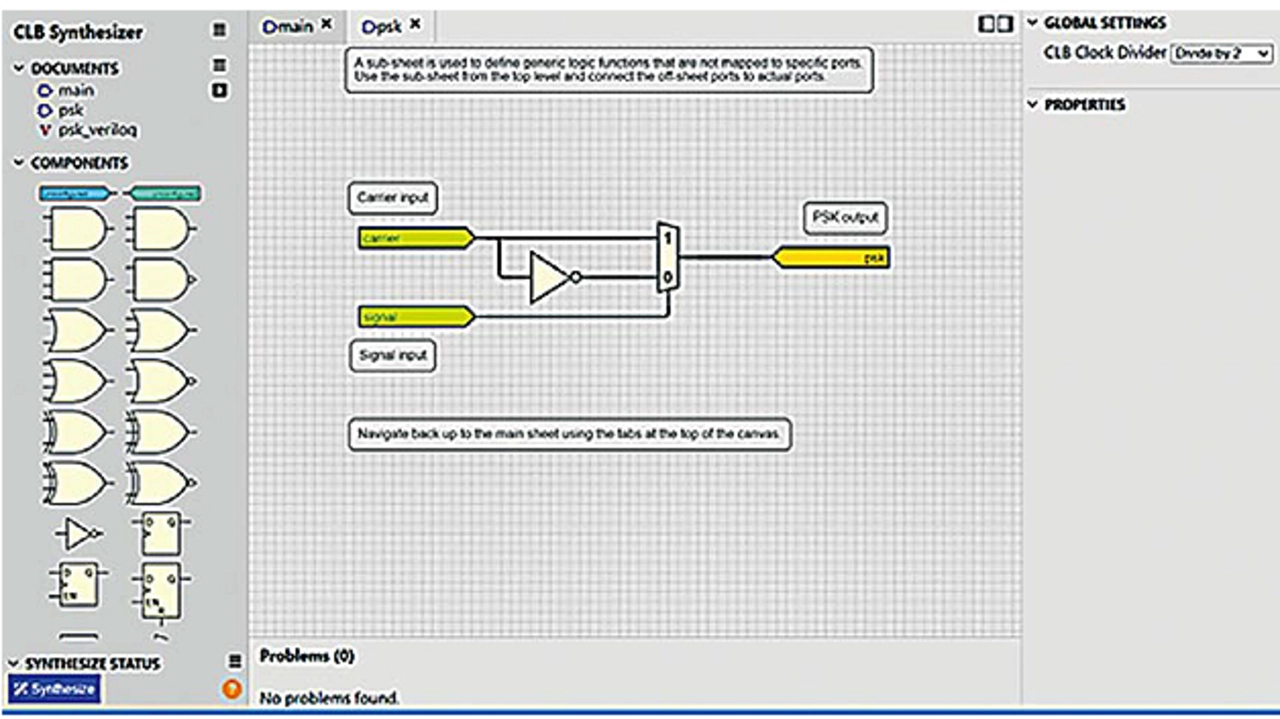

Da das CLB-Modul wesentlich komplexer ist als CLC- oder CCL-Elemente, wurde ein neues Tool entwickelt. Der »CLB-Synthesizer« bietet eine grafische Oberfläche zur Konfiguration der Logik (Bild 2). Neben Logikgrundelementen unterstützt das Tool auch Bibliotheken mit Logikblöcken höherer Ebene, die bereits vorhanden sind oder vom Benutzer selbst erstellt werden können.

Bei der Interaktion mit dem grafischen Tool wird im Hintergrund ein Verilog-Modul für die Synthese generiert. Möchten Entwickler lieber ihr eigenes Verilog schreiben oder haben sie bereits eine fertige Datei, lässt sich diese direkt als Modul in das Tool importierten.

Die Ausgabe des CLB-Synthesizers ist eine Assembly-Datei, die den Bitstream zum Einrichten des CLB und etwas Quellcode zur Konfiguration des CLB als Peripherie enthält. Dieses Tool kann über den MPLAB Code Configurator (MCC) oder über ein eigenständiges Online-Tool ausgeführt werden. Der MCC ist ein Dienstprogramm zur Codeerzeugung, mit dem Entwickler die Peripherie im Mikrocontroller über eine visuelle Schnittstelle einrichten und konfigurieren können. Nach der Konfiguration der Hardware-Peripherie generiert der MCC einen Initialisierungscode und eine Device-API.

Zur Laufzeit wird der CLB-Bitstream mithilfe der integrierten Hardware direkt aus dem Programmspeicher geladen. Ein Vorteil dabei ist, dass der Ladevorgang mit einem anderen, im Bausteinspeicher abgelegten Bitstream wiederholt werden kann, wenn die CLB-Konfiguration während der Programmausführung geändert werden muss.

CLB in der praktischen Anwendung

Um den CLB in Anwendungen zu demonstrieren, wurden Anwendungsbeispiele erstellt. Nachfolgend werden zwei Beispiele vorgestellt: ein 7-Segment-Displaykonverter und ein SPI-to-WS2812-Konverter. Diese Beispiele sind Bausteine, die kopiert und als Teil einer Komplettlösung verwendet werden können. Sie sollen die Nützlichkeit dieser Peripherie und ihren Beitrag zu einem Design demonstrieren.

7-Segment-Displaykonverter

7-Segment-Displays können über die normalen I/Os angesteuert werden, wobei eine Standardimplementierung typischerweise eine softwaredefinierte Lookup-Tabelle benötigt, um die Eingangszahl in das korrekte Ausgabemuster für das Display umzuwandeln. Hierbei fungiert der CLB als Hardware-Lookup-Tabelle. Das gewünschte Ausgabesymbol (0 bis F) wird von der Software in das CLB-Eingaberegister geladen. Jedes Ausgabesegment der Anzeige wird von einer LUT gesteuert, die die Eingaben den Ausgaben zuordnet.

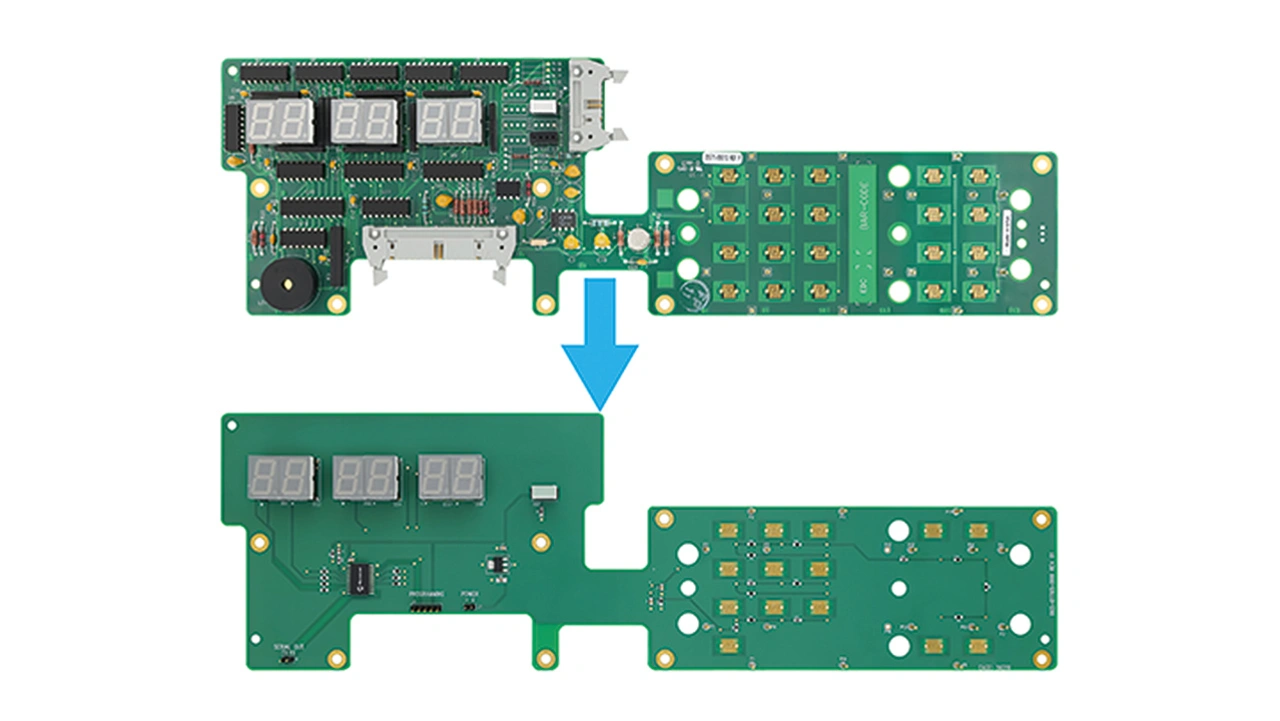

Dieses Beispiel wurde intern für eine neue Steuerplatine für ein Zeitmesssystem verwendet. Die ursprüngliche Benutzeroberfläche wurde in den 1980er-Jahren mit Logik der 74HC-Serie entwickelt. Mit dem CLB kann eine einzelne 20-polige MCU die auf der Platine vorhandene Anzeige- und Tastaturlogik implementieren, was die Stückliste erheblich reduziert. Ein Vergleich der beiden Platinen ist in Bild 3 dargestellt.

SPI-to-WS2812-Konverter

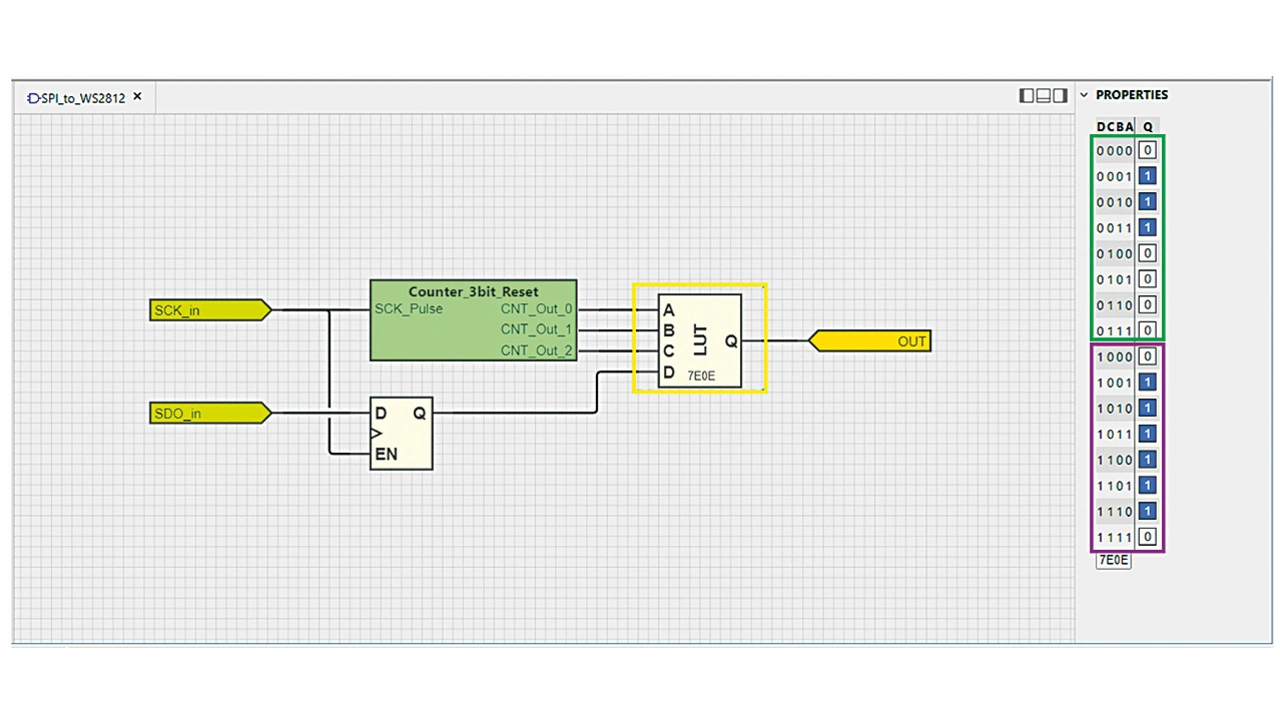

WS2812 ist ein serielles 1-Draht-Protokoll zur Steuerung von LED-Arrays mit Pulsweitenmodulation (PWM). Dabei wird die SPI-Hardware als Schieberegister für die an die LEDs zu sendenden Daten verwendet, während der CLB »SCLK« und »SDO« in die erwartete Ausgabe umwandelt.

Hier wird dies mithilfe eines mono-getriggerten 3-bit-Zählers, eines D-Latch mit Enable und einer 4-Eingangs-LUT umgesetzt (Bild 4). Entscheidend bei der Implementierung sind die Taktquellen für SPI und CLB. Der SPI-Taktgeber ist auf (Leerlauf) HIGH eingestellt, ändert seinen Zustand bei steigender Flanke und läuft mit einer Frequenz von 800 kHz (Ausgang des WS2812), während der CLB-Taktgeber mit der 10-fachen Geschwindigkeit (8 MHz) läuft. Wenn SCLK auf LOW ist, wird der 3-bit-Zähler ausgelöst und beginnt zu zählen. Erreicht der 3-bit-Zähler 7 (0b111), stoppt er und bleibt bis zur nächsten niedrigen Periode des Taktimpulses auf 0.

Der Ausgang des Zählers wird zusammen mit einer zwischengespeicherten Version der Ausgangsdaten in eine LUT mit vier Eingängen eingespeist. Dadurch wird das Ausgabemuster der Daten festgelegt, das auf der rechten Seite in Bild 4 zu sehen ist. Nach dem Zurücksetzen des Zählers bleibt der Zählerausgang auf 0, um den Zyklus abzuschließen. Anschließend wird bei Bedarf das nächste Byte in der SPI-Hardware übertragen, wodurch der Zyklus wiederholt wird.

Beide Beispiele zeigen die Vorteile diskreter Logik innerhalb einer MCU. Die Hardware-Peripherie entlastet die CPU, was die Reaktionszeit und den Stromverbrauch verbessert sowie die Anzahl der benötigten Bauteile reduziert. Der CLB ermöglicht komplexe Anwendungen, die bisher nicht in einer MCU implementiert werden konnten. Derzeit ist der CLB in den MCUs der Serie PIC16F13145 über Microchip Direct oder andere Distributoren erhältlich.

Der Autor

Robert Perkel

ist Application Engineer bei Microchip Technology. In dieser Funktion stellt er technische Inhalte wie Anwendungshinweise, Fachartikel und Videos bereit. Er ist außerdem für die Analyse von Anwendungen für Peripherie und die Entwicklung von Codebeispielen und Demos zuständig. Perkel hält einen Bachelor of Science in Computer Engineering von der Virginia Tech.