Neuer Atom - Hop oder Top?

Eintauchen in Intels Apollo Lake

Fortsetzung des Artikels von Teil 1

Schnellerer Speicher – aber Achtung

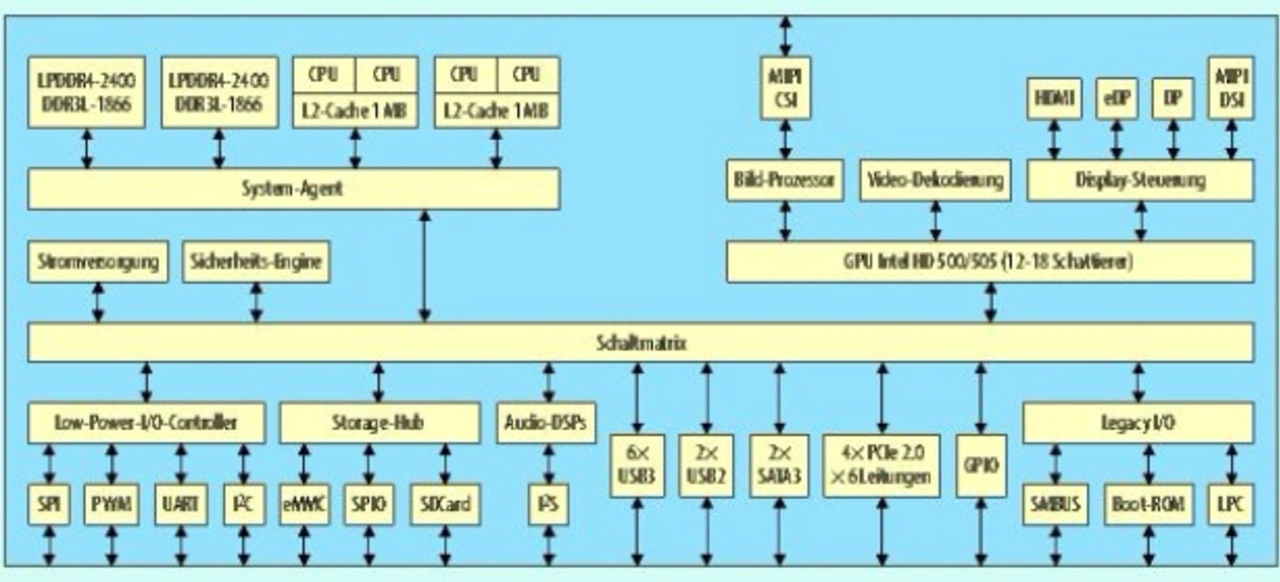

Wie im Blockdiagramm (Bild) ersichtlich, enthalten die neuen CPUs zahlreiche I/O-Schnittstellen. Eine Verbesserung gegenüber der Vorgängergeneration »Bay-Trail« sind die vier 32-bit-Kanäle zu LPDDR4-2400-Speicher, die mit bis zu 2400 Mio. Transfers/s eine maximale Bandbreite von 38,4 GB/s aufweisen. Bay-Trail hingegen hat lediglich eine zweikanalige 64-bit-Schnittstelle zu DDR3L-1333-Speicher bei maximal 1333 Mio. Transfers/s, was einer Bandbreite von 21,3 GB/s entspricht. Doch bevor das große Frohlocken über eine fast verdoppelte maximale Speicherbandbreite einsetzt, muss folgendes angemerkt werden: Die fehlererkennenden und -korrigierenden Codes (ECC) arbeiten nur mit DDR3L-Speicher. Immerhin wird jetzt auch DDR3L-1866 unterstützt, was 40 % schneller als zuvor ist. Aber die beworbenen 38,4 GB/s über LPDDR4 sind mit ECC eben nicht möglich.

Über die Mikroarchitektur der Goldmont-CPU breitet Intel offiziell den Mantel des Schweigens. Je zwei CPUs teilen sich 1 MB L2-Cache, d. h. die Quad-Core-Modelle haben in Summe 2 MB L2-Cache (Bild). Unseren Informationen zufolge handelt es sich um eine zwölf bis 14 Stufen umfassene superskalare Pipeline mit drei Befehlsdecodern, die drei Befehle pro Taktzyklus decodieren können. Der Microcode-Sequenzer kann pro Taktzyklus drei µOPs zu den Reservationstations schicken, die Retirementeinheit unterstützt maximal drei Instruktionen pro Taktzyklus. Verbesserungen gibt es bei der Sprungvorhersage, welche die Fetch-Pipeline von den Befehlsdecodern entkoppelt. Das Out-of-Order-Fenster sowie die zugehörigen Puffer wurden vergrößert, um die Out-of-Order-Befehlsausführung über Integer, Gleitkommer/SIMD und Speicherbefehle zu optimieren.

Goldmont kann im Gegensatz zu Silvermont, wo pro Taktzyklus nur ein Lade- oder ein Speicherbefehl abgearbeitet werden kann, pro Taktzyklus einen Lade- und einen Speicherbefehl ausführen. Die Pipeline im Backend für Speicherinstruktionen enthält zudem einen 2nd-Level-TLB mit 512 Einträgen für 4 KB große Speicherseiten.

Die Ausführungseinheiten für Integerbefehle haben drei Pipelines und können damit bis zu drei einfache ALU-Instruktionen pro Taktzyklus ausführen. Die SIMD-Befehle werden in einer 128 bit breiten Ausführungseinheit verarbeitet. Der Durchsatz und die Latenzzeiten wurden z. T. dramatisch verbessert, so benötigt z. B. PSHUFB statt fünf Taktzyklen wie bei Silvermont nur noch einen Taktzyklus. Bei zahlreichen anderen SIMD-Befehlen konnte der Durchsatz verdoppelt werden.

Neben den neuen Befehlen für SHA1- und SHA256-Hashing wurden Durchsatz und Latenzzeiten von Instruktionen für Verschlüsselung/Entschlüsselung (AES) und eine Multiplikation ohne Carry-Bit (PCMULQDQ) verbessert. Last, but not least wurde die Latenzzeit des PAUSE-Befehls für eine höhere Energieeffizienz verringert.

Bemerkenswert ist beim Schrumpfen der Fertigungsgeometrie von 22 nm auf 14 nm, dass Intel die Basisfrequenz der CPUs nicht angehoben, sondern gesenkt hat: Aus 1,3 bis 1,9 MHz (E3800) wurden 1,3 bis nur noch 1,6 MHz bei identischer Core-Anzahl. Allerdings hatten die E3800 keinen Burst-Modus und der E3900 kann temporär bis auf 1,8 GHz oder sogar 2.0 GHz hochgetaktet werden (siehe Tabelle).

In Summe kommt laut Intel der E3930 mit dem Burst-Mode, höhere IPC und schnelleren Speicher auf einen um 70 % höheren SPECint-Benchmark-Wert als der E3825. Allerdings nutzt der SPECint nur einen Core und kann unbegrenzt im Burst-Mode bleiben, was aus thermischen Gesichtspunkten bei einem deaktivierten zweiten Core möglich ist. Stehen beide Cores (und die GPU) unter Volllast, wird die Verbesserung deutlich geringer ausfallen als diese 70 %.

Jobangebote+ passend zum Thema

- Eintauchen in Intels Apollo Lake

- Schnellerer Speicher – aber Achtung

- Quantensprung bei GPU

- Apollo-Lake im IoT – es gibt Grenzen