System-on-Chip-Design

Powerline-Netzwerk-SoCs korrekt verifizieren

Fortsetzung des Artikels von Teil 1

Verifizierung der IP-Connectivity

Die erste Aufgabe ist die Validierung der grundlegenden Verbindungen zwischen den IPs und der Peripherie der jeweiligen Konfiguration. Dies scheint auf den ersten Blick keine große Herausforderung zu sein. Allerdings enthält unser SoC mehrere Low-Power-, BIST- und andere Konfigurationsmodi, welche die Steuersignale und Datenpfade beeinflussen und/oder multiplexen, bevor die kundenspezifische Anpassung überhaupt zum Tragen kommt. Wird dies alles berücksichtigt, dann sind zehntausende Verbindungen mit 100 % Genauigkeit zu verifizieren. Dies kann selbst eine bestens organisierte Person manuell nicht überprüfen.

Anfänglich verließ sich das Team auf eine detaillierte manuelle Inspektion plus C-basierter Simulations-Testbenches und einer Signalanalyse mittels Waveform. Allerdings wurde bald klar, dass diese Methodik in der Vergangenheit zwar funktionierte, doch dieses Design der nächsten Generation benötigte mit einer Vielzahl von Peripherals einen gründlicheren Ansatz.

Natürlich hatten die Entwickler auch die formale Verifikation als eine mögliche Lösung betrachtet und mit der "SoC Connectivity App" ein Produkt gefunden, das auf dem formalen Tool "Cadence Incisive Formal Verifier" läuft. Im Prinzip nutzt diese App eine rein Text-basierte Excel-Kalkulationstabelle zur Erfassung der Verbindungsspezifikation. Daraus erstellt die App automatisch die entsprechenden Assertions und startet das formale Tool. Im Fehlerfall werden Gegenbeispiele erzeugt, die unmittelbar die Fehlerursache hervorheben.

Mit Hilfe dieser App konnten die Chipdesigner rasch neue IP-Konfigurationen innerhalb weniger Stunden verifizieren, während dies mit dem simulationsbasierten Prozess bisher einige Wochen dauerte.

Im Zuge der Verifikation fanden wir eine falsche Verbindung auf der TX- und RX-Leitung zum UART-Block. Die Ports waren mit dem gleichen GPIO verbunden und nicht jeweils mit TX und RX. Dieser Fehler wurde nicht mit der funktionellen Simulation entdeckt, wo das UART per Loopback eingebunden wird.

AMBA-Protokoll-Verifikation

Der ARM-AMBA-Bus ist eine zentrale Lebensader des SoCs, und da die Anzahl der Peripherie zunimmt, steigt gleichzeitig die Komplexität der AMBA-Implementierung. Überdies waren einige an den internen Bus angeschlossene IPs selbst sehr komplex – sie ermöglichen viele Betriebs- und Low-Power-Modi, um den Kunden vielfältige Anwendungsmöglichkeiten anbieten zu können.

Auf Grund positiver Erfahrungen mit einer umfassenden formalen Verifikation mit Hilfe der SoC-Connectivity-App wurde das SoC-Team ermutigt, eine Assertion-basierende Verifikations-IP (ABVIP) für das AMBA-Protokoll zu nutzen. Dies ist eine Bibliothek von SVA/PSL-Assertions, welche die AMBA-Protokollregeln beschreiben, so dass sich die Schnittstelle unserer IPs zum AMBA-Bus mittels formaler oder dynamischer Simulationswerkzeuge auf Fehler überprüfen lässt.

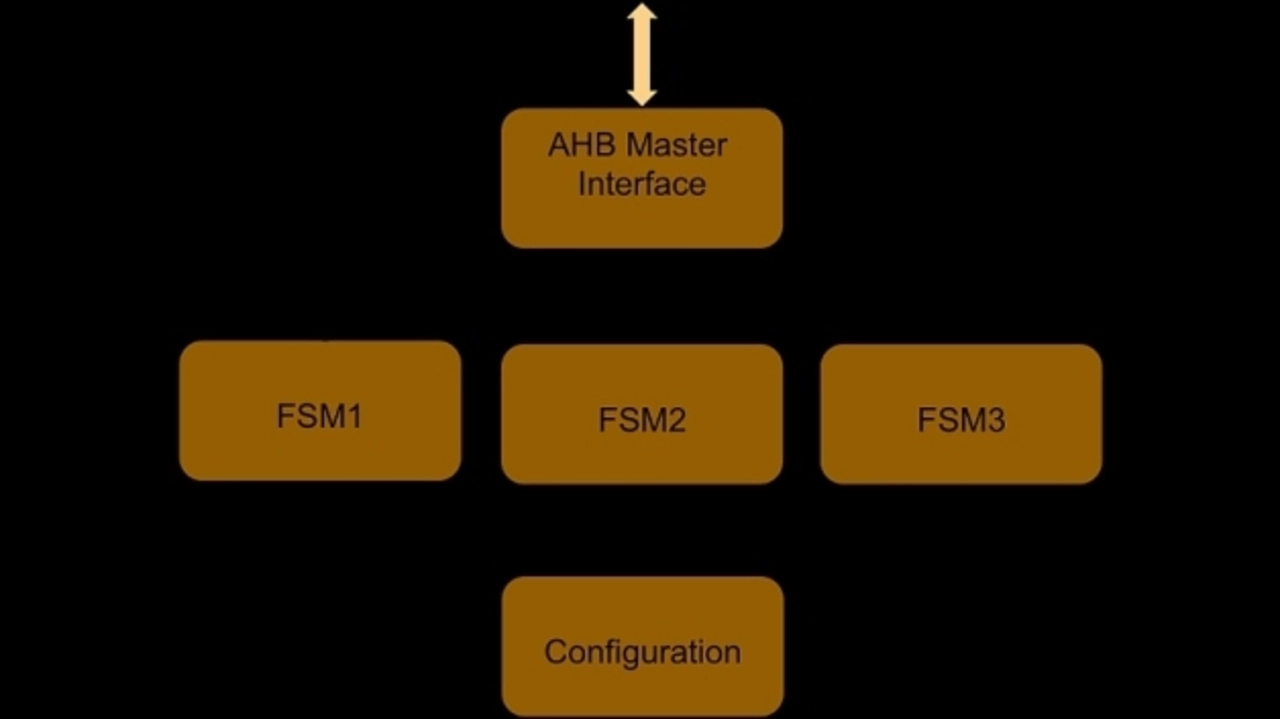

Die Chipdesigner nutzten eine formale Analyse zur Überprüfung der AHB-Master-Schnittstelle, da die Master-Port-Verifikation eine bekannte, eindeutige Stärke der formalen Analyse ist. Das nachfolgende spezifische Beispiel verdeutlicht dieses Vorgehen:

Einige Peripheriefunktionen des SoCs verfügen neben den üblichen Slave-Schnittstellen auch über AMBA-Master-Schnittstellen. Einige dieser Master können auch über mehr als zwei embedded DMA-Controller verfügen, was die Verifikationsherausforderungen noch erhöht. Bild 2 zeigt ein vereinfachtes Blockdiagramm der verifizierten AHB-Master-Schnittstelle. Es wird durch drei FSMs gebildet, die AHB-Transaktionen generieren können. Diese lassen sich über Register konfigurieren, auf die ein Zugriff über AHB-Slave-Schnittstellen möglich ist. Dieser Block wurde aus dem vollständigen IP extrahiert, wobei einige Konfigurationen durch Assume-Konstrukte eingeschränkt sind.

Wie bereits angedeutet, können zahlreiche Slave-Peripherien am Bus angeschlossen sein, um unterschiedliche Produktderivate zu erlauben. Zu unserer Überraschung hatten wir bei der Ausführung der formalen Analyse mit dem ABV-IP einige Fehler in unseren eigentlich ausgereiften Peripherien entdeckt. Diese IP wurde bereits früher durch Simulation überprüft und war in anderen Designs schon im Einsatz.

Im Zuge eines Projekts fand das Team sieben Verstöße gegen das AMBA-Protokoll. Einige der Fehler waren unkritisch, so dass die Robustheit des AMBA-Protokolls deren Auswirkungen minimierte. Andere Fehler waren dagegen umgehend zu beheben, da sie Probleme in den fertigen Produkten verursacht hätten.

Verbesserte Produktivität des Designteams

Seit dem erfolgreichen Einsatz dieser Methodik im ersten Projekt hatte das SoC-Team ein erfolgreiches Tapeout mehrerer Produkte mit diesem Flow erreicht. Immer waren die Ergebnisse dieser Halbleiter-Validierung perfekt. Dieser Design-Flow darf also als wertvoller Beitrag betrachtet werden, um die Produktivität des Teams steigern zu können.

Jobangebote+ passend zum Thema

- Powerline-Netzwerk-SoCs korrekt verifizieren

- Verifizierung der IP-Connectivity