Der schwierige Weg zum fertigen Chip

Fallstricke bei der Auswahl einer FPGA-basierten Prototyping-Lösung vermeiden

Fortsetzung des Artikels von Teil 2

Designflow von RTL bis zum FPGA-Prototypen glätten

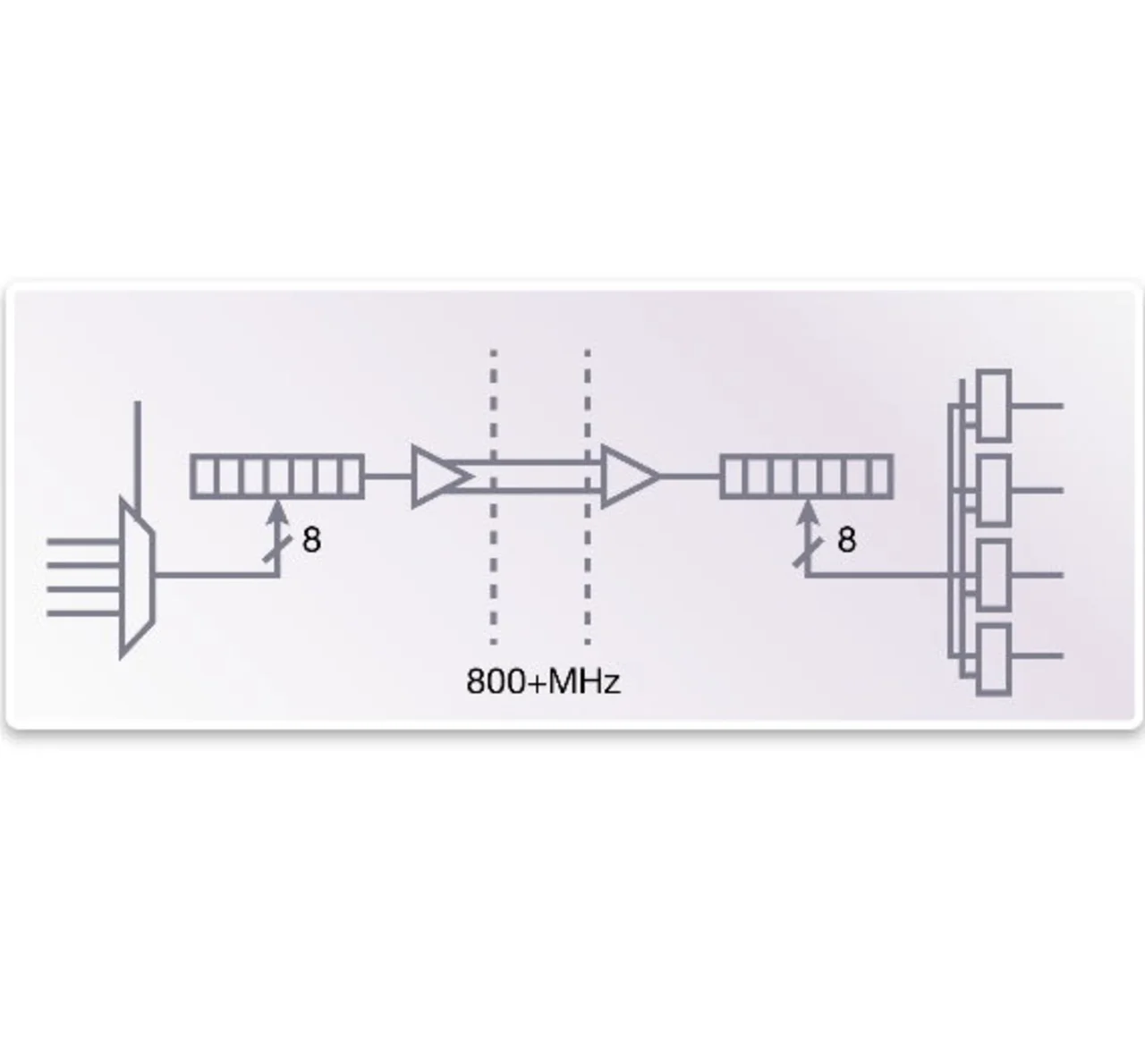

Wie oben erwähnt ist es auch wichtig, eine Lösung zu finden, die dabei hilft, den Designflow von den RTL-Dateien hin zum FPGA-Prototypen zu glätten. Dies ist besonders wichtig für große Designs, die auf Lösungen mit mehreren FPGAs angewiesen sind, weil das Design hierfür partitioniert werden muss. Es kommt darauf an, Hardware mit flexiblen Routing-Konfigurationen zwischen FPGAs zu wählen, wie sie das HAPS-System von Synopsys bietet. Fest definierte Verbindungen zwischen FPGAs schränken die Optionen des Partitionierungstools für das Routing ein, wodurch sich hohe Signal-Multiplex-Faktoren ergeben, die die Performanz verringern. Viele Designs, die auf mehrere FPGAs verteilt werden, erfordern mehr Routing-Ressourcen als irgendeine Lösung physikalisch bietet. Hier kommt integrierte Software ins Spiel. Entwickler benötigen ein Tool, das nicht nur die Umformung von Designs hinsichtlich Gated-Clocks oder Embedded-Memories handhaben kann, sondern auch die Partitionierung unter Beibehaltung der endgültigen Hardware-Performanz vereinfacht. Im Gegensatz zu herkömmlichem Pin-Multiplex ermöglichen Techniken wie High-Speed-Time-Division-Multiplexing (HSTDM) die Partitionierung eines Designs ohne bzw. mit nur geringem Performanzverlust.

Nicht zu vergessen ist auch die Unterstützung von IP wie beispielsweise der populären DesignWare-IP. Sicherzustellen, dass die mitgelieferte Software diese IP automatisch verarbeiten kann und die IP auf dem System einsatzbereit ist, sind wichtige Überlegungen, ebenso die Verfügbarkeit einer umfangreichen Liste von Schnittstellen-Tochterkarten. Das Ziel besteht darin, das System so akkurat wie möglich zu modellieren. Die Verwendung derselben IP sowohl im Prototypen als auch im Original-RTL-Code trägt zur Minimierung von Prototyping-Diskrepanzen bei.

Die Nutzbarkeit des FPGA-Prototypen zu einem früheren Zeitpunkt innerhalb des Designflows führt typischerweise zu einem größeren Vertrauen in die Validierung, weil damit umfassendere Tests möglich sind. Co-Simulation, transaktionsbasierte Verifikation, Standard-Co-Emulation-Modeling-Interface (SCE-MI) und weitere fortschrittliche Modi machen den FPGA-Prototypen einsetzbar für verschiedene Szenarien und wiederverwendbar über mehrere Projekte hinweg. Die Schaffung einer hybriden Umgebung, die virtuelle und FPGA-Prototypen mischen kann, löst gewöhnlich das Problem des fehlenden TLM-Modells für das Systemteam und verbessert die Software-Umgebung für die Hardware-Validierungsteams. Wichtig ist auch die Simulator-Integration, weil Anwender damit ihre bestehenden Simulationsumgebungen und Testbenches nutzen können, um den Prototypen schneller einsatzbereit zu machen. Praktisch ist die Möglichkeit der Fernverwaltung für den Fall, dass Unterstützung für mehrere Teams, beispielsweise ein Hardware- und ein Softwareteam, erforderlich sein sollte.

Schließlich, und das ist vielleicht der wichtigste Aspekt, sollten Anwender eine Lösung anstreben, die das Design-Debugging unterstützt und sie nicht mit “Black Boxes” auf dem Board im Dunkeln lässt. Debug-Funktionen werden benötigt, um die Quellen von Fehlern zu identifizieren, je schneller desto besser. Eine Lösung zu finden, die die Rückverfolgung von Fehlern vom FPGA-Prototypen direkt zum RTL-Code erlaubt, ermöglicht ein rasches Debugging des Designs in einer geläufigen Umgebung.

Heutzutage gibt es auf dem Markt neue Technologien, die all diese Faktoren adressieren, aber lediglich einige wenige Hauptanbieter sind in der Lage, sowohl aktuelle als auch künftige Projekte zu unterstützen. Der Erwerb einer Komplettlösung, die die Prototyping-Hardware und den unterstützenden Software-Tool-Flow beinhaltet und fortschrittliche Funktionen bietet, die einen High-Performance-Betrieb nahe an der Realität erlauben, schafft eine leistungsfähige Basis für einen frühzeitigen Projekterfolg. Wenn es um die Auswahl einer geeigneten FPGA-Prototyping-Lösung geht, müssen sich die Anwender an gewisse Richtlinien halten, jedoch kann die Befolgung dieser Richtlinien den Auswahlprozess beschleunigen.

Mick Posner ist Product Marketing Manager für das FPGA-based Prototyping beim EDA-Spezialist Synopsys

Jobangebote+ passend zum Thema

- Fallstricke bei der Auswahl einer FPGA-basierten Prototyping-Lösung vermeiden

- Eigenbau ist nicht die beste Lösung

- Designflow von RTL bis zum FPGA-Prototypen glätten