Ursachen von Jitterproblemen

Praktische Tipps gegen Taktjitter für Sigma-Delta-ADUs

Fortsetzung des Artikels von Teil 1

Übersprechen aus anderen Signalquellen

Eine weitere Jitterquelle sind Taktstörungen, die von externen Leitungen stammen. Sind auf der Leiterplatte die Leitungen von der Taktquelle nahe zu Signalleiterbahnen – die einkoppeln können –platziert, kann es verheerende Auswirkungen auf die Leistungsfähigkeit haben.

Ist das Störsignal unabhängig vom Betrieb des AD-Umsetzers – und zufällig – kann es den Jitter-Anteil ziemlich stark erhöhen. Wird das Taktsignal durch digitale Signale des AD-Umsetzers gestört, lassen sich Störspitzen erkennen. Für Slave-AD-Umsetzer können die CLK- und SPI-Leitungen unabhängig vom Takt sein. Dies kann aber bei Frequenzen, die der ersten Nyquist-Zone zugeordnet sind, Probleme hervorrufen (Gleichung 1).

Es ist ratsam frequenzstarr gekoppelte Quellen für SPI und MCLK (Master Clock) zu verwenden. Allerdings können selbst mit dieser Vorsichtsmaßnahme SPI und MCLK Störungen aufweisen, die mit dem Tastverhältnis eines vorgegebenen Takts zusammenhängen.

Wenn der AD-Umsetzer z.B. durch 128 teilt und SPI nur 24 bit liest, verursacht dies das Risiko eine Überlagerungsfrequenz zu erzeugen, die speziell mit den 1/(24t) und 1/(104t)-Messwerten zusammenhängt. Deshalb sollten MCLK-Leitungen von den Leiterbahnen für SPI und auch von anderen Datenleitungen entfernt geführt werden.

Jobangebote+ passend zum Thema

Schnittstellen und weitere Takte

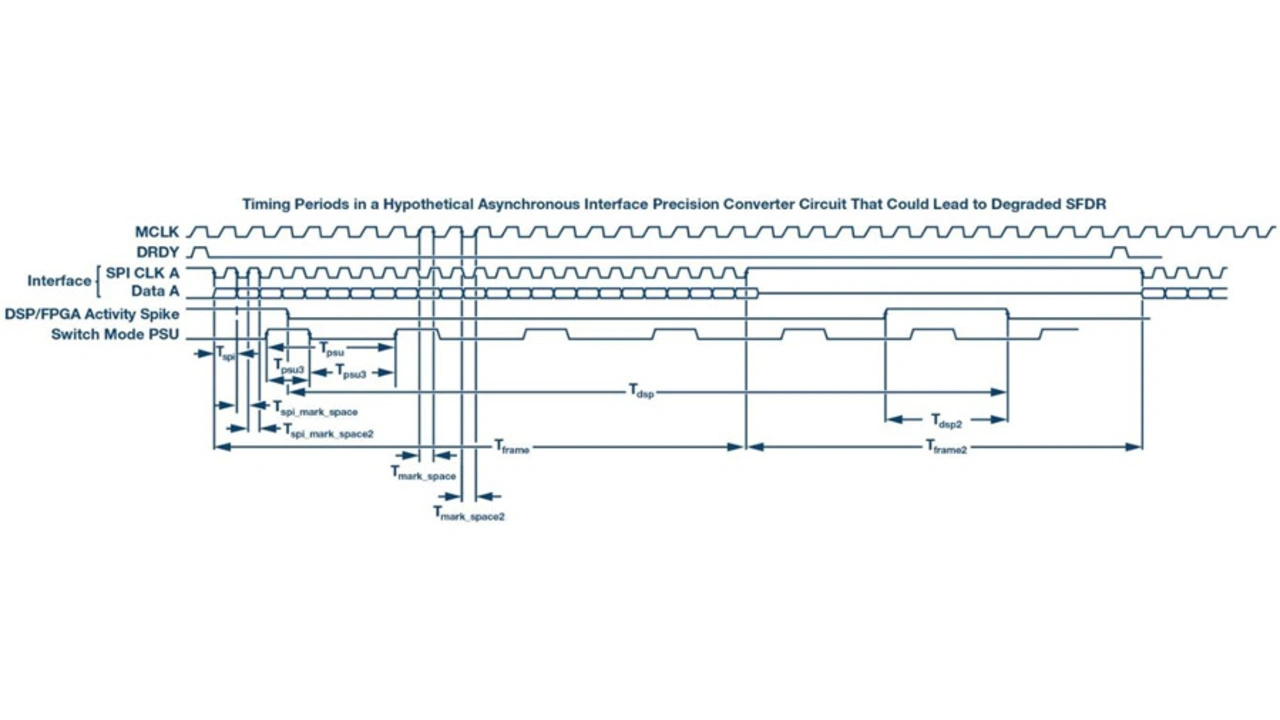

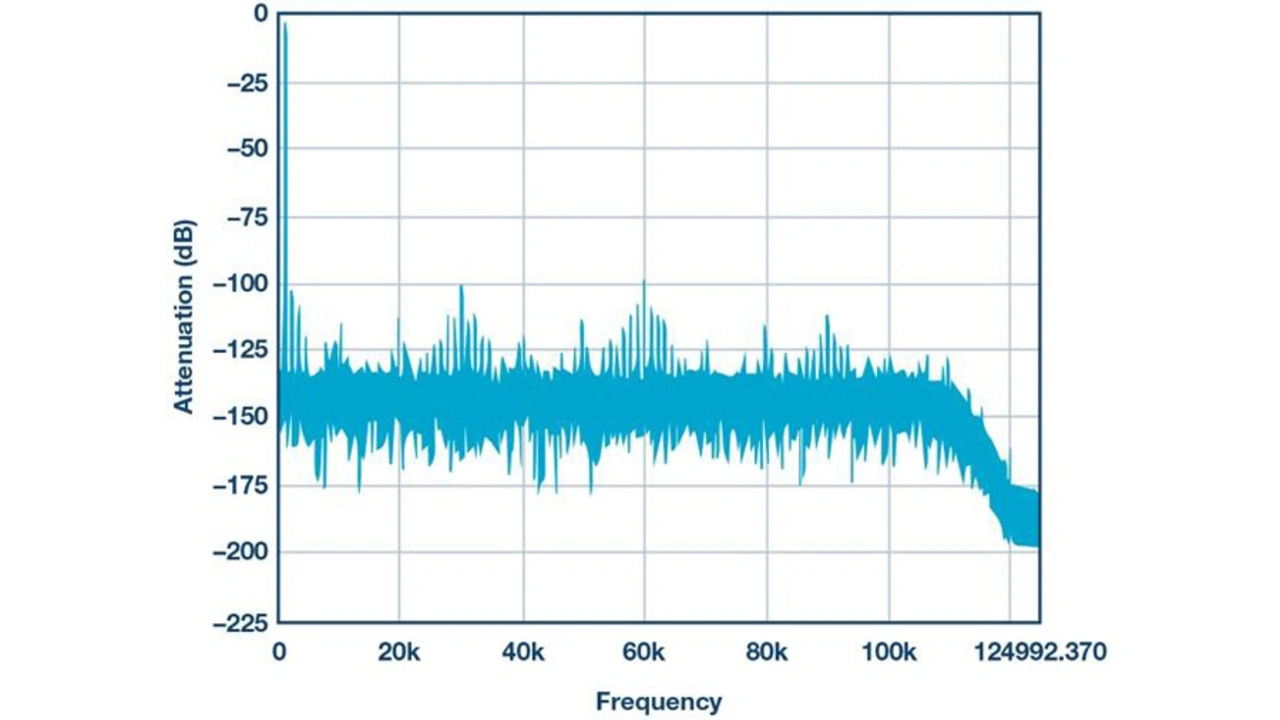

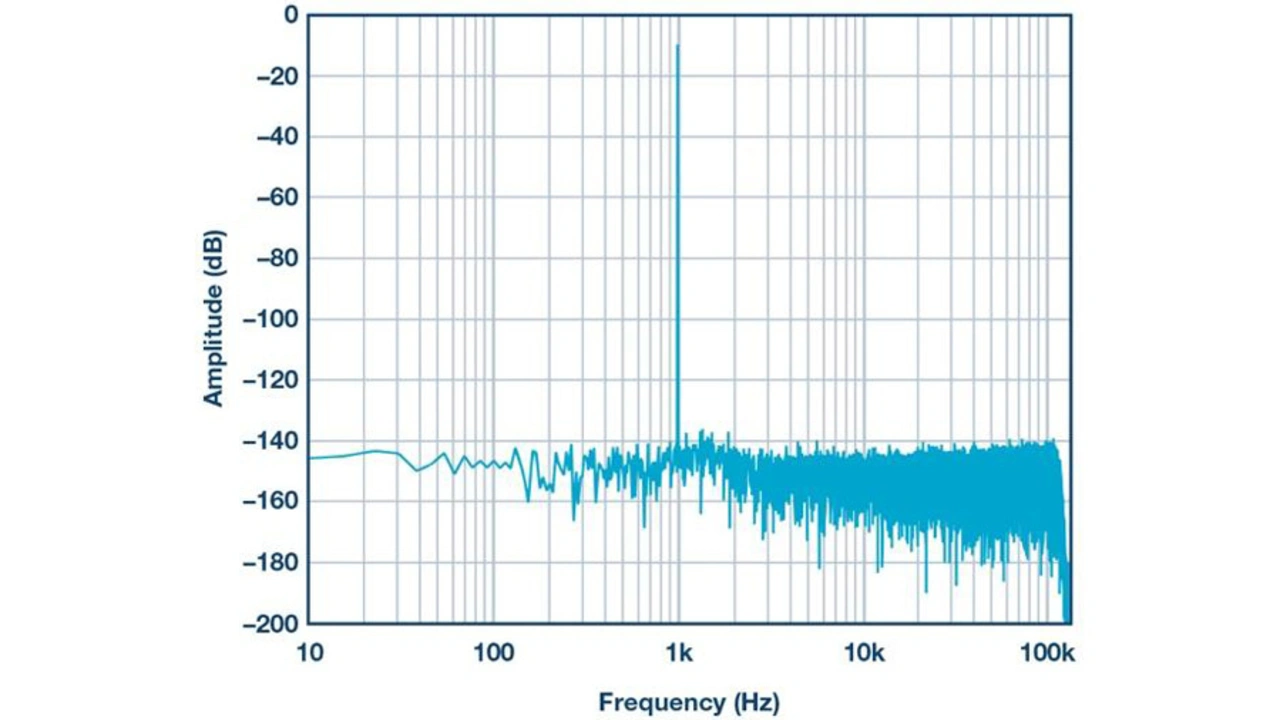

In Bild 6 ist eine Vielzahl an Takt-Perioden markiert, die entweder SFDR stören oder zu Jitter beitragen können. Wenn die SPI-Kommunikation nicht mit dem MCLK frequenzmäßig gekoppelt ist, können Störanteile auftreten.

Das Beherrschen von geeigneten Layout-Techniken ist das größte Kapital zur Minderung dieses Problems. Hochfrequente Signale präsentieren sich selbst als abgeschwächte Störer, aber auch als Überlagerungsfrequenzen und Intermodulationsprodukte. Läuft die SPI z.B. bei 16,01 MHz und der MCLK liegt bei 16 MHz, sind Störspitzen bei der Differenzfrequenz von 10 kHz zu erwarten.

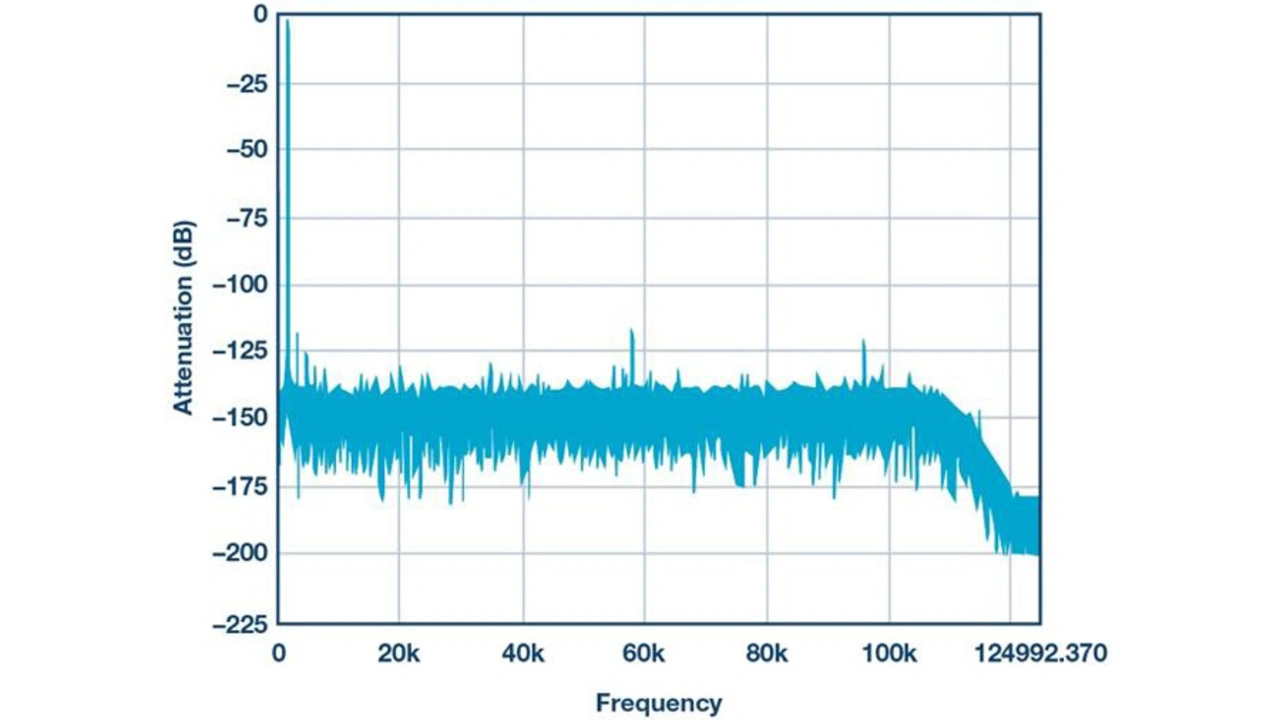

Neben einem guten Leiterplattenlayout ist ein weiterer Weg Störungen zu reduzieren, diese aus dem interessierenden Frequenzband heraus zu schieben. Können MCLK und SPI frequenzmäßig miteinander gekoppelt werden, lassen sich viele Störungen vermieden. Aber auch dann gibt es noch das Problem, der inaktiven Perioden (Idle) bei SPI, die immer noch Störungen verursachen können. Schnittstelleneigenschaften lassen sich aber auch zum Vorteil nutzen.

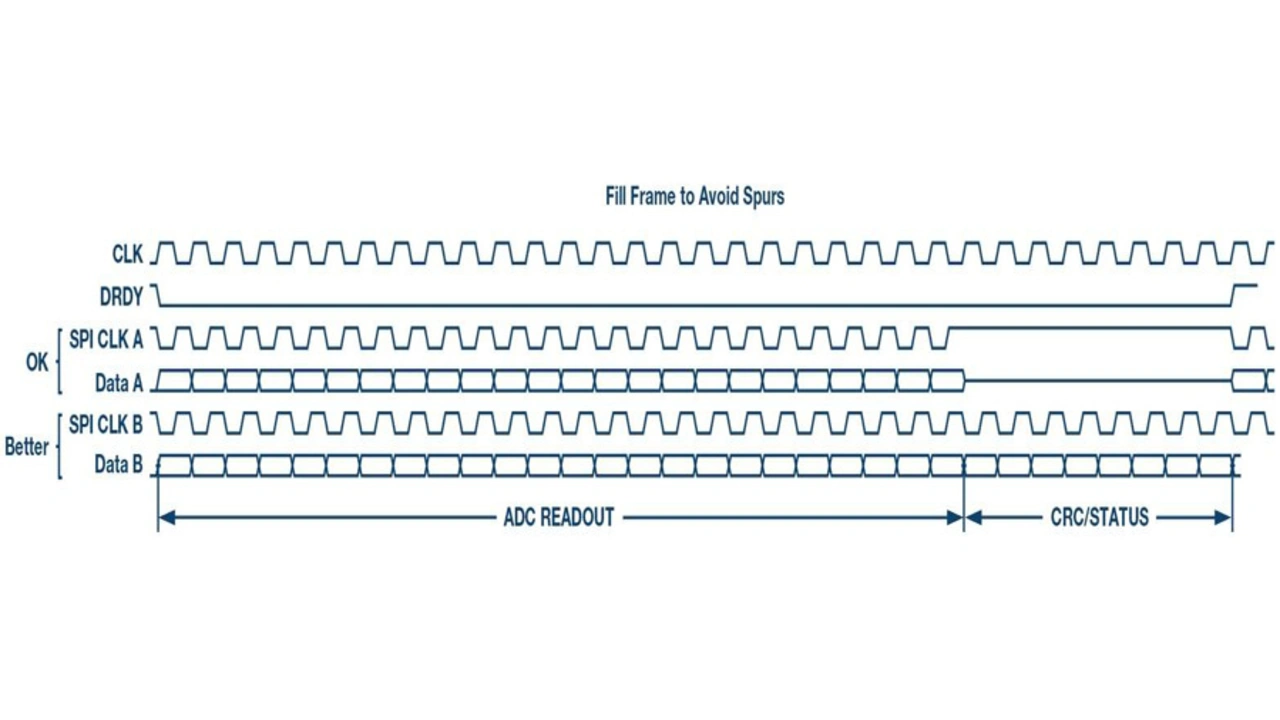

Beispielsweise können AD-Umsetzer Zustands-Bytes oder CRCs (cyclic redudancy check) liefern. Dies kann eine gute Möglichkeit sein, Störungen mit dem zusätzlichen Vorteil dieser Funktionen zu unterdrücken. Leerlauftakte – und selbst unbenutzte CRC-Bytes – können vorteilhaft sein, um Datenrahmen gleichmäßig aufzufüllen (Bild 9).

Entwickler können entscheiden, diese CRCs außer Acht zu lassen und trotzdem den Vorteil zu nutzen, sie zu aktivieren. Natürlich bedeutet dies eine zusätzliche Leistungsaufnahme über die Versorgungsleitungen auf digitalen Leitungen.

2018 brachte Analog Devices den AD7768-1 auf den Markt, einen sehr genauen AD-Umsetzer mit einem Offset unter 100 µV und flachem Frequenzgang bis zu 100 kHz.

Er wurde erfolgreich in Systeme mit einem SFDR von über 140 dB integriert, in denen Jitter im vollständigen Eingangsspannungsbereich oberhalb der Audiobänder erwiesenermaßen vernachlässigbar ist. Er hat einen internen RC-Generator, der die Referenzpunkte liefert, um verteilte Taktquellen zu prüfen.

Obwohl er keinen geringen Jitter hat, kann dieser interne RC-Generator Differenzierungsmethoden bieten, um Störquellen aufzudecken. Dieser AD-Umsetzer enthält interne Filter mit geschalteten Kondensatoren, nutzt aber auch Taktteiler, um den Antialiasing-Filter zu entlasten.

Der interne Taktteiler sichert eine gleichbleibende Leistungsfähigkeit auch beim Betrieb mit verzerrten Taktsignalen, die im Allgemeinen über Koppler empfangen werden. Die Positionen der Stromversorgung mit kurzen internen Bonddrähten, sind ideal für das Begrenzen externer ESR/ESL-Effekte. Die Glitch-Unterdrückung ist in den Takteingangs-Pads implementiert.

Messungen mit dem AD7768-1 in verschiedenen Applikationen zeigen einen Jitter von durchschnittlich 30 ps, was für das breite Spektrum an Anwendungen ausreichend sein sollte. Wenn die Aufgabe lautet, mit einem SDFR von besser 140 dB zu messen, kann der AD7768-1 am schnellsten zum Ziel führen – und er kann diese Messung bei einem Bruchteil des Leistungsbedarfs durchführen, der bisher bei herkömmlichen Stromversorgungspegeln nötig war.

Literatur

[1] Czapor, P.: Taktgenerierung für Sigma-Deslta-ADUs: Mehr als nur Jitter. Elektronik, 2019, H. 13, S. 36–41.

Der Autor

Pawel Czapor, M. Eng.

kam 2007 als Testingenieur für Präzisions-ADUs zu Analog Devices und arbeitet derzeit in der High Precision Converters Design Group in Limerick, Irland. Czapor studierte an der Technischen Universität Breslau, Polen, Elektrotechnik und schloss sein Studium mit dem Master ab.

pawel.czapor@analog.com

- Praktische Tipps gegen Taktjitter für Sigma-Delta-ADUs

- Übersprechen aus anderen Signalquellen

- Übersicht der Bilder